PCF8563:低功耗实时时钟芯片技术规格

需积分: 13 149 浏览量

更新于2024-07-14

收藏 216KB PDF 举报

"PCF8563是一款低功耗实时时钟/日历芯片,具有I2C总线接口和多种功能,适用于移动电话、便携式仪器、传真机和电池供电设备等应用。"

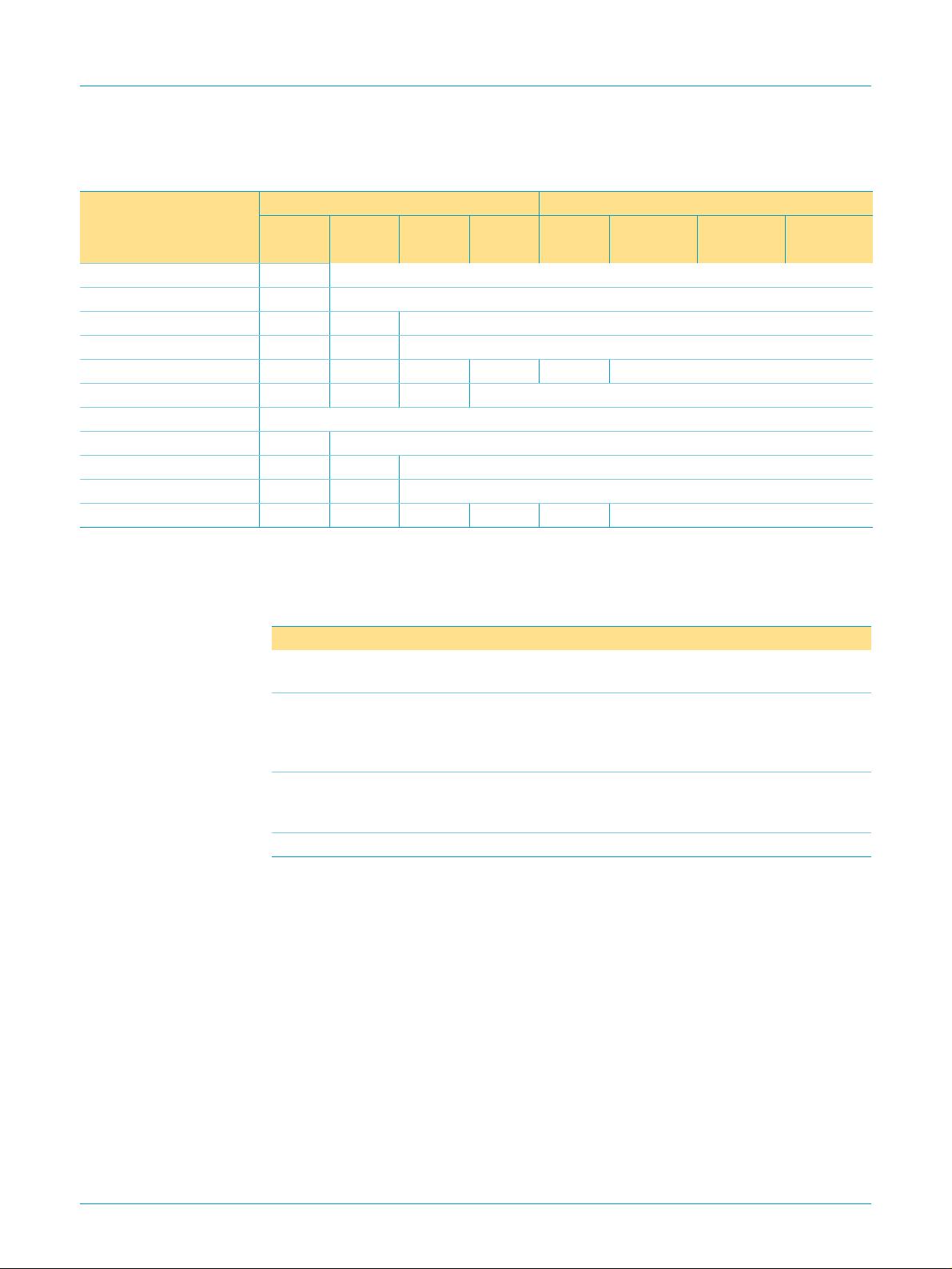

PCF8563是荷兰飞利浦(现NXP半导体)公司设计的一款CMOS实时时钟/日历(RTC)芯片,特别针对低功耗应用进行了优化。该芯片能够提供完整的日期和时间功能,包括年、月、日、星期、小时、分钟和秒,并且基于32.768kHz的石英晶体工作,确保了时间的精确性。此外,它还具有世纪标志位,可以处理闰年问题。

在电源特性方面,PCF8563的工作电压范围广泛,可以从1.0V到5.5V,这使得它能在各种电源条件下稳定运行。在VDD=3.0V和环境温度为25°C时,待机状态下典型电流仅为0.25µA,极大地降低了能源消耗,非常适合电池供电的设备。

PCF8563支持400kbps的I2C两线双向总线接口,该接口在1.8V至5.5V的电压范围内可以运行,简化了与微控制器或其他系统组件的连接。用户可以通过I2C总线设置和读取时钟数据,内部的字地址寄存器会在每次读写操作后自动递增。

该芯片还配备了一个可编程的时钟输出,可以为外部设备提供32.768kHz、1024Hz、32Hz和1Hz四种频率选择,满足不同应用场景的需求。此外,PCF8563还具有闹钟和定时器功能,可用于定时唤醒或其他时间触发的任务。电压低检测器能够在电源电压低于设定阈值时提供报警,确保系统的可靠运行。

PCF8563还有一个开漏中断引脚,当发生特定事件(如闹钟或定时器触发)时,可以向主机系统发送中断信号。该芯片的I2C总线从设备地址为读取时的A3H和写入时的A2H。最后,PCF8563集成了振荡器电容,减少了外部组件的需求,并且包含内部上电复位功能,以确保在电源恢复时的正确初始化。

PCF8563因其低功耗、高精度和丰富的功能集,成为移动通信、便携式电子设备、办公自动化设备等领域理想的实时时钟解决方案。配合提供的源码,开发者可以轻松地将其集成到自己的系统设计中,实现高效的时间管理。

113 浏览量

208 浏览量

点击了解资源详情

104 浏览量

382 浏览量

2010-09-15 上传

2021-07-26 上传

1511 浏览量

2021-07-26 上传

Corey_Wong

- 粉丝: 0

最新资源

- 开源数据库表自动修复工具发布

- MySQL Connector/Net 6.10.6: .NET 驱动程序的发布与更新

- C++实现Modbus-RTU通信测试程序源码解析

- 免费绿色版大地正反算软件v1.0发布

- Java贪吃蛇游戏设计与实现

- MFC实现的SMTP服务器端源码解析

- Exchange资源预约自动化工具AutoAccept Sink开源介绍

- IDL语言实现HJ-1卫星影像大气校正教程

- React待办事项应用:功能更新与设计缺陷修复指南

- STM32智能手环研发资料包

- CXF框架下WebService全套实现代码及加密实例解析

- 深入解析Ext3.0动态图表开发

- Asmodat Brute Mouse & Keyboard Logger:免费开源记录工具

- 自学视频刻录源代码完整教程

- PhoenixSuitPacket:一站式刷机解决方案

- vc++源码包大合集:涵盖界面、加密、通讯等技术