Verilog HDL入门:硬件描述语言的基石

需积分: 9 9 浏览量

更新于2024-07-18

收藏 1.48MB PPT 举报

Verilog HDL语言的学习指南深入探讨了硬件描述语言在现代电路设计中的重要性。Verilog HDL,作为一门硬件设计语言,旨在以文本形式描述和设计复杂的电路系统,它在硬件设计人员与电子设计自动化(EDA)工具之间起到了关键的桥梁作用。学习Verilog HDL的内容主要包括以下几个方面:

1. **综述**:

- 定义:硬件描述语言如Verilog,用于编写设计文件、构建行为级仿真模型,自动生成电路逻辑网表,并能在CPLD和FPGA等器件中实现设计。

2. **使用原因**:

- 面对大规模和高复杂度的电路设计需求,HDL提供了一个有效的解决方案。

- 在电子领域竞争加剧的背景下,HDL便于快速调试,避免频繁修改电路原理图。

- 它具有易读性和维护性,以及丰富的仿真、综合和布局布线工具支持。

3. **与C语言对比**:

- Verilog HDL继承了C语言的结构特性,但使用模块(module)代替函数,模块间通过端口变量调用而非函数名。

- C语言有主函数,而Verilog HDL强调模块的并行执行,顶层模块负责整合I/O信号。

4. **设计方法**:

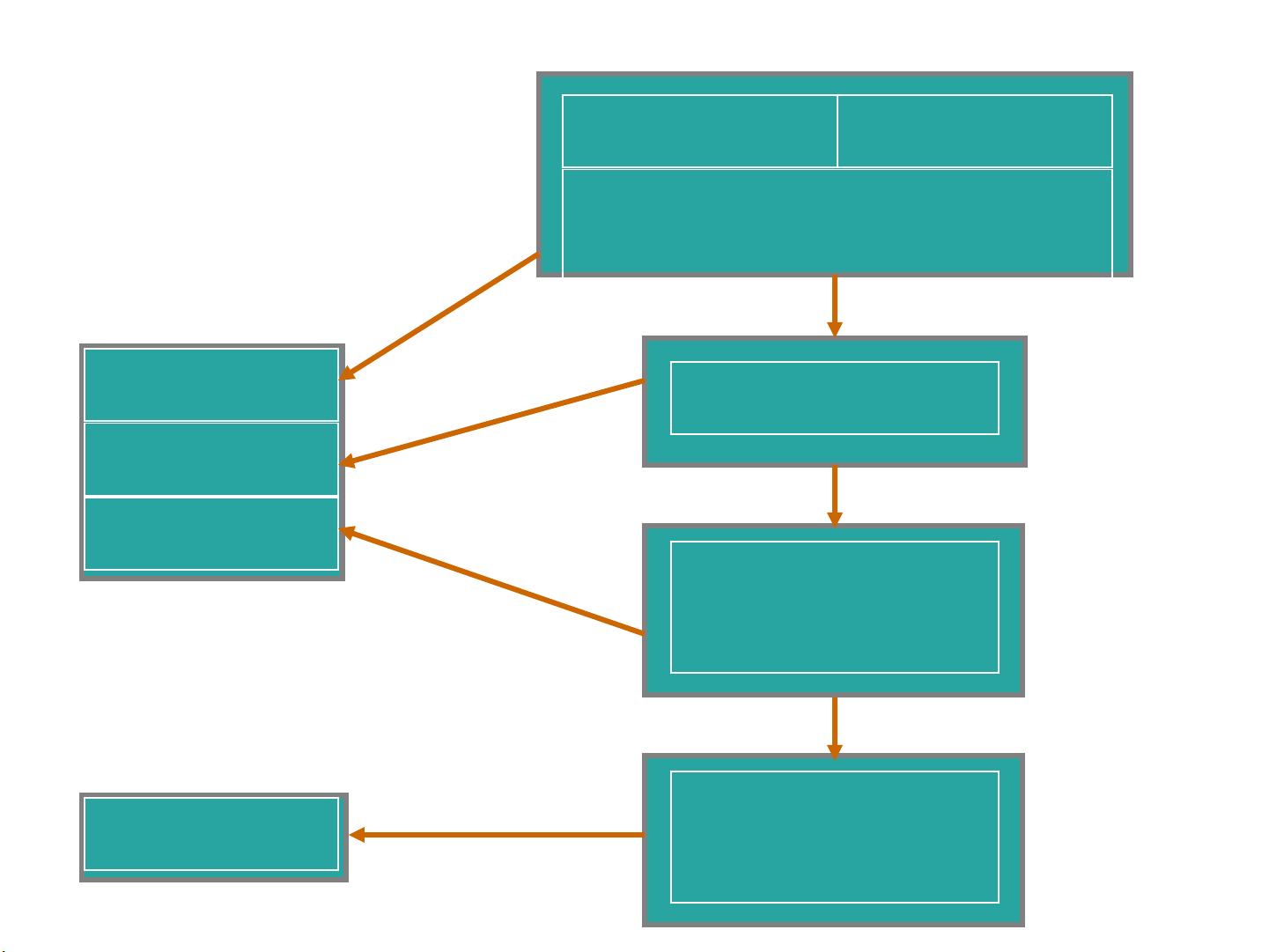

- 底层向上(BottomUp)设计:从基本门开始,逐步构建组合逻辑和时序逻辑模块,再到功能模块和系统集成。

- 上层向下(TopDown)设计:从系统需求出发,分解为模块,然后逐步细化至具体实现。

5. **传统设计方法与Verilog的差异**:

- 传统电路设计从状态图和逻辑表达式开始,采用特定元器件,而在Verilog中,设计可以在早期阶段进行,并通过仿真测试不断迭代。

通过学习Verilog HDL,设计师可以提升设计效率,减少设计错误,同时保持代码的可读性和可维护性,这对于现代电子系统开发至关重要。通过PPT的形式呈现,使得重点更加突出,便于理解和记忆。

2018-12-02 上传

2021-10-02 上传

2021-08-09 上传

2021-08-09 上传

2021-08-09 上传

2021-08-09 上传

2021-08-09 上传

jiangxiaoweiwei9

- 粉丝: 0

- 资源: 3

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析