使用TimingDesigner优化FPGA设计中的时序管理

165 浏览量

更新于2024-08-30

收藏 267KB PDF 举报

"EDA/PLD中的如何有效地管理FPGA设计中的时序问题"

在现代电子设计领域,FPGA(Field-Programmable Gate Array)因其灵活性和高性能而被广泛应用于各种复杂的系统。然而,随着速度的提升,时序管理成为了一个关键挑战。时序问题可能导致系统性能下降,甚至无法正确工作。【标题】和【描述】中提到的"EDA/PLD中的如何有效地管理FPGA设计中的时序问题",着重于如何在设计初期通过工具如TimingDesigner来识别和解决这些问题。

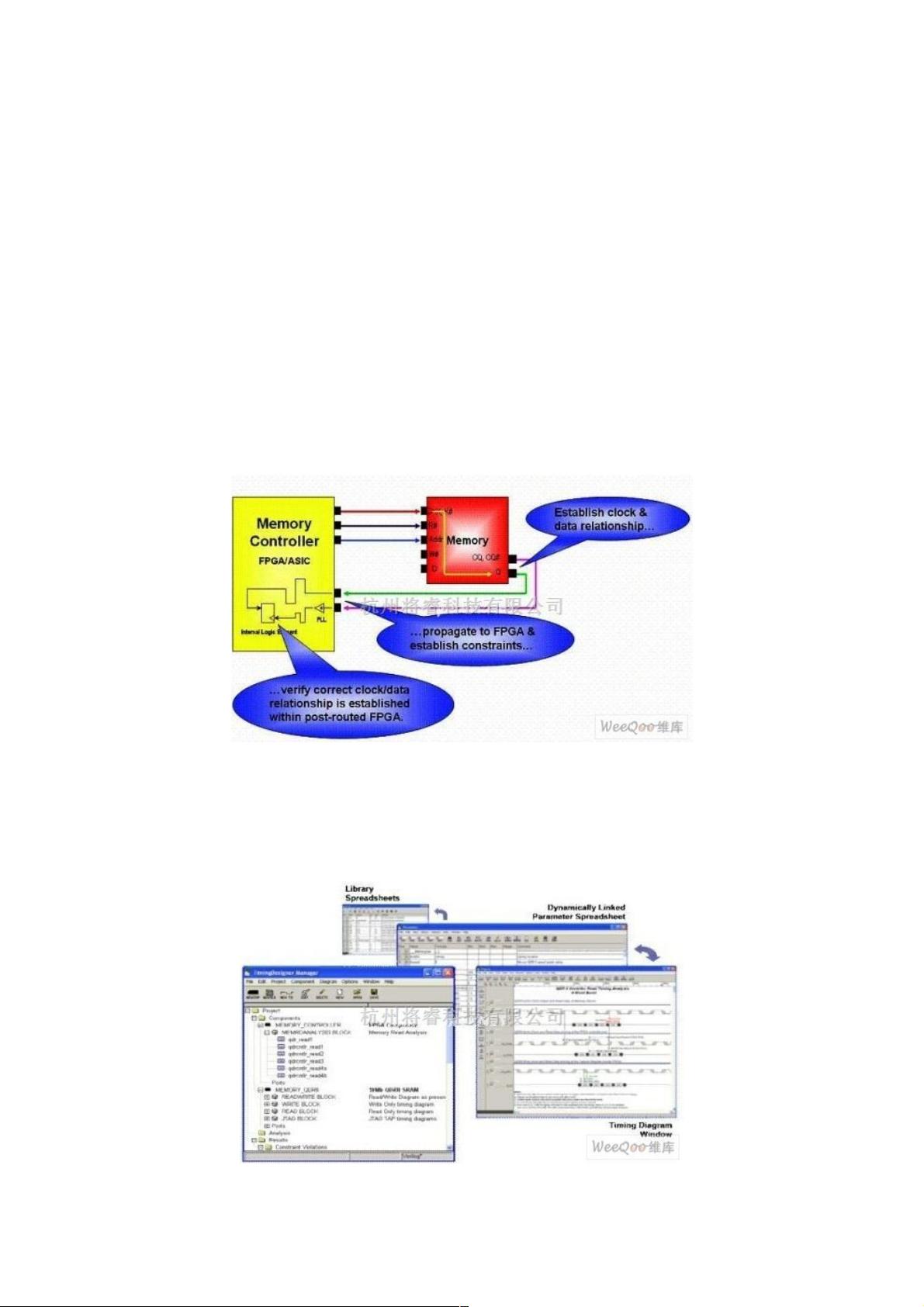

TimingDesigner是美国EMA公司提供的一款设计自动化工具,它特别针对时序分析和管理。该工具允许设计者在设计流程的早期阶段就进行时序评估,这至关重要,因为早发现问题意味着能更早地修复,进而避免后期修改的困难和时间浪费。通过创建交互式的时序图,设计者可以清晰地了解接口规范,分析组件间时序关系,并有效地在团队内部沟通设计需求。

在高速接口设计,特别是当涉及DDR或QDR存储器接口时,时序分析变得尤为重要。DDR内存能够以两倍于时钟频率的速度传输数据,而QDR则能以四倍速度进行,这就对时序控制提出了极高要求。设计者需要精确地控制时钟偏移,以确保数据在正确的时钟沿被捕获和驱动,同时考虑到信号完整性和噪声的影响。例如,过快的信号边缘可能会导致信号反射和串扰,影响数据的正确传输,需要通过适当的时序空余来保证数据的可靠性。

TimingDesigner提供了强大的功能来处理这些问题。它能帮助设计者分析DDR接口中必需的时钟偏移,以及数据采样时刻的时序余量,这对于保持数据眼图的稳定至关重要。通过这些工具,设计者可以精细调整时序约束,确保在高频率下数据的准确传输,避免出现数据丢失或错误。

此外,FPGA中的PLL(Phase-Locked Loop)网络对于实现精确的时钟控制起到了关键作用。PLL能够生成多个时钟域,以满足不同部分的需求,同时还能补偿由于工艺、电压和温度变化(PVT条件)引起的时钟延迟差异。在DDR设计中,PLL的配置和优化是保证时序正确性的核心步骤之一。

有效地管理FPGA设计中的时序问题,需要设计者深入理解高速接口的特性,结合强大的EDA工具如TimingDesigner,进行细致的时序分析和规划。通过这些方法,设计者可以确保其设计在高速运行条件下仍然稳定可靠,满足市场需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-12-05 上传

2020-10-21 上传

2020-12-09 上传

2020-12-09 上传

2020-11-10 上传

2020-11-20 上传

weixin_38617451

- 粉丝: 4

- 资源: 903

最新资源

- sugar-docs:贡献者和开发者的文档

- 基于PHP的支持同时上传多个文件的类源码.zip

- Smart Dictionary Lookup-crx插件

- 斑马打印机,Java调用官方API架包及调用样例

- 《ORANGE’S:一个操作系统的实现》读书笔记(三十二)文件系统(七)文章代码

- CSS3鼠标悬停下拉显示二维码特效代码

- GARPP:采用遗传算法的机器人路径规划

- school-web-3

- Python库 | sectool-0.0.8-py3-none-any.whl

- 实现IOS倒计时按钮

- hexo-deployer-cos-cdn:Hexo部署插件,支持将静态博客发布到腾讯云对象存储中,并同步刷新被更新文件的CDN缓存

- goshaplot:干净方便地将测量结果绘制成多个图形并将其组织在屏幕上。-matlab开发

- Flutter跨平台openai对话聊天交互APP

- protospace-34016

- jquery自动适应页面宽度的导航菜单下载特效代码

- 基于PHP的支持Ajax星星投票的PHP无刷新评论程序源码.zip