HI3516DV500DMEB芯片的DV500原理图设计与配置

需积分: 5 10 浏览量

更新于2024-08-03

收藏 384KB PDF 举报

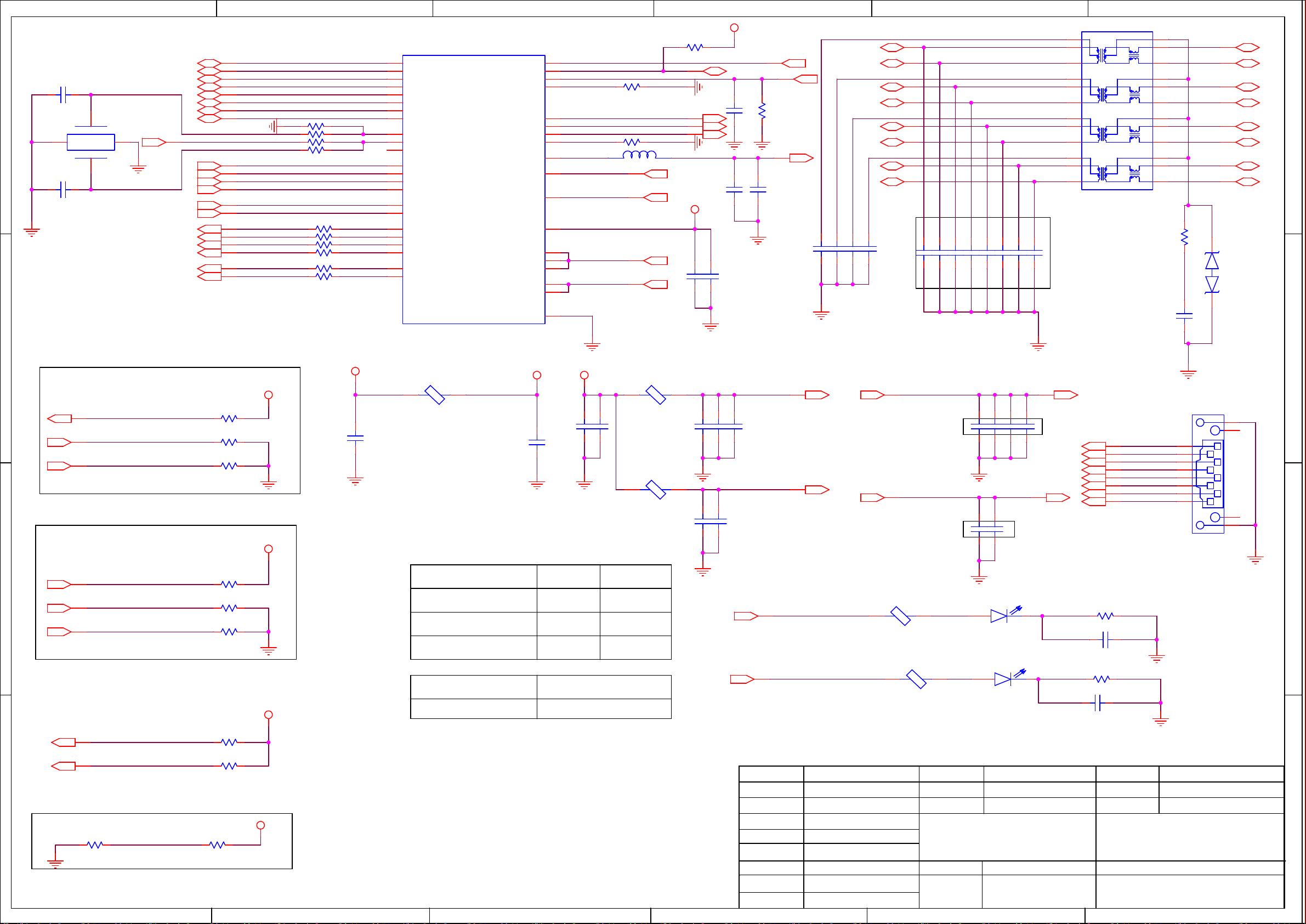

HI3516DV500DMEB-VER-C-SCH中DV500原理图

HI3516DV500DMEB-VER-C-SCH中DV500原理图是Hi3516DV500系列芯片的原理图设计,主要涉及到PHY Address配置、RGMII0 Voltage配置、 External Source配置、ETH配置、闭塞PIN配置、Internal 1.8V电压配置等方面。

1. Pull-up disable PLL @ ALDPS mode:在ALDPS模式下,PLL的上拉电阻disable, PLL是锁相环路的缩写,主要用于时钟信号的同步和稳定。

2. TXDLY=1 Add 2ns delay to TXC for TXD latching:在TXD latch时增加2ns的延迟,以确保数据的正确传输。

3. Enable/Disable PLL @ ALDPS:在ALDPS模式下,PLL的使能和禁用控制,PLL的使能可以确保时钟信号的稳定,而禁用可以减少功耗。

4. Reserve capacitance For EMI:为EMI(Electromagnetic Interference,电磁干扰)预留电容,以减少设备对周围环境的干扰。

5. 100M active & link、1000M active & link:分别表示100Mbps和1000Mbps的以太网连接,active表示连接状态,link表示链路状态。

6. PHY Address Config.:PHY Address是PHY层面的地址配置,用于确定PHY层面的身份和地址。

7. RGMII0 Voltage Config.:RGMII0的电压配置,用于确定RGMII0的工作电压。

8. External Source:外部信号源,用于提供时钟信号和其他信号。

9. ETH_close to PIN21、close to PIN3、PIN8、PIN38:ETH(以太网)接口闭塞到PIN21、PIN3、PIN8、PIN38,用于确定ETH接口的引脚连接。

10. Internal 1.8V:内部1.8V电压,用于芯片内部的电压供应。

11. 1'b0、2'b10、CFG_EXT、CFG_LDO[1:0]:分别表示一位、二进制十进制数字和配置寄存器的值。

12. External 3.3V (default):外部3.3V电压,默认电压供应。

13. RGMII0TXC/RXC Delay Config.:RGMII0的时钟延迟配置,用于确定RGMII0的时钟信号延迟。

14. RGMII0 Power Source:RGMII0的电源配置,用于确定RGMII0的电源供应。

15. PHYAD[2:0]:PHY地址寄存器,用于确定PHY层面的地址。

16. RXDLY=1 Add 2ns delay to RXC for RXD latching:在RXD latch时增加2ns的延迟,以确保数据的正确传输。

17. 位号:7200:表示芯片的位号为7200。

18. 3V3_PER、DVDD_ETHIO:分别表示3.3V电压和以太网IO电压供应。

19. REVIEWED、DESIGNED、VER、PART_NUMBER:分别表示审核、设计、版本号和零件号。

20. DATE、ECANO、SHEET、OF、C:分别表示日期、ECANO(环境可靠性测试)、SHEET(元件表)和版面设计信息。

HI3516DV500DMEB-VER-C-SCH中DV500原理图涉及到PHY Address配置、RGMII0 Voltage配置、External Source配置、ETH配置、闭塞PIN配置、Internal 1.8V电压配置等方面,旨在提供一个完整的芯片设计方案。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-03-18 上传

2023-03-10 上传

2023-11-15 上传

2023-06-13 上传

2023-06-13 上传

胡子wang

- 粉丝: 0

- 资源: 8

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率