ASIC设计流程与逻辑综合详解

需积分: 31 148 浏览量

更新于2024-07-29

收藏 950KB PDF 举报

"DC中文教程主要讲解了ASIC设计流程、逻辑综合的概念以及Synopsys Design Compiler的使用,涉及Synopsys技术库、逻辑优化过程、布局布线接口、后布局优化和SDF文件的生成等内容。教程以一个具体的ASIC设计示例——tap控制器为例,阐述了从RTL验证到tapeout的全过程。"

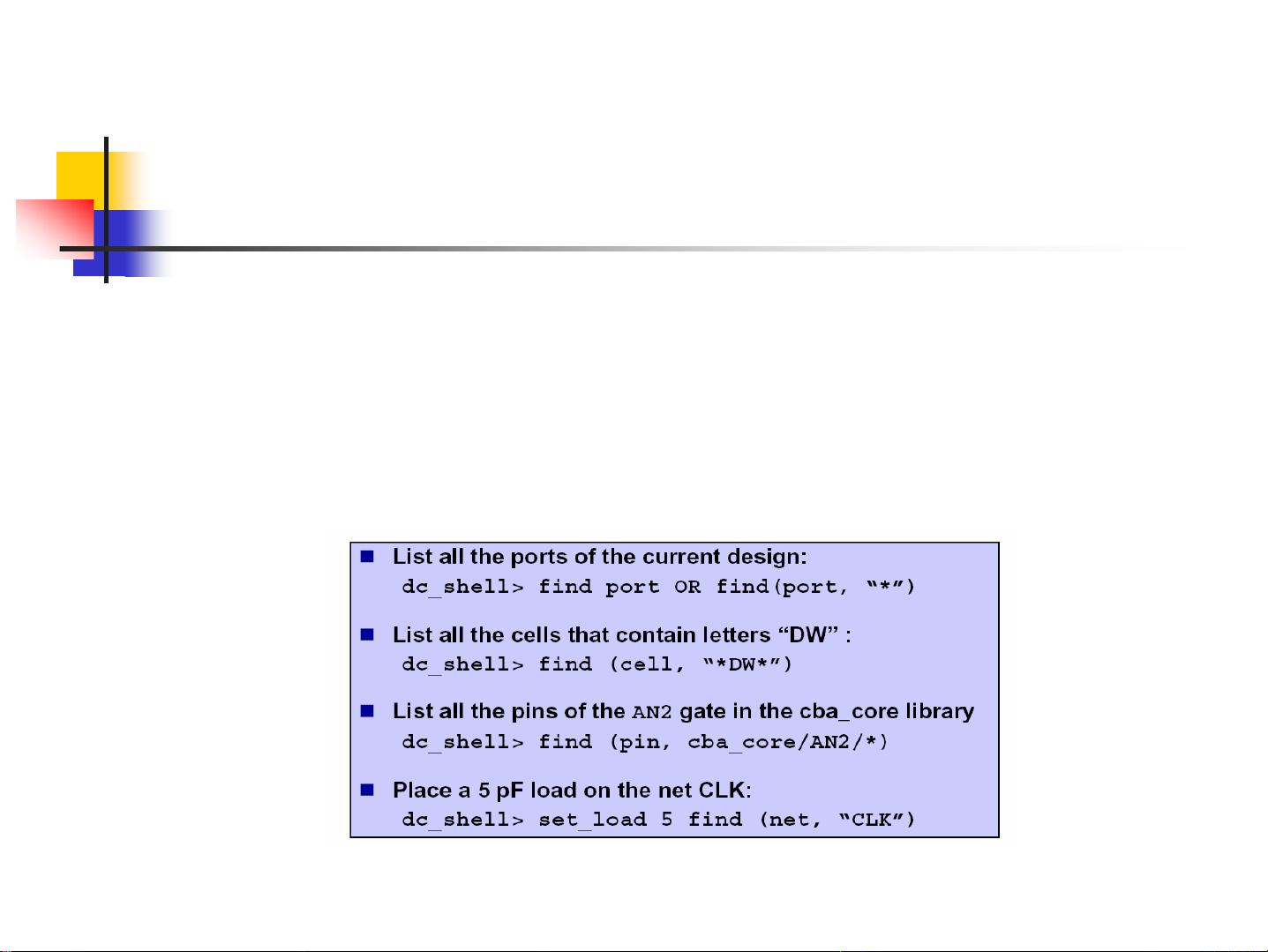

在ASIC设计中,逻辑综合是一个至关重要的步骤,它决定了设计电路中逻辑门的连接方式。逻辑综合的目标包括确定门级结构、平衡时序与面积、优化功耗与时序的关系以及提升电路的可测试性。这个过程由综合工具执行,首先通过分析硬件描述语言(HDL)代码,将其映射到技术库无关的GTECH模型,接着进行逻辑优化,最后将逻辑映射到目标单元库的特定细胞,生成综合后的网表。

ASIC设计流程通常包括多个阶段,从验证RTL设计、设定设计约束,到使用IP和库模型进行逻辑综合与扫描插入,再到静态时序分析、形式验证。接下来,经过布局、时钟树插入、全局路由,直至后全局路由的静态时序分析和细节路由。在这些步骤之后,会进行后布局优化(in-place optimization,IPO),并再次进行静态时序分析以确保满足时间约束。最终,当所有条件满足后,设计可以进入tapeout阶段。

以tap控制器为例,该设计包含了多个组件如Tap_controller.v、Tap_bypass.v、Tap_instruction.v和Tap_state.v等。在完成代码编写和功能仿真后,设计者还需要进行预布局、逻辑综合、使用PrimeTime进行静态时序分析,并生成SDF文件,以便后续的布局布线和优化。

在Synopsys Design Compiler中,用户可以利用其强大的逻辑优化功能,结合特定的技术库,实现高效的逻辑综合。Synopsys技术库包含了各种门级单元,这些单元在综合过程中会被选中以构建实际电路。同时,逻辑综合与布局的接口——LTL(Layout and Logic)是连接这两步的关键,确保了设计的时序性能。Post_layout optimization阶段,主要是针对布局布线后的电路进行进一步优化,以达到更好的性能指标。

DC中文教程详细介绍了ASIC设计的核心技术和流程,对于理解数字集成电路设计和掌握Synopsys工具的使用具有很高的参考价值。

2011-09-05 上传

108 浏览量

2007-08-28 上传

2012-11-04 上传

2022-06-04 上传

132 浏览量

yxj3179

- 粉丝: 5

- 资源: 24

最新资源

- Snorkel Ops Fortnite Wallpapers New Tab-crx插件

- periodic-table:交互式元素周期表

- 净重分类改进:已提出将NRI替代ROC曲线下的面积。-matlab开发

- ipRecorder:允许记录和播放IP中的数据。 适合调试

- juan-ted-api

- adapters

- 最实用的mvp框架

- 脉冲输出程序1.rar

- 用于求解延迟微分方程和进行局部搜索的图形用户界面:用于求解一组延迟微分方程 (DDE) 和局部搜索以获得最佳解决方案的图形用户界面-matlab开发

- SCORM-on-MEAN-stack

- flutter_myinsta

- velocitaiproject

- 基于PHP的最新的搜搜问问抓取php商业版(伪静态)源码.zip

- iSAX:提供 iSAX Java 实现

- 亨利简历

- Laptop-Template:在此模板中,仅使用HTML和CSS