基于Vivado的FIR滤波器设计与Altera Cyclone IV教程

需积分: 9 104 浏览量

更新于2024-09-09

收藏 1.87MB DOCX 举报

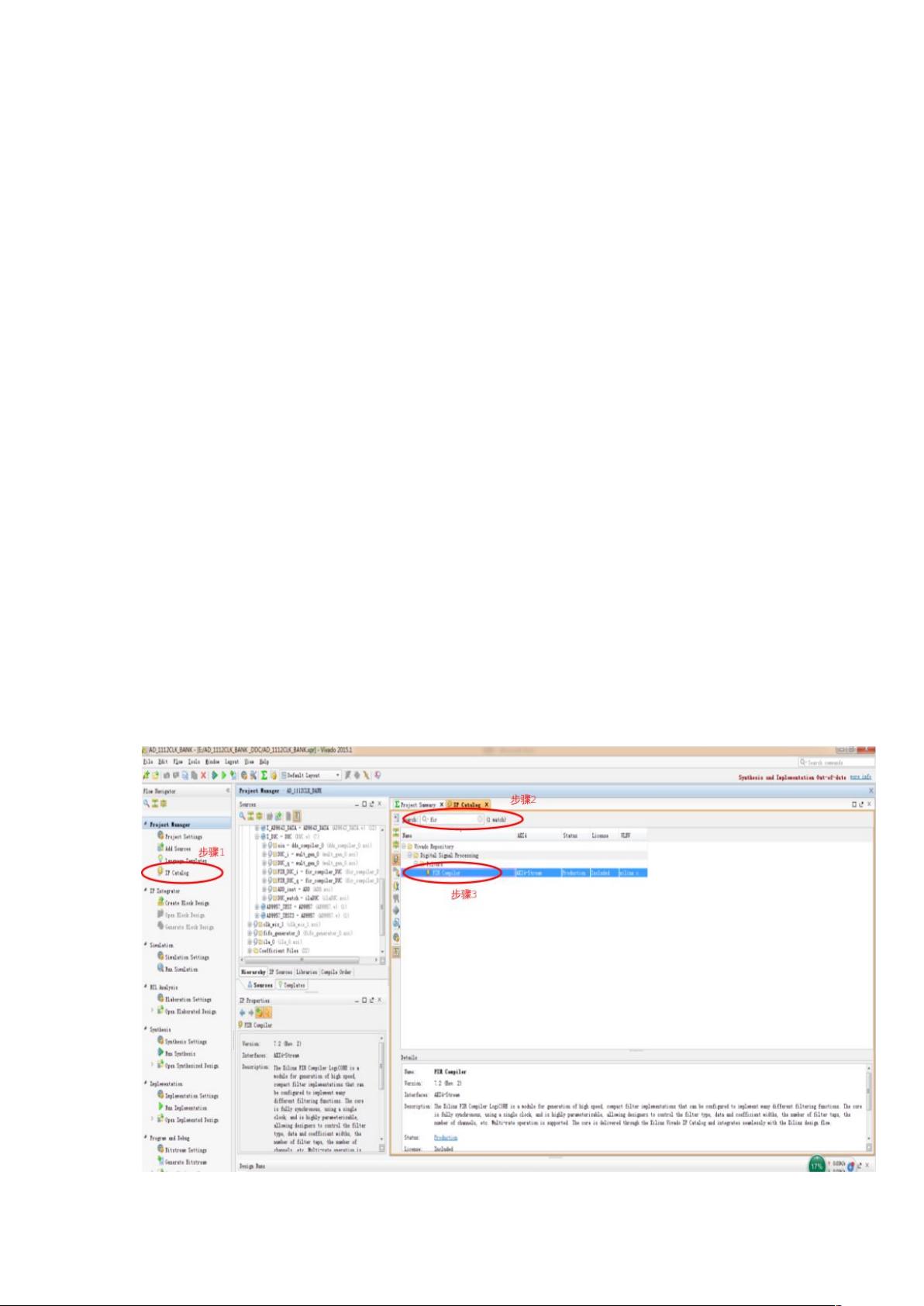

"该资源是一份关于使用Altera Cyclone IV FPGA进行滤波器设计的教程,特别适合软件开发新手。教程详细介绍了如何利用Vivado的IP核定制FIR滤波器,并结合MATLAB进行滤波器设计和系数量化。整个设计过程包括设置滤波器参数、导入MATLAB生成的系数文件以及配置IP核。"

在这个资源中,主要涉及了以下几个IT知识点:

1. **Altera Cyclone IV FPGA**: Altera Cyclone IV是Altera公司(现已被Intel收购)推出的一系列FPGA芯片,它具有低功耗、高性能和丰富的I/O资源等特点,常用于各种数字信号处理(DSP)、嵌入式系统和通信应用。

2. **Vivado IP核**: Vivado是Xilinx公司的集成开发环境,用于FPGA和SoC的设计。IP核是预先设计好的功能模块,可以快速方便地集成到用户的设计中。在本例中,FIRCompiler IP核被用来构建滤波器。

3. **FIR滤波器设计**: FIR(Finite Impulse Response)滤波器是一种线性相位数字滤波器,用于信号处理。设计FIR滤波器通常采用MATLAB等工具,本教程中使用的是基于窗函数法,选择了32阶滤波器,以实现低通滤波效果。

4. **MATLAB的fdatool**: fdatool是MATLAB中的信号处理工具箱,用于设计和分析数字滤波器。在这里,它被用来定制FIR滤波器的参数,如响应类型、设计方法、滤波器阶数和频率规格。

5. **FIR滤波器系数量化**: 由于实际硬件限制,滤波器的系数需要进行量化,即将浮点数转换为固定点数。这个过程中,需要选择适当的位宽以确保精度和效率。

6. **COE文件**: COE文件是一种Xilinx系数文件格式,包含了FIR滤波器的系数数据。这些系数可以在MATLAB中生成,并在Vivado中加载到FIR Compiler IP核中。

7. **IP核参数配置**: 在Vivado中,用户需要根据设计需求配置IP核的参数,例如采样时钟频率、滤波器系数位宽和输入数据位宽等。

通过以上步骤,开发者可以将设计的FIR滤波器实现到Altera Cyclone IV FPGA中,完成信号处理任务。这份教程对于理解和实践FPGA上的数字信号处理有极大的帮助,特别是对于初学者,提供了从理论设计到实际实现的完整流程。

1215 浏览量

1136 浏览量

252 浏览量

2024-02-10 上传

2024-02-29 上传

1302 浏览量

740 浏览量

407 浏览量

qq_19337531

- 粉丝: 0

- 资源: 2

最新资源

- apiAutocomNFSe

- ekrtf304_d7_delphi_rtf_3娱d7com_

- mysql-installer-community-8.0.22.0.msi.zip

- blomqvist:布隆奎斯特

- zsnap:Linux上用于ZFS的自动简单快照工具

- 记分卡:安全记分卡-开源的安全健康指标

- 用HTML5编写乐谱

- java项目实战练习小项目

- typed-manifest:对标准 Java META-INFMANIFEST.MF 的类型安全访问

- firefox-to-deepl:Firefox扩展。 突出显示网页上的文本并将其发送到DeepL

- 关于车辆到行人通信系统及其使用方法的介绍说明.rar

- 基于串口通信的上位机控制软件.rar

- Week5:网络编程

- t-angular-boilerplate-keycloak

- svelte-localstorage::warning:尚未就绪:warning:自动与localStorage同步的Svelte可写存储

- matlab个人练习上手视觉项目