高速差分ADC驱动器设计关键点解析

需积分: 9 5 浏览量

更新于2024-08-05

收藏 3.07MB PDF 举报

"高速差分ADC驱动器设计指南"

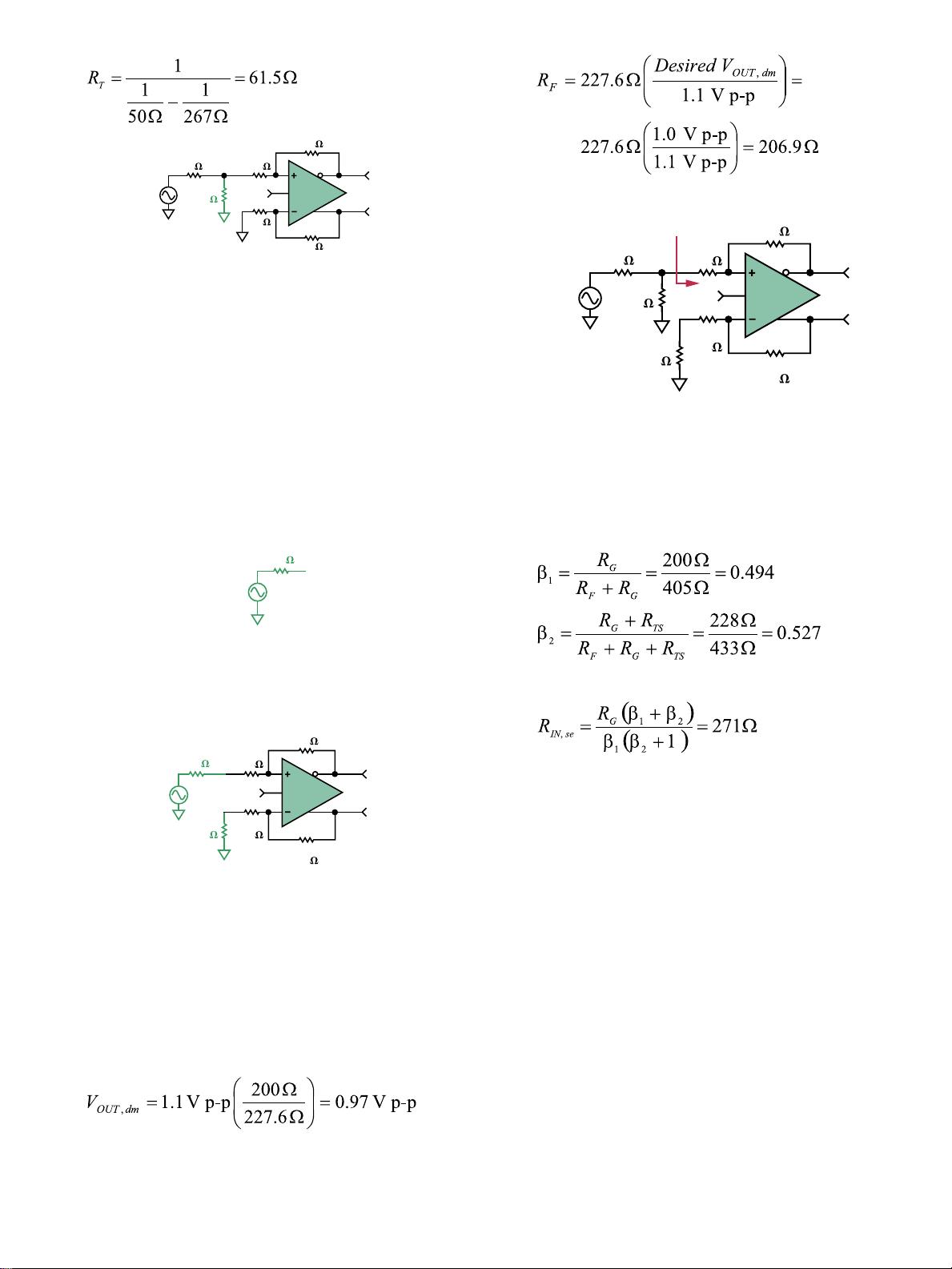

这篇由ADI公司提供的技术文章聚焦于高速差分ADC驱动器的设计,旨在解决在高速数据采集系统中遇到的挑战。高速差分ADC驱动器在抑制共模噪声和干扰方面起着关键作用,通过提供差分输入信号,能够显著提升系统的动态范围和整体性能。

差分输入型ADC通常优于单端输入,因为它们采用平衡信号处理,能将动态范围加倍。然而,要实现最佳性能,ADC需要特定的驱动器来生成差分信号。这些驱动器不仅提供信号放大,还能进行幅度调整、单端到差分转换、缓冲、共模偏置调整以及滤波等功能。

文中提及的AD8138是一款示例性的差分ADC驱动器,它具有两个输出端(VOP和VON)和一个共模输入端(VOCM)。VOCM允许灵活地控制输出共模电压,而差分输出信号在VOP和VON之间形成。负反馈确保放大器的两个输入端(VA+和VA-)电压接近相等。输入信号可以是平衡的差分信号,也可以是单端信号,但无论哪种形式,输入信号都被定义为VIP - VIN。

文章还引入了差模输入电压(VIN,dm)和共模输入电压(VIN,cm)的概念,这是理解驱动器性能和信号质量的重要参数。差模电压代表两个输入端之间的电压差,而共模电压则是两个输入端相对于公共参考电压的平均值。保持低共模电压有助于减少噪声对ADC性能的影响。

设计高速差分ADC驱动器时,需要考虑的关键因素包括信号带宽、驱动器的输出摆幅、共模抑制比(CMR)、上升时间、输出电流能力以及电源抑制比(PSRR)等。合适的驱动器应能适应ADC的输入要求,同时在噪声和干扰环境中保持信号完整性。

此外,匹配电路元件以减小信号失真、选择适当的电容和电阻来滤除噪声、以及考虑驱动器的输出阻抗与ADC输入阻抗的匹配都是设计过程中不容忽视的细节。在实际应用中,设计师可能需要根据具体系统需求进行多次迭代和优化,以确保驱动器和ADC之间的最佳配合。

高速差分ADC驱动器设计是一门复杂的艺术,需要深入理解信号处理原理、噪声抑制技术和ADC特性。通过正确选择和配置驱动器,可以实现高效、可靠的高速数据采集系统,从而提高整个系统的测量精度和稳定性。

237 浏览量

160 浏览量

275 浏览量

441 浏览量

282 浏览量

994 浏览量

136 浏览量

204 浏览量

2021-12-10 上传

yinguoyan1985

- 粉丝: 5

最新资源

- Verilog实现的Xilinx序列检测器设计教程

- 九度智能SEO优化软件新版发布,提升搜索引擎排名

- EssentialPIM Pro v11.0 便携修改版:全面个人信息管理与同步

- C#源代码的恶作剧外表答题器程序教程

- Weblogic集群配置与优化及常见问题解决方案

- Harvard Dataverse数据的Python Flask API教程

- DNS域名批量解析工具v1.31:功能提升与日志更新

- JavaScript前台表单验证技巧与实例解析

- FLAC二次开发实用论文资料汇总

- JavaScript项目开发实践:Front-Projeto-Final-PS-2019.2解析

- 76云保姆:迅雷云点播免费自动升级体验

- Android SQLite数据库增删改查操作详解

- HTML/CSS/JS基础模板:经典篮球学习项目

- 粒子群算法优化GARVER-6直流配网规划

- Windows版jemalloc内存分配器发布

- 实用强大QQ机器人,你值得拥有