CADENCE:集成电路设计的强大工具与流程概览

需积分: 9 13 浏览量

更新于2024-08-01

1

收藏 4MB PPT 举报

Cadence设计系统是一个广泛应用于集成电路设计的高级电子设计自动化(EDA)平台,它在集成电路设计流程中起着核心作用。随着半导体行业的不断发展,集成电路的设计复杂度持续提升,Cadence凭借其强大的功能和灵活性满足了日益增长的市场需求。

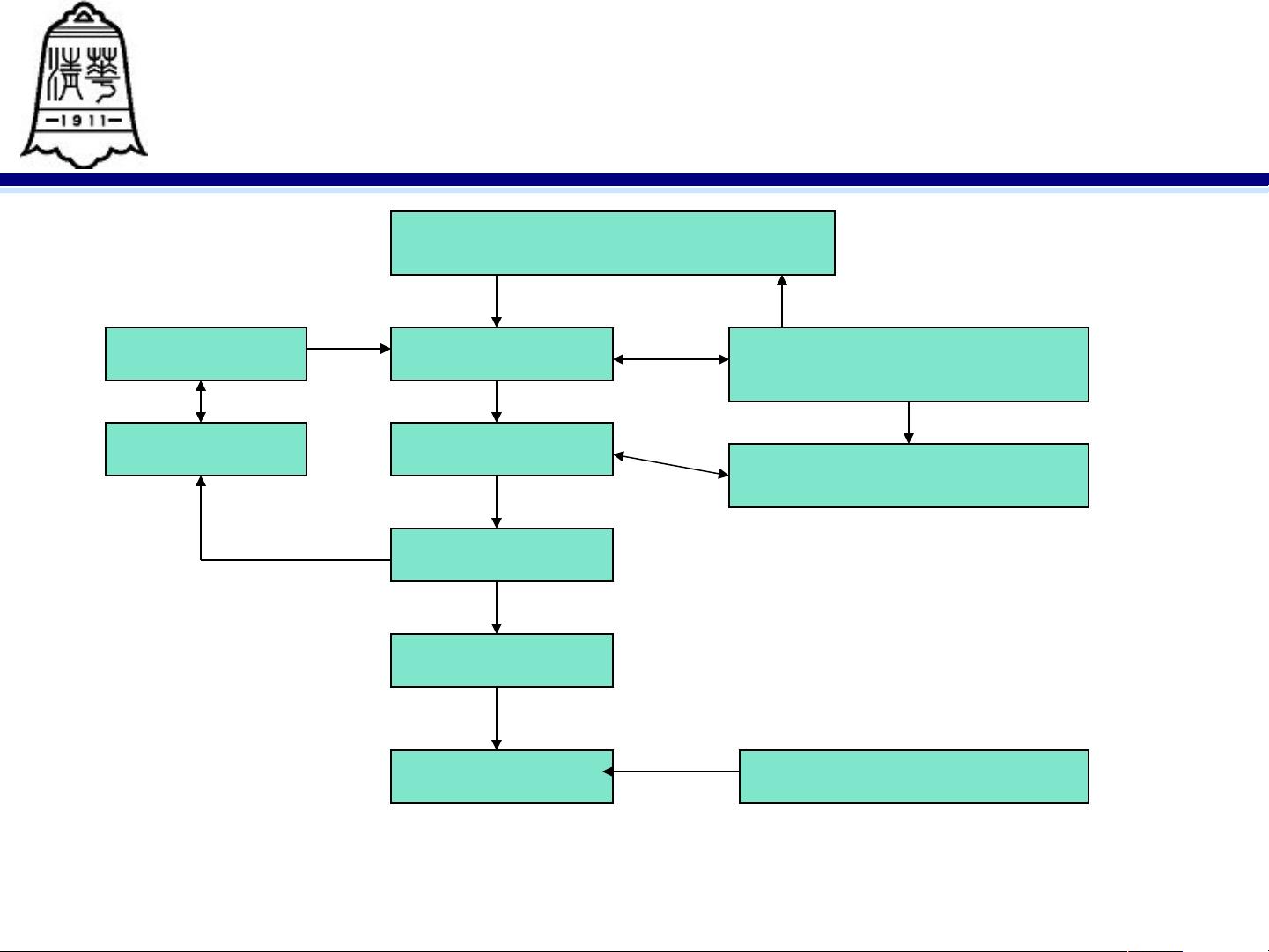

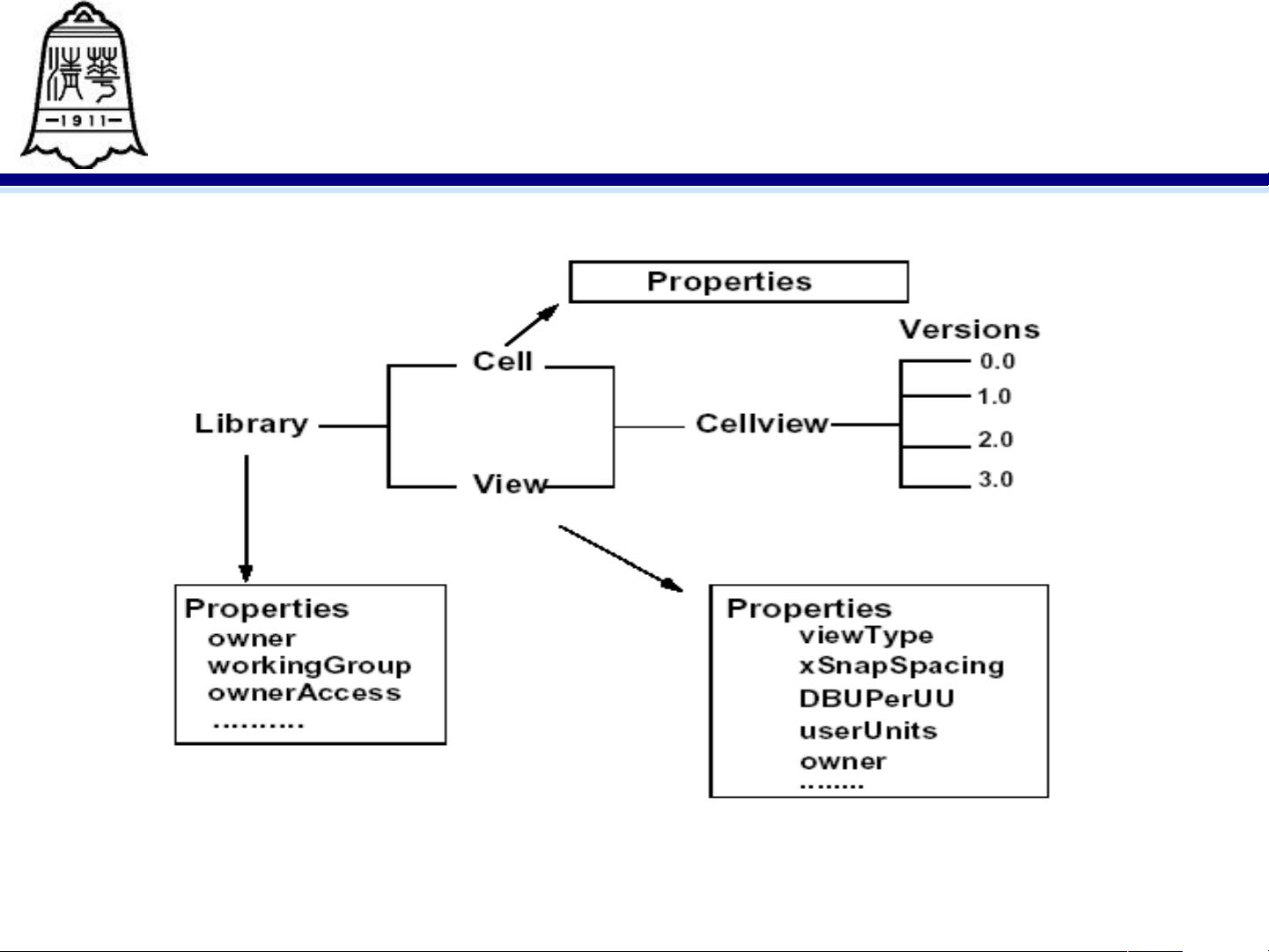

首先,Cadence系统概述部分介绍了Cadence的全貌,包括其在集成电路设计中的地位。设计流程涵盖了从概念阶段到实现阶段的多个步骤,如版图设计、验证和优化。其中,Virtuoso LE是一款版图设计工具,它提供了一个集成环境,用于创建、编辑和管理电路布局。Diva和Dracula是版图验证工具,分别用于电路功能验证和物理一致性检查。

学习Cadence的原因在于它能够支持从高级设计语言(如VHDL)的模型化,到仿真验证,再到逻辑综合和实施,整个设计链路。VHDL是一种结构化设计语言,通过VHDL仿真,设计师可以模拟电路的行为,确保设计的正确性和性能。行为综合将VHDL模型转化为硬件描述语言(HDL),逻辑综合则进一步将这些描述转化为实际的门级电路。同时,Cadence也强调了可测性设计和低功耗设计的重要性,以满足现代电子产品的高效率和易测试性要求。

系统组织结构清晰,包括系统启动、帮助文档等组成部分,使得用户能够快速上手并高效地进行设计工作。随着工艺技术的进步,如特征尺寸的减小和电源电压的降低,Cadence的功能也在不断更新,以适应不断变化的市场和技术趋势。

Cadence设计系统是集成电路行业中不可或缺的一部分,它通过提供一系列强大的工具和解决方案,帮助设计师应对设计复杂度的挑战,推动了整个行业的技术创新和效率提升。学习和掌握Cadence对于集成电路设计师来说,是一项至关重要的技能。

101 浏览量

124 浏览量

点击了解资源详情

367 浏览量

120 浏览量

geehow

- 粉丝: 1

- 资源: 7