Verilog HDL基础教程:模块与行为描述

"Verilog HDL硬件描述语言是电子设计自动化领域中的一种重要语言,用于描述数字系统的硬件逻辑。本书旨在手把手教导读者理解和运用Verilog HDL进行硬件设计。"

在Verilog HDL中,模块是核心的描述单元,它代表了硬件设计的一个功能单元或者结构,并通过外部端口与其他模块进行通信。模块可以描述从最基本的开关级到高级的抽象层次,如门级和自定义逻辑。模块的声明包括模块名称和端口列表,例如:

```verilog

module Module_Name (port_list);

// Declarations

reg, wire, parameter, input, output, inout,

function, task,

// Statements

initial statement,

always statement,

module instantiation,

gate instantiation,

UDP instantiation,

continuous assignment

endmodule

```

声明部分用于定义模块内部的各种元素,如寄存器(reg)、线网(wire)、参数(parameter)以及输入、输出和双向端口。语句部分则包含了设计的行为,如初始语句(initial statement)用于定义非时序行为,总是语句(always statement)用于描述时序逻辑,模块实例化(module instantiation)用于嵌套模块,门级实例化(gate instantiation)用于创建基本逻辑门,用户定义的进程(UDP instantiation)和连续赋值(continuous assignment)用于数据流操作。

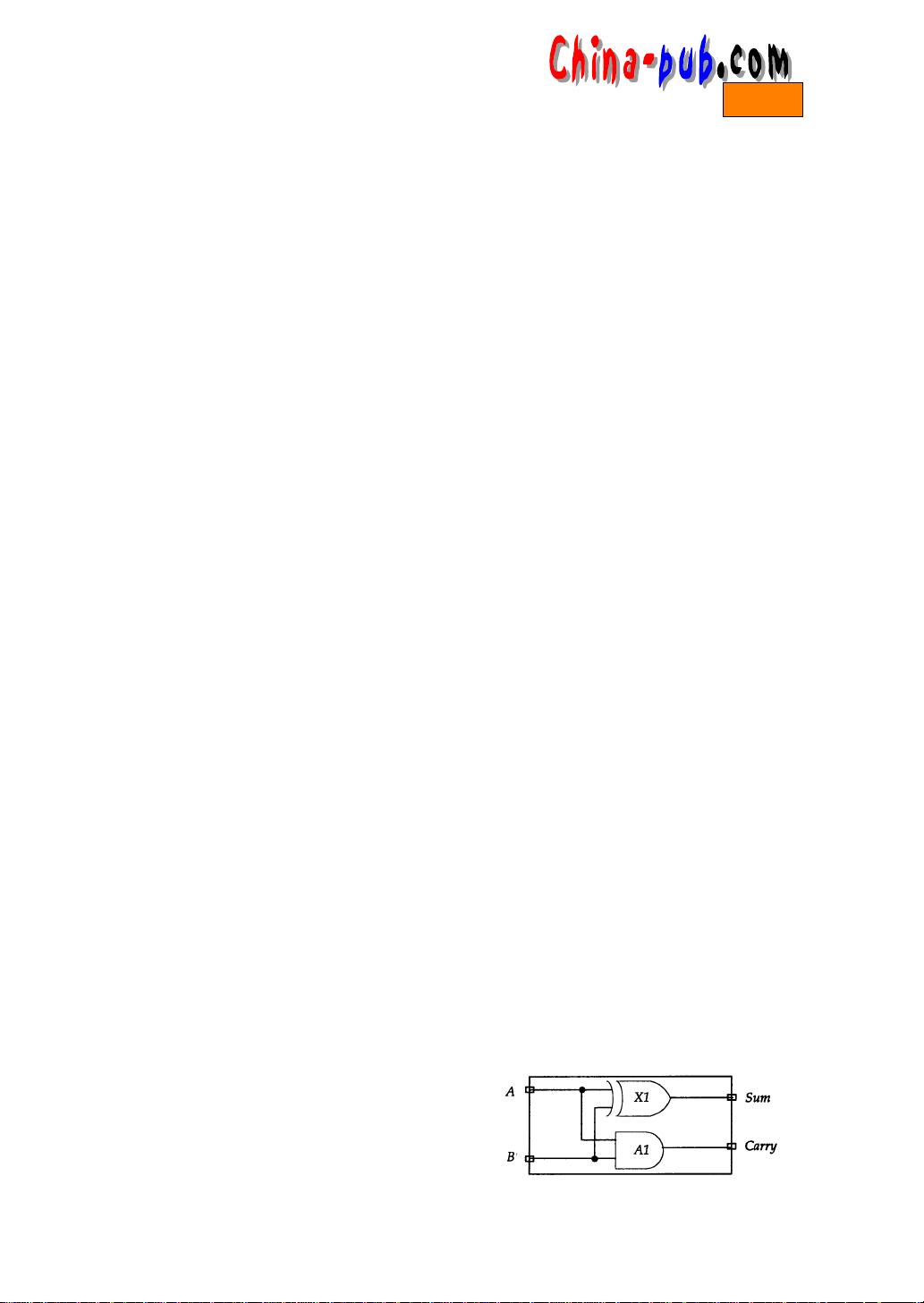

以半加器为例,一个简单的模块声明如下:

```verilog

module Half_Adder (A, B, Sum, Carry);

input A, B;

output Sum, Carry;

assign #2 Sum = A ^ B;

assign #5 Carry = A & B;

endmodule

```

在这个例子中,`Half_Adder`模块有两个输入端口`A`和`B`,以及两个输出端口`Sum`和`Carry`。由于没有指定端口的宽度,它们默认为单比特。连续赋值语句`assign`定义了`Sum`和`Carry`的计算逻辑,表示半加器的数据流行为。这里的`#2`和`#5`是延迟时间,意味着计算会有相应的时间延迟。

理解Verilog HDL的关键在于掌握模块的结构和语法规则,以及如何利用它们来描述数字系统的逻辑。在实际的设计过程中,通常会遵循一定的编码规范,如将声明部分放在语句之前,以提高代码的可读性和维护性。通过学习和实践,工程师可以利用Verilog HDL实现复杂的数字系统设计,从而在电子设计自动化领域发挥重要作用。

2019-02-23 上传

146 浏览量

2012-12-02 上传

2008-04-09 上传

2012-02-18 上传

2024-12-24 上传

2024-12-24 上传

2024-12-24 上传

2024-12-24 上传

yangxujunboy

- 粉丝: 2

- 资源: 4

最新资源

- 电子功用-含导电胶元件的处理装置

- 北方交通大学硕士研究生入学考试试题结构力学2003.rar

- 狂神说JVM探究md完整版

- fewpjs-acting-on-events-online-web-sp-000

- 一个简单实现循环滚动视图效果

- 电子功用-电力负荷程控模拟装置

- linux-Linux驱动程序模板.zip

- AgendaModule:Avans - 技术信息学 - 第 3 期 - 项目节策划者

- goit-react-hw-02-phonebook

- SpringBoot+MyBatisPlus+MySQL绩效考核系统源码.zip

- foxx-mailer-mandrill:使用Mandrill的Foxx的邮件工作类型

- 一款实现特殊的Paging滚动视图效果

- dss-binalyadav:GitHub Classroom创建的dss-binalyadav

- 电子功用-基于二阶滤波电路的ETC传感系统

- 基于yolov7得并联机械臂实时抓取(python)

- fewpjs-fns-as-first-class-data-array-o-functions-online-web-sp-000