Verilog 实现 (2,1,4) 卷积码译码器设计与分析

需积分: 15 2 浏览量

更新于2024-09-15

收藏 195KB PDF 举报

"该文档详细介绍了卷积码译码器的设计,特别关注了(2,1,4)卷积码的编码和维特比译码器的实现,同时提供了Verilog HDL代码示例。文档内容包括卷积码的基本原理、纠错能力分析以及Viterbi译码算法的应用。"

卷积码是一种重要的前向错误校正(FEC)编码技术,广泛应用于通信系统中,以提高数据传输的可靠性。卷积码的特点在于它产生的码元不仅与当前的信息码元有关,还与之前的信息码元有关,形成了一个“记忆”效应,这使得编码过程中的码元相互关联,从而增强了纠错能力。

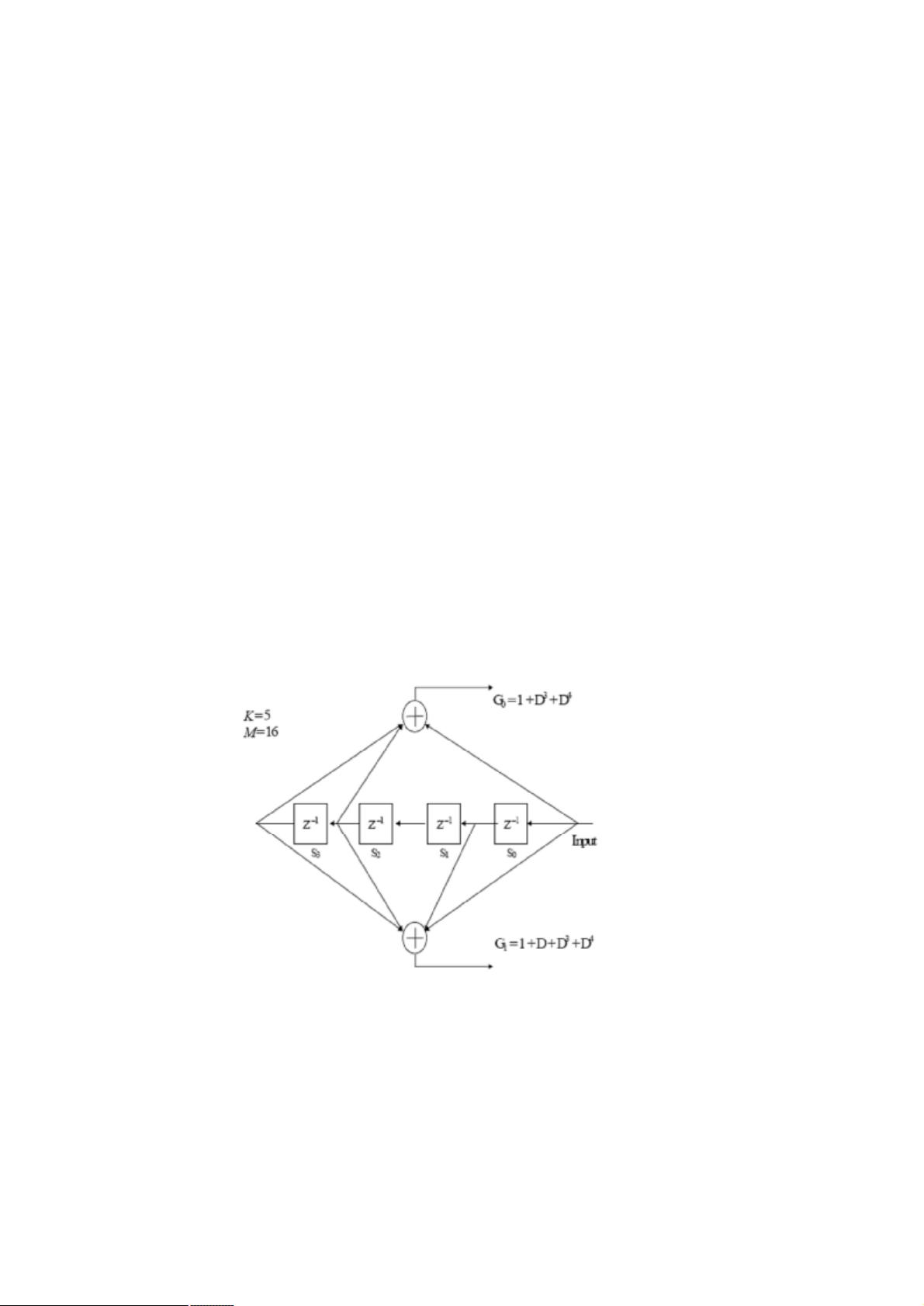

(2,1,4)卷积码是一个特定类型的卷积码,其中n=2表示输出的码元个数,k=1表示输入的信息码元个数,m=4是约束长度。编码规则如文档中所述,通过线性组合输入和多个延迟状态(D0, D2, D3)生成输出码元C[1]和C[0]。这种卷积码的Viterbi译码器是基于最大似然原则工作的,译码过程通过在网格图(也称为 trellis 图)中寻找与接收到的噪声干扰码序列最匹配的路径来实现。

Viterbi译码算法的关键在于使用维特比距离计算接收码序列与可能的编码路径之间的差异,以确定最有可能的原始信息序列。在篱笆图(图2)中,每个节点代表编码器的状态,实线和虚线表示0和1码元,状态会按照一定的规律循环出现。译码器包含多个阶段,例如 ACS(Add-Compare-Select)模块,用于在每个时钟周期计算两个路径的差值,并选择最优路径。

在Verilog HDL实现中,通常会设计一个总体结构,包括编码和解码部分。编码部分将原始的01信息码转换为卷积码,而解码部分则接收编码后的码流并结合随机噪声模拟实际通信环境。Viterbi译码器会输入这些编码码流,通过计算和比较路径,找到最佳路径并恢复原始信息。

在设计中,模块如`acs0`, `acs1`, `acs23`, `acs_4_7`, `acs_8_15`等分别对应于Viterbi算法的不同部分,它们负责处理不同状态间的路径选择和距离计算。`mod2`模块可能用于计算路径差值的模2操作,以简化距离计算。

这份文档提供了深入理解卷积码译码器设计的详细知识,包括理论基础和具体的硬件描述语言实现,对于学习通信系统和数字信号处理的工程师非常有价值。通过学习和应用这些概念,可以有效地提升通信系统的抗干扰能力和数据传输的准确性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

114 浏览量

118 浏览量

2021-07-13 上传

148 浏览量

pfeng005

- 粉丝: 0

- 资源: 1

最新资源

- CI--EA实施

- 24L01模块原理图+PCB两种天线三块板子

- Horiseon-proyect

- SimbirSoft

- 钟摆模型:用于不同实验的 Simulink 模型-matlab开发

- shopcart.me

- 6ES7214-1AG40-0XB0_V04.04.00.zip

- hivexmlserde jar包与配套数据.rar

- KeepLayout:使自动布局更易于编码

- worldAtlas

- AdvancedPython2BA-Labo1

- lsqmultinonlin:共享参数的全局参数非线性回归-matlab开发

- STK3311-WV Preliminary Datasheet v0.9.rar

- js实现二级菜单.zip

- 微店助理 千鱼微店助理 v1.0

- tao-of-rust-codes:作者的回购