VHDL实现:半整数分频器设计与原理

下载需积分: 9 | PDF格式 | 597KB |

更新于2024-07-30

| 157 浏览量 | 举报

"该资源主要介绍了基于VHDL的数字系统设计,特别是通过实例讲解了半整数分频器的设计,适用于VHDL初学者学习。"

在VHDL编程中,数字系统设计是一项核心技能,尤其对于硬件描述语言的学习者而言。本章节主要讨论了如何使用VHDL设计各种数字系统,包括实例化的半整数分频器、音乐发生器、2FSK/2PSK信号产生器、实用多功能电子表、交通灯控制器以及数字频率计。这些实例有助于读者深入理解VHDL在实际应用中的工作原理和设计过程。

首先,我们关注的是半整数分频器的设计。在数字电路中,分频器是常见的频率处理单元,它可以将输入的高频率信号转换为较低的频率信号。通常,我们可以使用标准计数器或者可编程逻辑器件(如FPGA)来构建整数分频器。然而,当需要的输出频率与输入时钟频率不成整数倍关系时,就需要使用到小数分频器。

小数分频的基本原理是脉冲吞吐计数法,它结合了不同分频比的整数分频器。例如,要实现一个分频系数为2.5的分频器,可以设计一个模3计数器,配合扣除脉冲电路,每接收两个脉冲就扣除一个,以达到2.5的分频效果。这种方法也可以扩展到设计任意半整数分频系数的分频器。

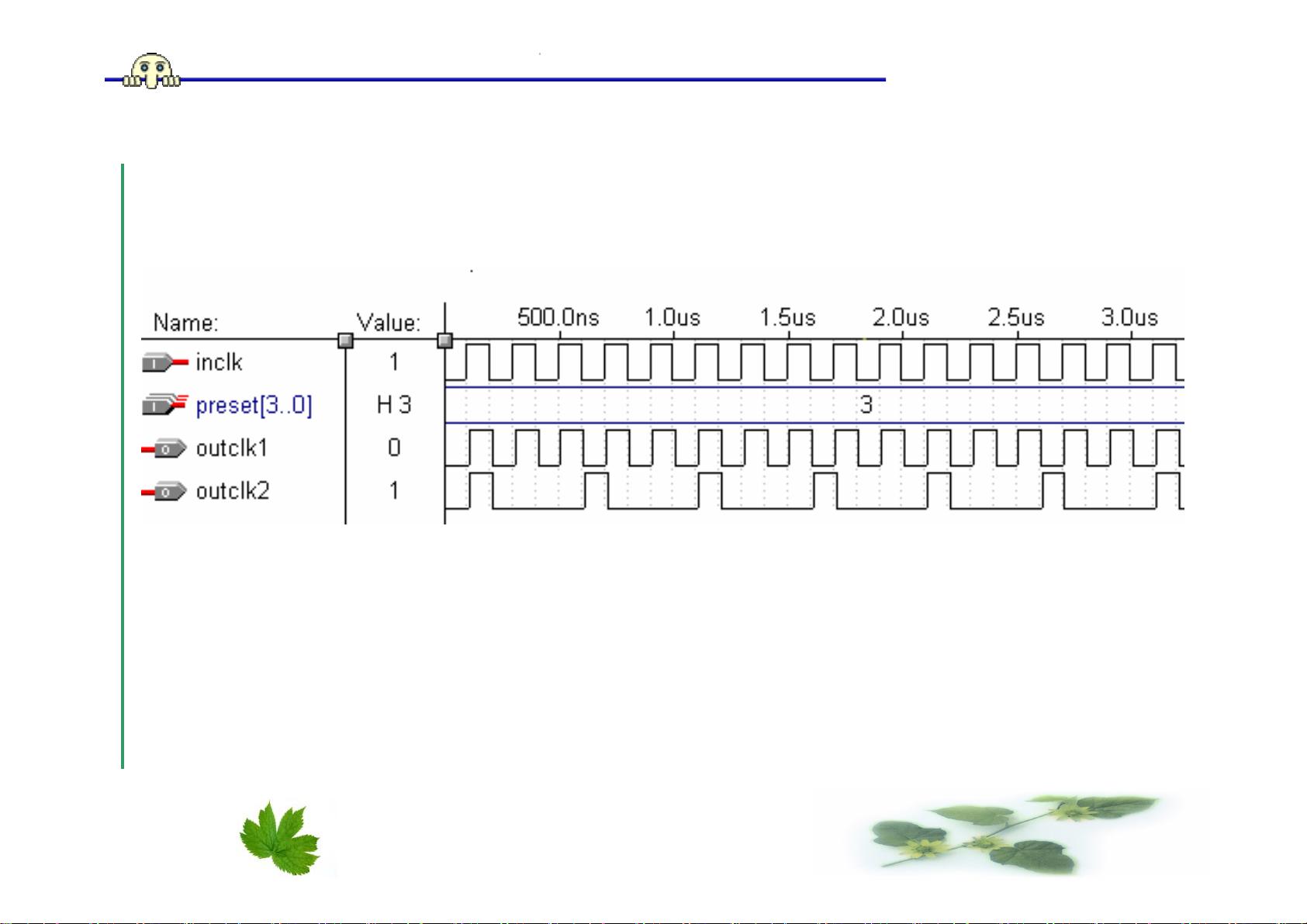

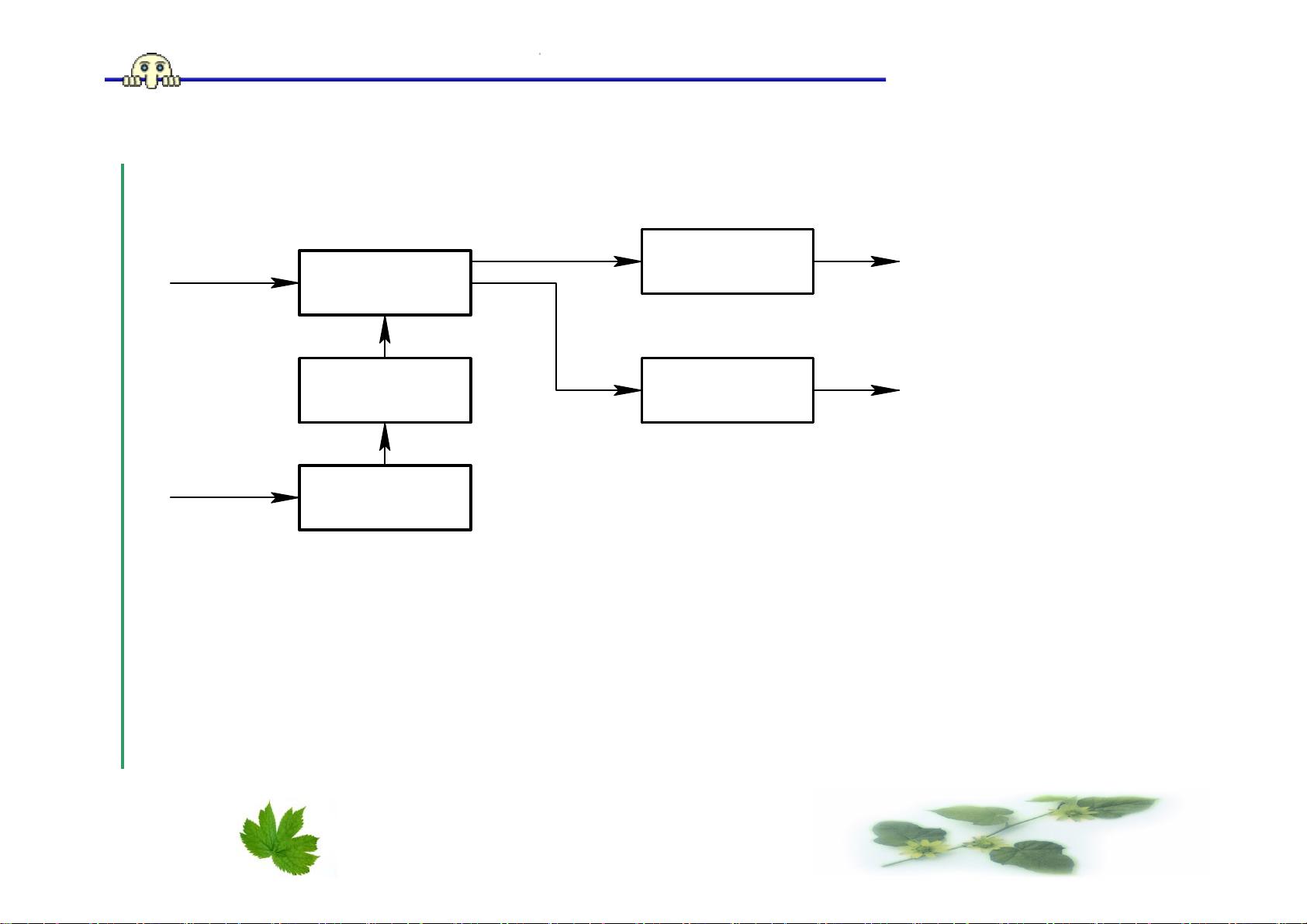

当分频系数为N-0.5时,电路可以通过控制扣除脉冲的时间,使得输出信号频率稳定。电路通常由模N计数器、二分频器和异或门组成。模N计数器可以预置,以适应任意分频系数为N-0.5的分频需求。图7-1展示了这种通用半整数分频器的结构,其中异或门用于生成扣除脉冲,二分频器用于进一步降低频率,而模N计数器则负责基础的计数操作。

此外,文中还提到了其他几个数字系统设计实例,如音乐发生器,它可能涉及到波形生成和定时控制;2FSK/2PSK信号产生器,这是通信系统中常见的调制技术,用于数据传输;实用多功能电子表,可能包含了时间显示和计时功能;交通灯控制器,涉及时序逻辑控制;以及数字频率计,用于测量输入信号的频率。这些实例覆盖了不同的数字系统设计领域,为学习者提供了丰富的实践机会。

这个资源为VHDL初学者提供了一套全面的实践教程,不仅介绍了基本的理论知识,还通过实例深入浅出地解释了如何利用VHDL设计和实现复杂的数字系统。对于那些希望掌握VHDL并应用到实际项目中的学习者来说,这是一份极具价值的学习材料。

相关推荐

tianma330

- 粉丝: 0

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例