VHDL实现异步FIFO设计:解决空满标志与亚稳态问题

174 浏览量

更新于2024-08-31

收藏 256KB PDF 举报

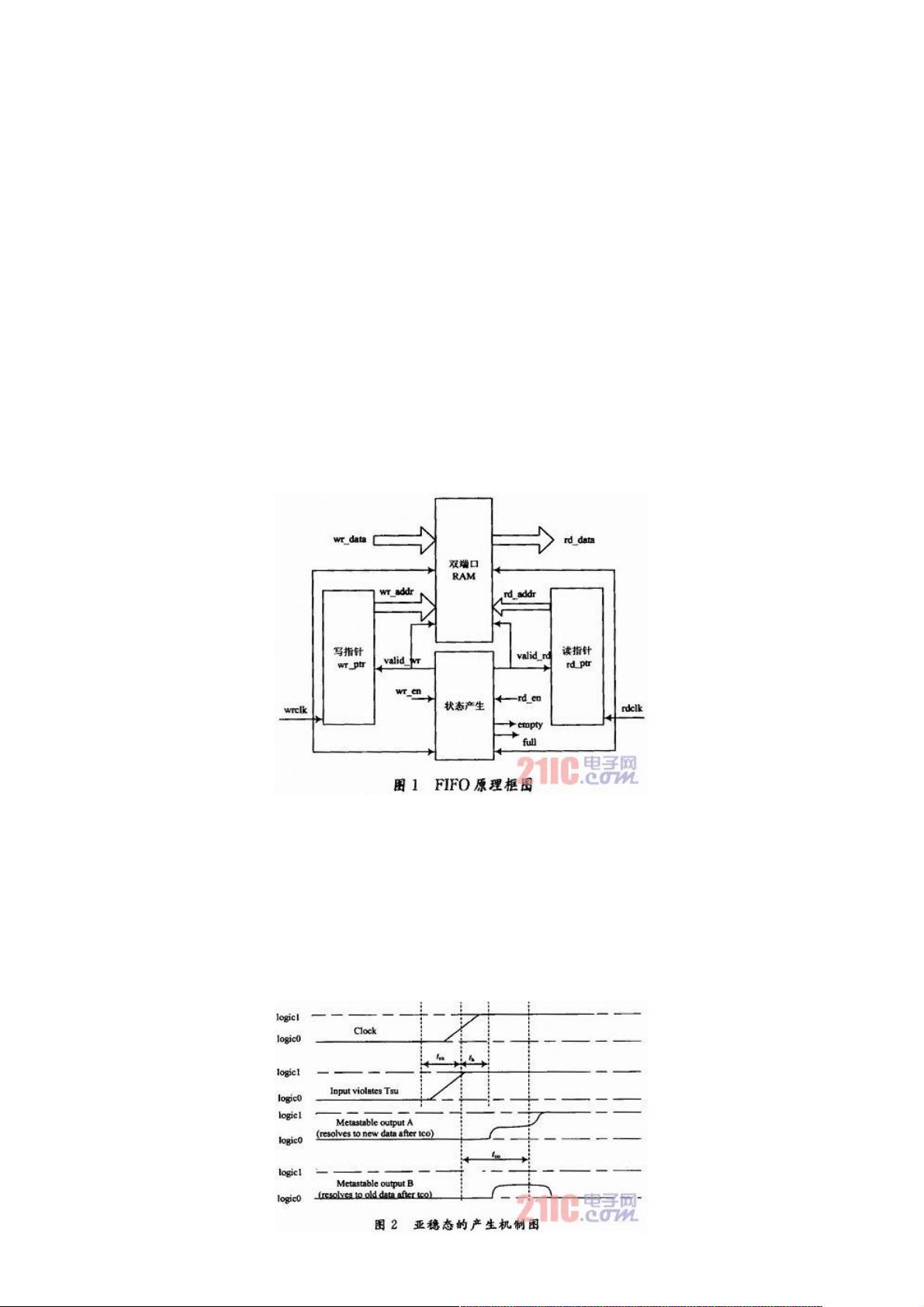

在本文中,我们将深入探讨"基于VHDL的异步FIFO设计"这一主题。FIFO(First-In-First-Out,先进先出)是一种重要的数据存储和传输机制,特别适用于不同时钟域之间的数据交换,如在空空导弹的数据传输体系中。异步FIFO与同步FIFO的主要区别在于读写时钟的同步性:同步FIFO的时钟频率成倍数关系,而异步FIFO则没有这种限制,能够实现跨时钟域的实时数据传输。

在异步FIFO的设计中,一个主要挑战是处理空满标志的生成和避免亚稳态问题。空满标志的判断通常是基于读写指针的状态变化,当读写指针在复位或读操作后相等,FIFO被视为为空;反之,写操作后指针相等,则认为FIFO已满。然而,由于时钟域的不同步性,确保这些指针的一致性和正确性是一个复杂的过程,需要精确的时序控制和同步机制。

亚稳态是FPGA设计中的另一大难题,它发生在信号在不同时钟域传输时,可能导致系统的暂时不稳定。数字器件,包括FPGA,对输入信号有严格的时序要求,即输入信号需在时钟沿之前稳定并在之后保持一段时间,以确保寄存器正确地存储和输出数据。如果这些时序条件不满足,输出信号可能会处于亚稳态,造成系统功能的错误。

为解决这些问题,本文提出了一种新颖的设计方案,即使用格雷码计数器,这是一种特殊的计数器,每次时钟脉冲仅有一位状态改变,这有助于减少时钟域转换带来的干扰,并有效地同步读写操作和空满标志的判断。通过这种方式,设计者能够在异步环境下创建可靠的FIFO,提高数据传输的准确性和可靠性。

基于VHDL的异步FIFO设计不仅关注硬件结构的实现,还涵盖了深入的时序分析和同步策略,确保了在复杂时钟环境下的高效和稳定数据流管理。理解并掌握这些设计技巧对于开发高性能的嵌入式和实时系统至关重要。

weixin_38681301

- 粉丝: 5

- 资源: 921

最新资源

- 如何将数据从CSV和XML导入MS SQL Server

- ROMsettaStone.SoE:SoE的ROMsetta Stone文档

- redux-rest-actions:使用Redux发出REST请求的中间件

- g

- meta-llama-3-8b-instruct 的 model-00002-of-00004.safetensors 的1/3

- laravelapi-vueui

- git-training1:训练库

- netassist.zip

- VM

- ac1poo_190583

- StreamEventCoreference

- emp_curate_data:用于为#EEGManyPipelines准备EEG数据的代码

- computer-systems:穿越计算机系统

- feign_v960依赖的jar包.rar

- vuls-log-converter

- 门业生产企业网站模版