Verilog教程:综合与组合逻辑解析

需积分: 9 118 浏览量

更新于2024-07-28

收藏 189KB PPT 举报

"这是一份关于Verilog的英语教学材料,涵盖了Verilog的基础内容,适合初学者学习。"

在深入探讨Verilog语言之前,我们首先理解一下标题和描述中的关键概念。`verilog_tutorial`表明这是一个关于Verilog的教程,而`PPT`标签提示我们这份资料可能是以PowerPoint的形式呈现,包含了丰富的视觉辅助和讲解。

Verilog是一种硬件描述语言(HDL),用于设计和描述数字系统的逻辑功能,包括集成电路、微处理器、接口和存储器等。在这个英语课件中,你将学习如何使用Verilog来构建和验证数字逻辑设计。

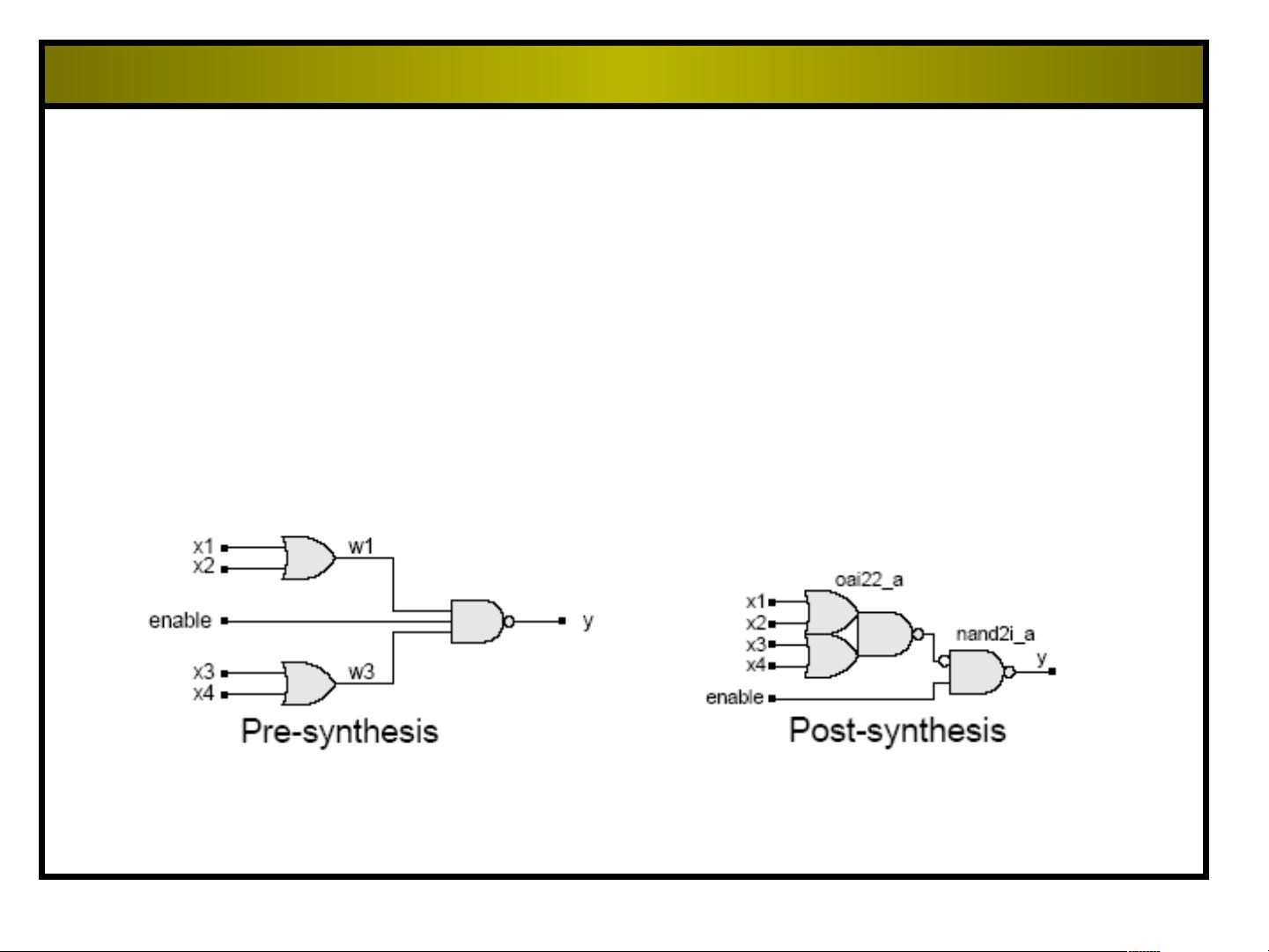

描述中提到的"Synthesis-Combinational Logic"是Verilog设计流程中的一个关键步骤。综合(Synthesis)是将高级的Verilog代码转换成实际电路的过程,而组合逻辑(Combinational Logic)是指输入信号立即决定输出的无记忆逻辑功能。

在Verilog中,组合逻辑函数可以表示为:`logic_output(t) = f(logic_inputs(t))`,即输出在任何时刻都是由当前输入值决定的。在编写组合逻辑时,有以下几点需要注意:

1. 避免依赖于特定技术的建模,应关注功能实现而非时序。

2. 组合逻辑不应包含反馈,以防止形成环路。

3. 必须为所有可能的输入组合指定输出,确保功能完整无遗漏。

4. 如果逻辑不是组合性的,合成工具会将其视为顺序逻辑处理。

组合逻辑的实现风格多样化,包括:

1. 完全结构化的门级网表,即直接使用门实例和Verilog原语。

2. 组合逻辑用户定义的部件(UDP)。

3. 函数(Function)。

4. 连续赋值(Continuous Assignment)。

5. 行为语句,如if-else结构,但不包含事件或延迟控制。

6. 任务(Task)没有事件或延迟控制。

7. 上述各种风格的模块间互连。

在合成组合逻辑时,工具会进一步优化以门级网表形式表示的Verilog原始语句。例如,下面的代码展示了如何用Verilog表示一个三输入的与非门(NAND):

```verilog

module or_nand_1(enable, x1, x2, x3, x4, y);

input enable, x1, x2, x3, x4;

output y;

wire w1, w2, w3;

or(w1, x1, x2);

or(w2, x3, x4);

or(w3, w1, w2);

// NAND gate with enable control

assign y = (enable == 1'b1) ? ~w3 : 1'bz;

endmodule

```

在这个例子中,通过`or`函数创建了逻辑或门,并通过连续赋值语句`assign`实现了带使能控制的NAND门。

通过这个英语课件,你将学习到如何用Verilog描述组合逻辑,并了解其在综合过程中的表现和优化。这份教程对于理解和掌握Verilog语言的基础知识至关重要,是成为熟练的数字系统设计师的第一步。

340 浏览量

点击了解资源详情

点击了解资源详情

2021-09-30 上传

340 浏览量

2022-09-20 上传

162 浏览量

2011-06-06 上传

xdrobin

- 粉丝: 2

- 资源: 4

最新资源

- 奇偶校验-WebAssembly低级格式库-Rust开发

- 通过visa控制Agilent信号源

- elves-of-santa-101-global-packaging:如何制作一个全局npm软件包。 Hello World应用程序

- contactForm

- django-project-manager:django中的prosectos实现程序

- 草根域名注册批量查询工具 v8.0

- Javascript-TaskList

- WDD430-Lesson1

- 行业文档-设计装置-面料服装效果图开发平台及呈现方法.zip

- 智睿中小学生学籍信息管理系统 v2.7.0

- test2

- windos 上位机I2C、SPI、GPIO转USB,USB转I2C、SPI、GPIO组件

- skyfn

- ProjectPal:使用Electron制作的CodingProgramming项目经理和Idea Generator

- FE内容付费系统响应式(带手机版) v4.51

- 华峰超纤-300180-一体化超纤革赛道冠军,向高附加值领域延伸成长前景向好.rar