Application Note 86

AN86-9

Approach and Error Considerations

This schematic is deceptively simple. In practice, con-

struction details are crucial. Parasitic thermocouples

(Seebeck effect), layout, grounding, shielding, guarding,

cable choice and other issues affect achievable perfor-

mance.

1

In fact, as good as the chopper-stabilized LTC1152

is with respect to drift, offset, bias current and CMRR,

selection is required if we seek sub-ppm nonlinearity

performance. Figure C4, an error budget analysis, details

some of the selection criteria.

Note 1: See Appendix J, “Cables, Connections, Solder, Layout,

Component Choice, Terror and Arcana,” for relevant tutorial.

Note 2: See above Footnote.

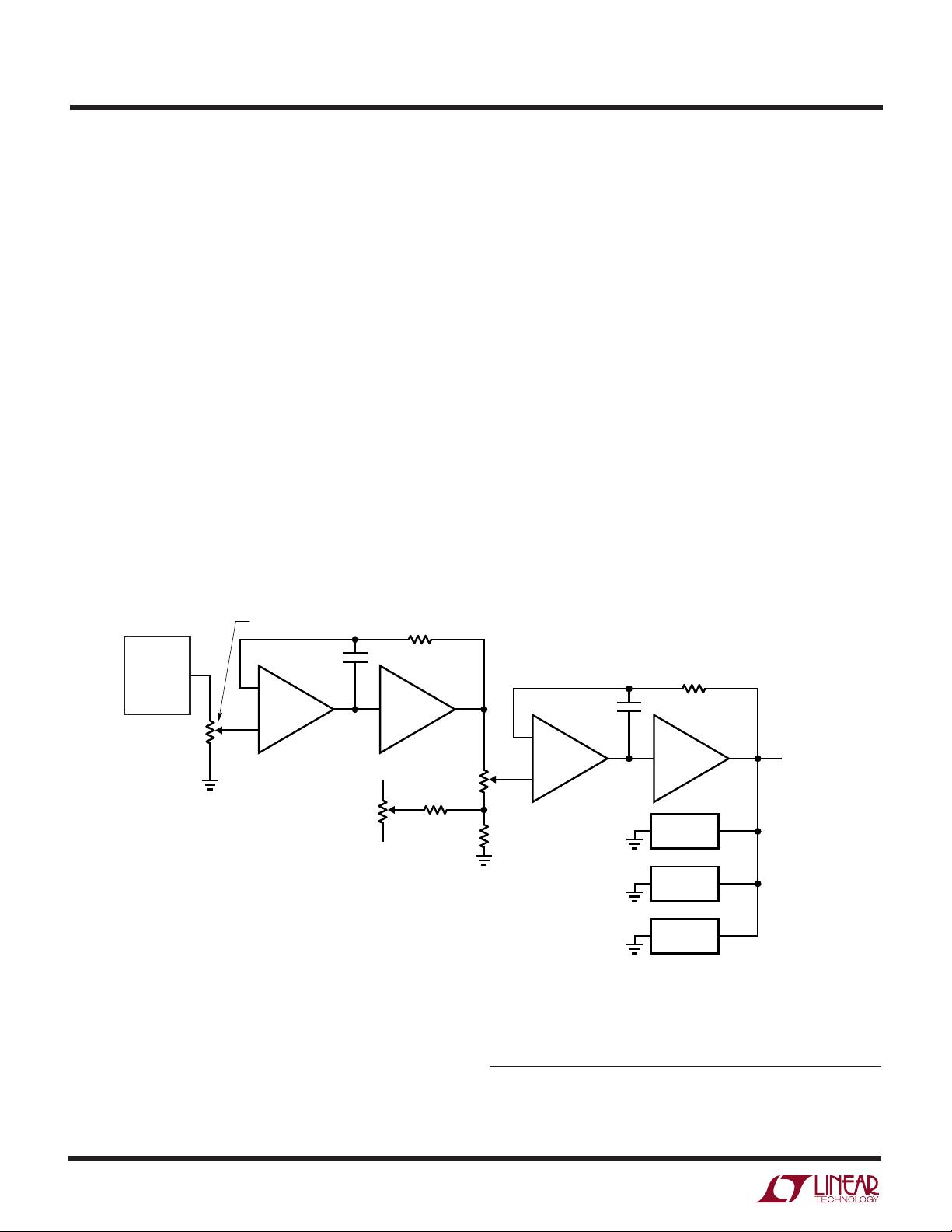

The buffer is tested with Figure C5’s circuit. As the KVD is

run through its entire range, the floating null detector must

remain well within 1ppm (5µV), preferably below 0.5ppm.

This test ensures that all error sources, particularly I

B

and

CMRR, whose effects vary with operating point, are ac-

counted for. Measured performance indicates the sum of

all errors called out in Figure C4 is well within desired

limits.

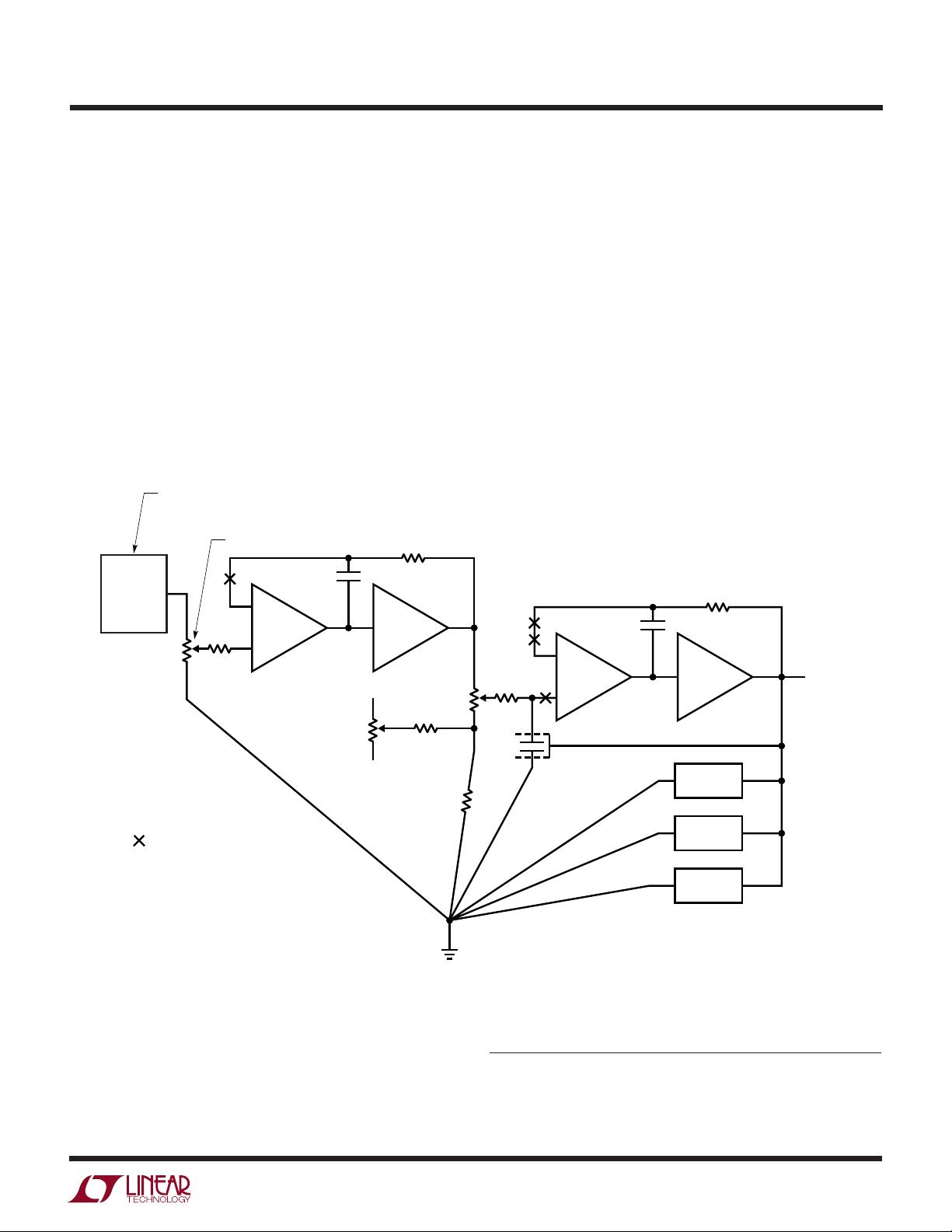

In Figure C6, we add offset trim, a stable voltage source

and a second KVD to drive the main KVD. Additionally, an

ensemble of three HP3458A voltmeters monitor the out-

put.

The offset trim bleeds a small current into the main KVD

ground return, producing a few microvolts of offset-trim

range. This functionally trims out all sources of zero error

(amplifier offsets, parasitic thermocouple mismatches

and the like), permitting a true zero volt output when the

main KVD is set to all zeros.

The voltmeters, specified for <0.1ppm nonlinearity on the

10V range, “vote” on the source’s output.

Circuitry Details

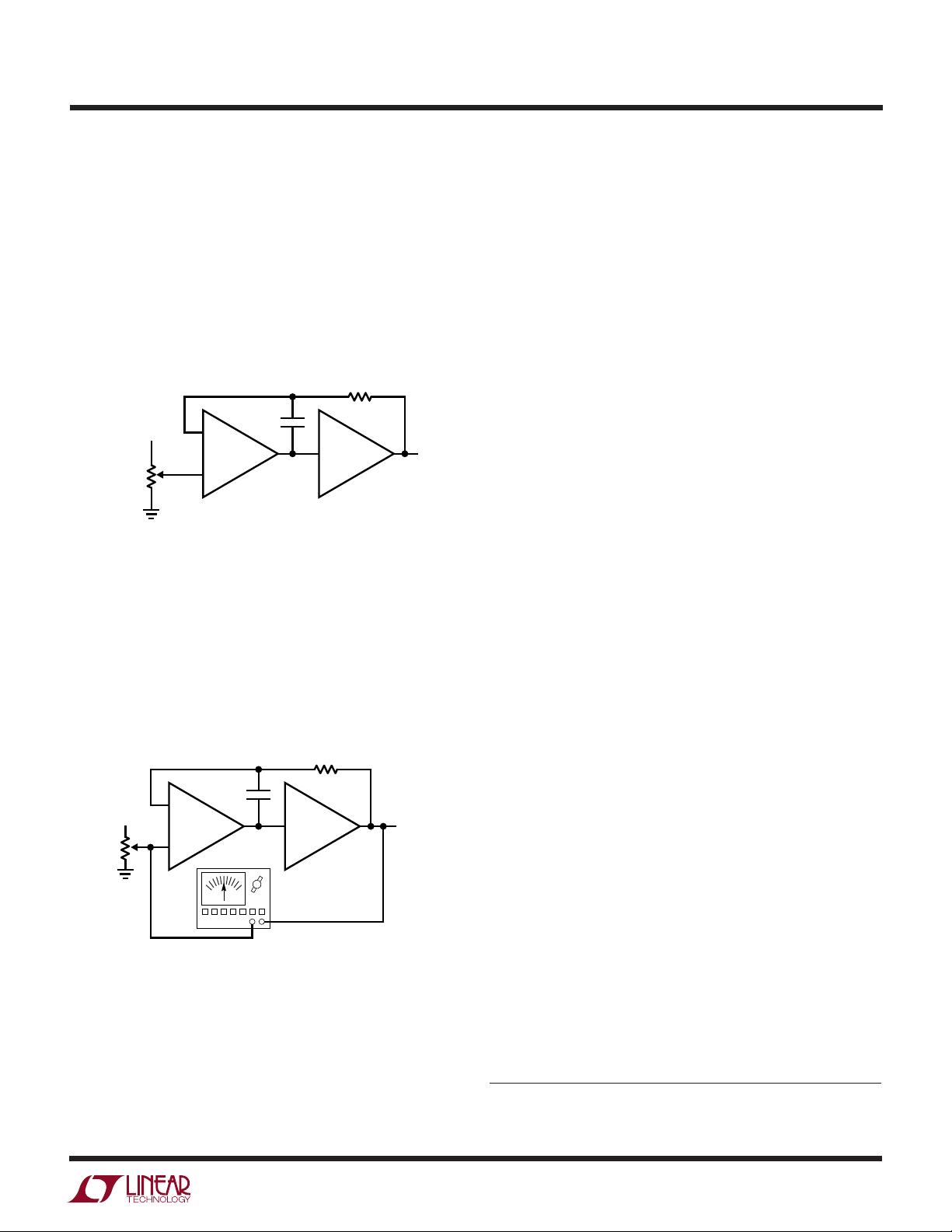

Figure C7 is a more detailed schematic. It is similar to

Figure C6 but highlights issues and concerns. The ground-

ing scheme is single point, preventing mixing of return

currents and the attendant errors. The shielded cables

used for interconnections between the KVDs and voltme-

ters should be specified for low thermal activity. Keithley

type SC-93 and Guildline #SCW are suitable. Crush type

copper lugs (as opposed to soldered types) provide lower

parasitic thermocouple activity at KVD and DVM connec-

tion points. However, they must be kept clean to prevent

oxidation, thus avoiding excessive thermal voltages.

2

A

copper deoxidant (Caig Labs “Deoxit” D100L) is quite

effective for maintaining such cleanliness. Low thermal

lugs and jacks, preterminated to cables, are also available

(Hewlett-Packard 11053, 11174A) and convenient.

Thermal baffles enclosing KVD and DVM connections tend

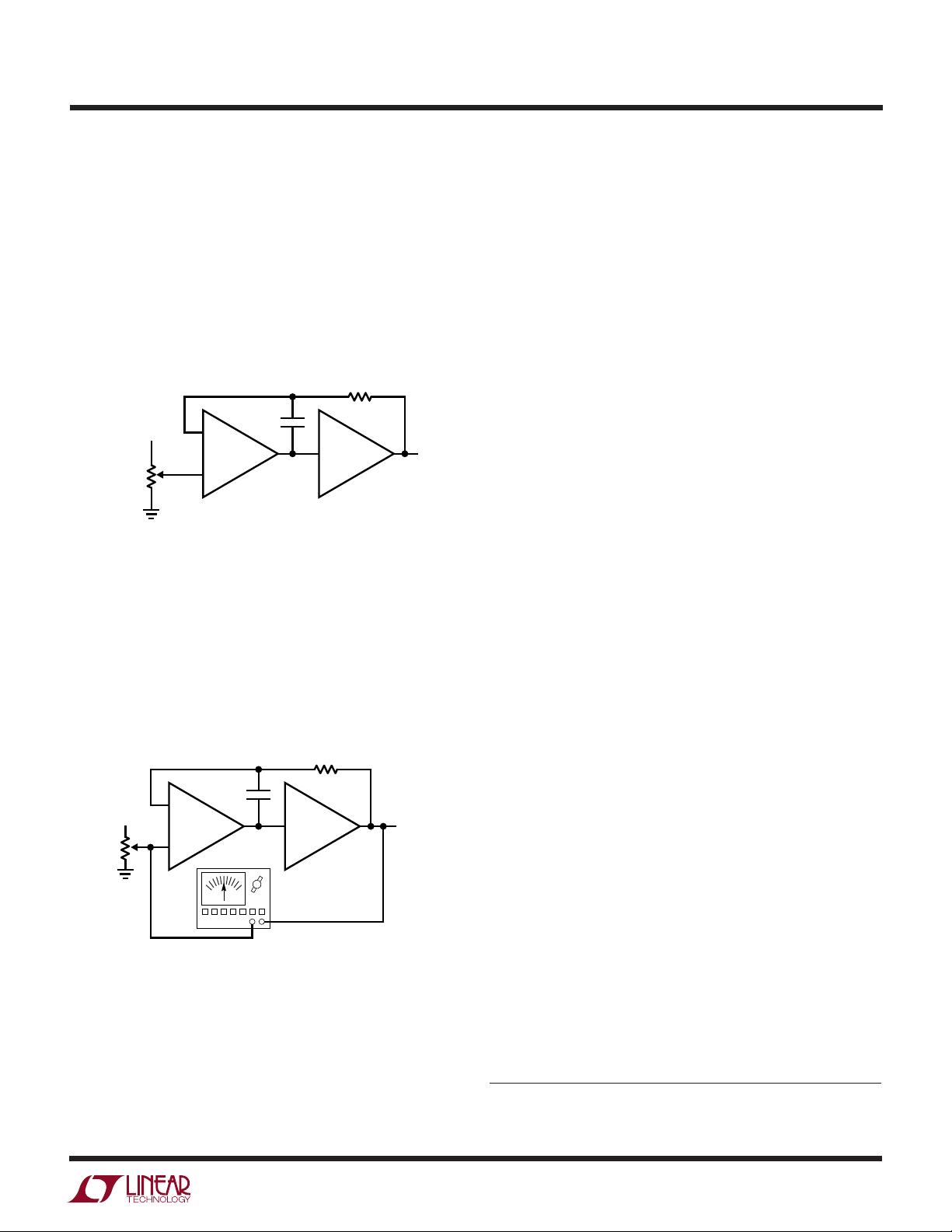

Figure C4. Error Budget Analysis for the KVD Buffer.

Selection Permits ≈0.4ppm Predicted Linearity Error

0.1µF

LT1010

OUTPUT

10k

KVD R

IN

= 100k

≈ 30k

WORST-CASE

OUTPUT

RESISTANCE

5V

AN86 FC04

ERROR

SOURCE

E

OS

E

OS∆T

I

B

CMRR

FINITE GAIN

WORST-CASE

SPEC

5µV

0.05µV/°C

50pA

110dB

140dB

REALISTIC SELECTION

TARGET

0.5µV

0.05µV/°C

10pA

140dB

140dB

ERROR IN

PPM

0.1

0.01/°C

0.1

0.1

0.1

+

–

LTC1152

Figure C5. Determining Buffer Error By Measuring Input-Output

Deviation with Floating Microvolt Null Detector. Technique

Permits Evaluation of Fixed and Operating Point Induced Errors

AN86 FC05

0.1µF

+

–

LTC1152

5V

KVD

FLOATING, BATTERY-POWERED

µV NULL DETECTOR

HP-419A

LT1010

OUTPUT

10k