Verilog HDL入门:基本语法详解

需积分: 10 33 浏览量

更新于2024-07-31

收藏 409KB PDF 举报

"Verilog基本语法入门教程,涵盖了Verilog HDL的基础知识,包括不同级别的抽象模型和语言特性,适用于初学者。"

Verilog HDL是一种广泛使用的硬件描述语言,用于设计和验证数字逻辑电路。本教程针对入门级学习者,旨在提供Verilog的基本语法知识,后续还将提供更深入的学习资料,与夏宇闻老师的教材同步,去除了冗余文字,确保每个字都具有实质性的学习价值。

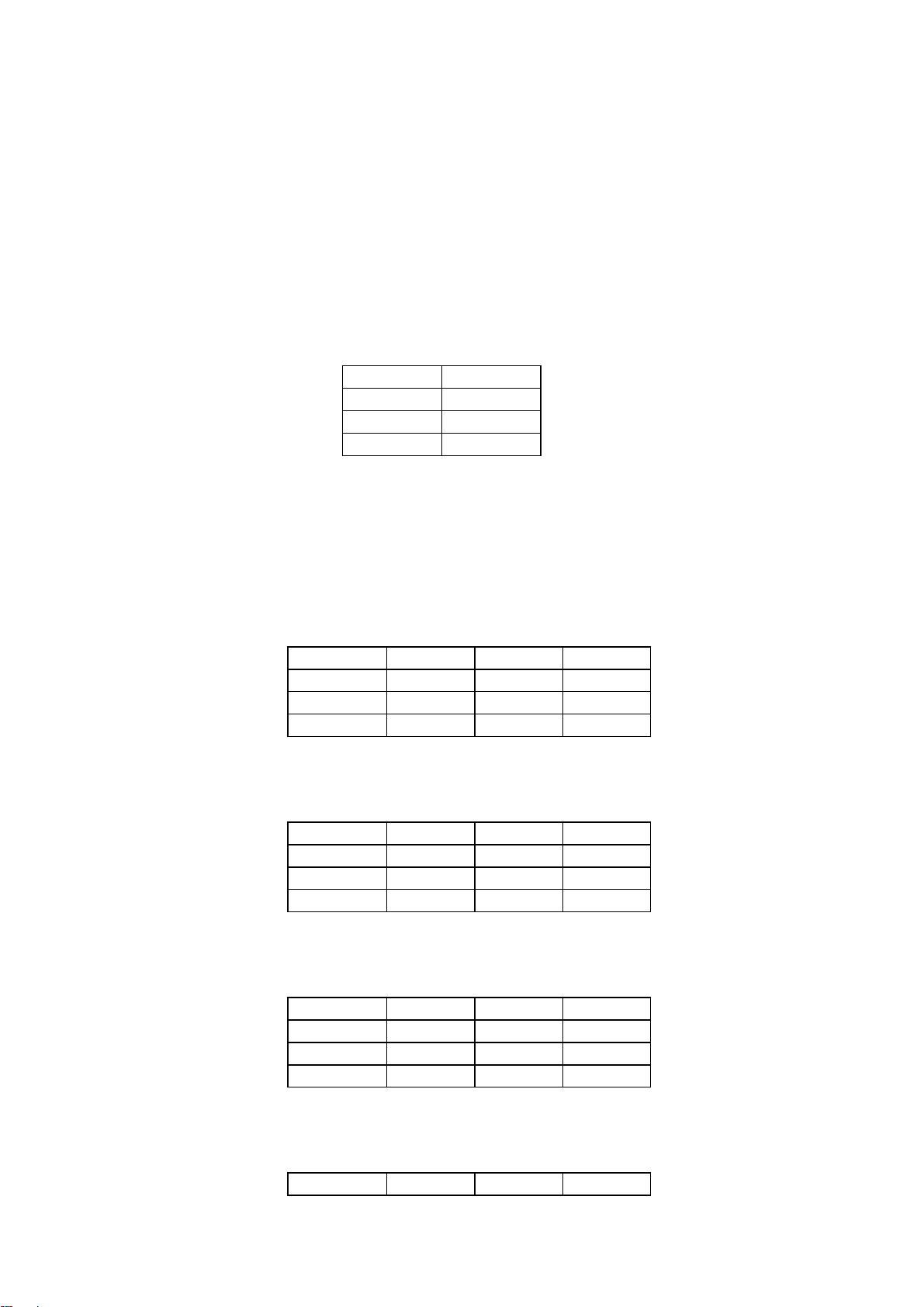

在Verilog HDL中,设计可以被描述为五个级别的抽象模型:

1. **系统级 (system)**: 这一级别关注设计模块的外部行为,使用高级语言结构来体现系统的整体性能。

2. **算法级 (algorithm)**: 在这一级别,设计的算法被详细描述,侧重于功能的实现。

3. **RTL级 (Register Transfer Level)**: 描述数据在寄存器之间的传输和处理,是数字设计中常见的抽象层。

4. **门级 (gate-level)**: 在这个级别,设计被表示为逻辑门的网络,如AND、OR和NOT门等。

5. **开关级 (switch-level)**: 最低级别的抽象,涉及到晶体管和存储节点的物理连接,用于模拟电路行为。

Verilog HDL允许设计师通过模块化的方式来构建复杂的电路系统。每个模块可以包含子模块,形成层次化的结构,便于管理和验证。某些模块会被综合成实际电路,而其他模块可能代表已经存在的硬件或测试激励。

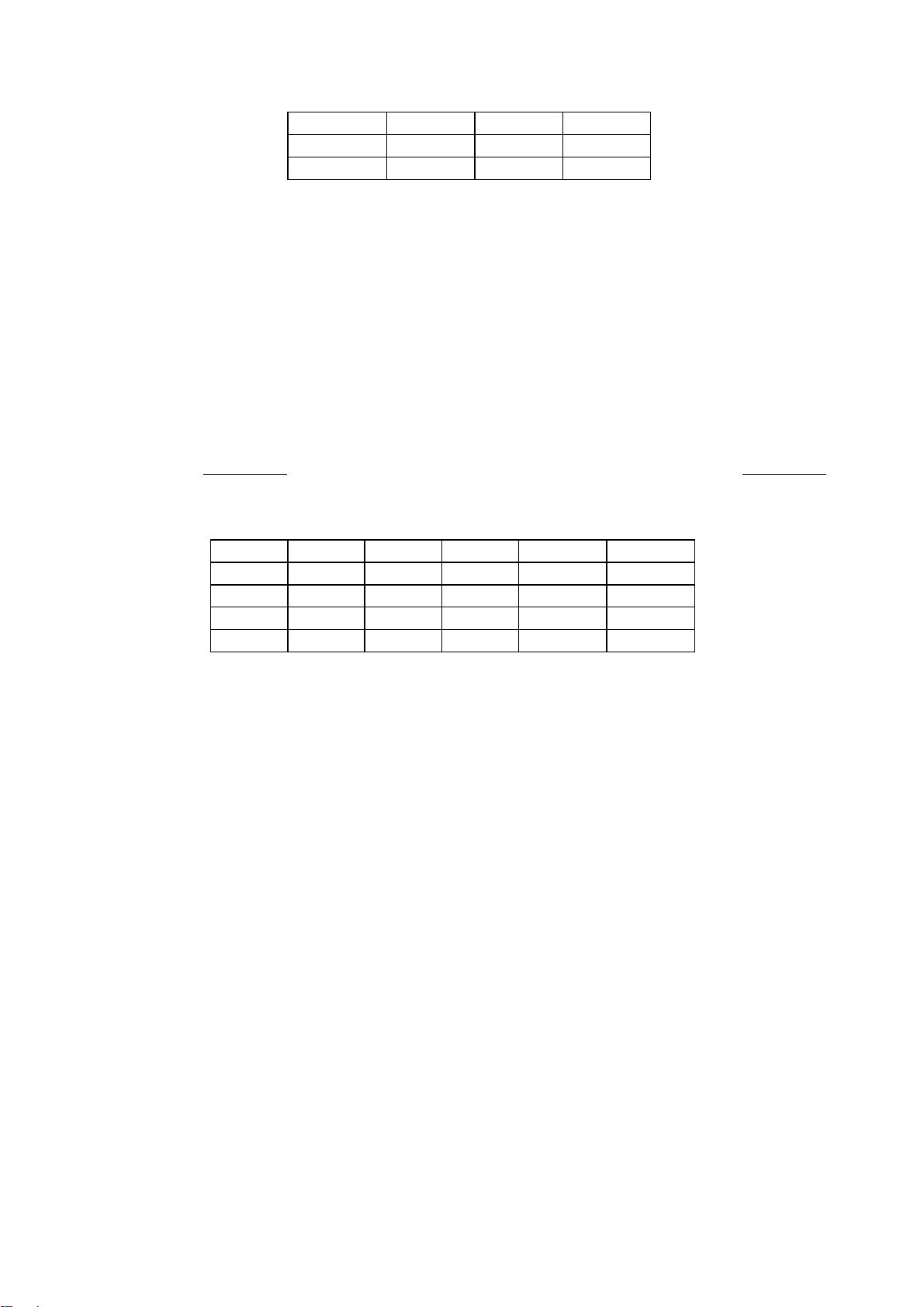

Verilog HDL的行为描述语言特性使得它在算法级和RTL级设计中特别强大:

- **顺序与并行执行**:Verilog支持顺序和并行的程序结构,模拟硬件中的并发行为。

- **事件驱动**:通过延迟和事件表达式控制流程的启动时间,使设计能响应特定的时序事件。

- **事件触发**:命名事件可以触发或停止其他进程的行为,增强设计的灵活性。

- **控制结构**:提供了条件语句(if-else)、case语句和循环,方便编写复杂的控制逻辑。

- **任务与函数 (task and functions)**:任务支持带参数的非阻塞操作,函数则用于计算,两者增强了代码的复用性。

- **非阻塞赋值**:非阻塞赋值(<=)用于并行处理,避免了不必要的信号竞争。

此外,Verilog还支持数据类型定义、接口、类、包装、综合属性等高级特性,使得它成为现代数字系统设计不可或缺的工具。学习Verilog的基本语法是进入数字设计世界的必要步骤,它将帮助你理解和创建各种规模的数字逻辑电路模型。

3719 浏览量

364 浏览量

2023-05-02 上传

119 浏览量

123 浏览量

183 浏览量

287 浏览量

662 浏览量

kobeyin

- 粉丝: 3

最新资源

- 经典J2ME坦克对战游戏:回顾与介绍

- ZAProxy自动化工具集合:提升Web安全测试效率

- 破解Steel Belted Radius 5.3安全验证工具

- Python实现的德文惠斯特游戏—开源项目

- 聚客下载系统:体验极速下载的革命

- 重力与滑动弹球封装的Swift动画库实现

- C语言控制P0口LED点亮状态教程及源码

- VB6中使用SQLite实现列表查询的示例教程

- CMSearch:在CraftMania服务器上快速搜索玩家的Web应用

- 在VB.net中实现Code128条形码绘制教程

- Java SE Swing入门实例分析

- Java编程语言设计课程:自动机的构建与最小化算法实现

- SI9000阻抗计算软件:硬件工程师的高频信号分析利器

- 三大框架整合教程:S2SH初学者快速入门

- PHP后台管理自动化生成工具的使用与资源分享

- C#开发的多线程控制台贪吃蛇游戏源码解析