FPGA实现的六路抢答器设计与计时功能

版权申诉

190 浏览量

更新于2024-06-25

1

收藏 324KB DOC 举报

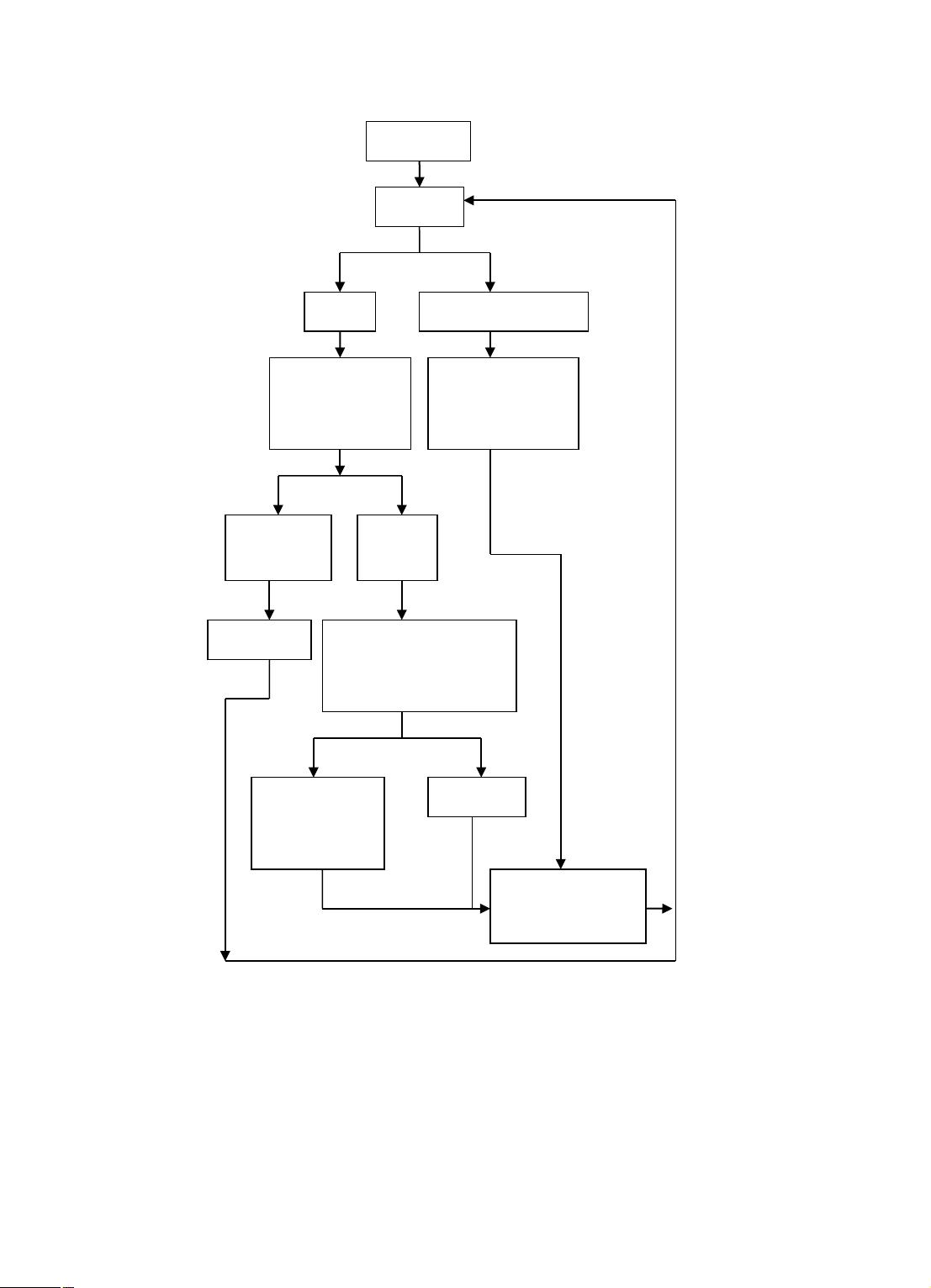

"基于FPGA的电子抢答器设计文档主要介绍了如何利用现代电子技术,特别是FPGA(Field-Programmable Gate Array)技术来构建一个高效、可靠且功能丰富的电子抢答系统。该设计旨在解决传统抢答器存在的制作复杂、可靠性低以及使用频率不高等问题。"

在本文档中,作者首先指出抢答器在各类知识竞赛中的应用,但同时也指出现有抢答器存在的不足,如制作复杂、可靠性低等。为了解决这些问题,作者提出了一种基于FPGA的新型抢答器设计方案。

该设计的核心是采用AT89C51单片机作为控制单元,结合外围接口设备,实现抢答系统的计时与控制功能。AT89C51是一款常见的微控制器,具有内置的定时器/计数器,可以用于精确的计时和计数任务。通过软件和硬件的协同工作,系统能够准确地进行计时,并通过LED数码管实时显示剩余时间。

设计的关键特性包括:

1. 六路抢答:系统支持六个参赛队伍同时抢答,确保公平竞争。

2. 可设定限时回答:允许用户在1-99秒范围内设定抢答和回答问题的时间。

3. 抢答有效性判断:只有在主持人启动抢答后,选手的抢答操作才会被认可,提前抢答视为无效。

4. 显示功能:数码管不仅能显示时间,还能指示有效和无效抢答的选手。

5. 音乐提示:正确的抢答和按键操作会触发音乐提示,增加比赛的趣味性。

6. 自动复位:抢答和回答时间结束后,系统自动复位,准备下一轮比赛。

7. 按键锁定:在有效状态下,防止非法按键干扰比赛进程。

此外,文档还可能涉及了FPGA在系统中的作用,FPGA的优势在于其可编程性,可以根据需求灵活配置逻辑功能,提高系统的灵活性和效率。作者可能详细介绍了如何使用FPGA实现抢答逻辑,以及如何与单片机进行通信。

关键词:AT89C51单片机,LED数码管显示,抢答器计时,报警功能。这些关键词揭示了设计的关键技术和功能,有助于读者快速理解设计的核心内容。

这份基于FPGA的电子抢答器设计文档深入探讨了如何利用现代电子技术构建一个高效、可靠且具有用户友好的特性的抢答系统,不仅满足了竞赛的需求,也提升了比赛的体验和公平性。

122 浏览量

268 浏览量

2024-11-10 上传

2024-11-10 上传

2024-11-10 上传

2024-11-09 上传

2024-11-11 上传

2024-11-03 上传

omyligaga

- 粉丝: 97

- 资源: 2万+

最新资源

- 20210315-秒针系统-互联网行业:2020中国异常流量报告.rar

- project

- vant-vue-cropper-h5.rar

- iOS 17.0.3 镜像包

- 基于C语言实现喇叭发声原理(含源代码+使用说明).zip

- 破折号按钮:小型Node.js服务器,对WiFi网络上的Amazon Dash按钮做出React

- 多峰对齐框架:MAF的实现:多峰对齐框架

- 毕业答辩合集1.rar

- Jimmu---Resturaunt-Concept

- 艾讯科技 Standard BIOS.zip

- 20200918-头豹研究院-2019年中国云通信行业概览.rar

- 64个基础图标 .sketch .xd .svg .png素材下载

- apiprodutos

- FaolFuqarolar后台

- 基于HTML实现影音娱乐网站_阿波罗DJ程序 5.1 美化简洁版_abl_dj(HTML源码+数据集+项目使用说明).rar

- soft_contrastive_learning:此存储库包含我们NeurIPS 2020出版物“用于视觉本地化的软对比学习”的代码。