VHDL设计的FPGA函数信号发生器及其应用

需积分: 11 183 浏览量

更新于2024-07-29

收藏 2.54MB DOC 举报

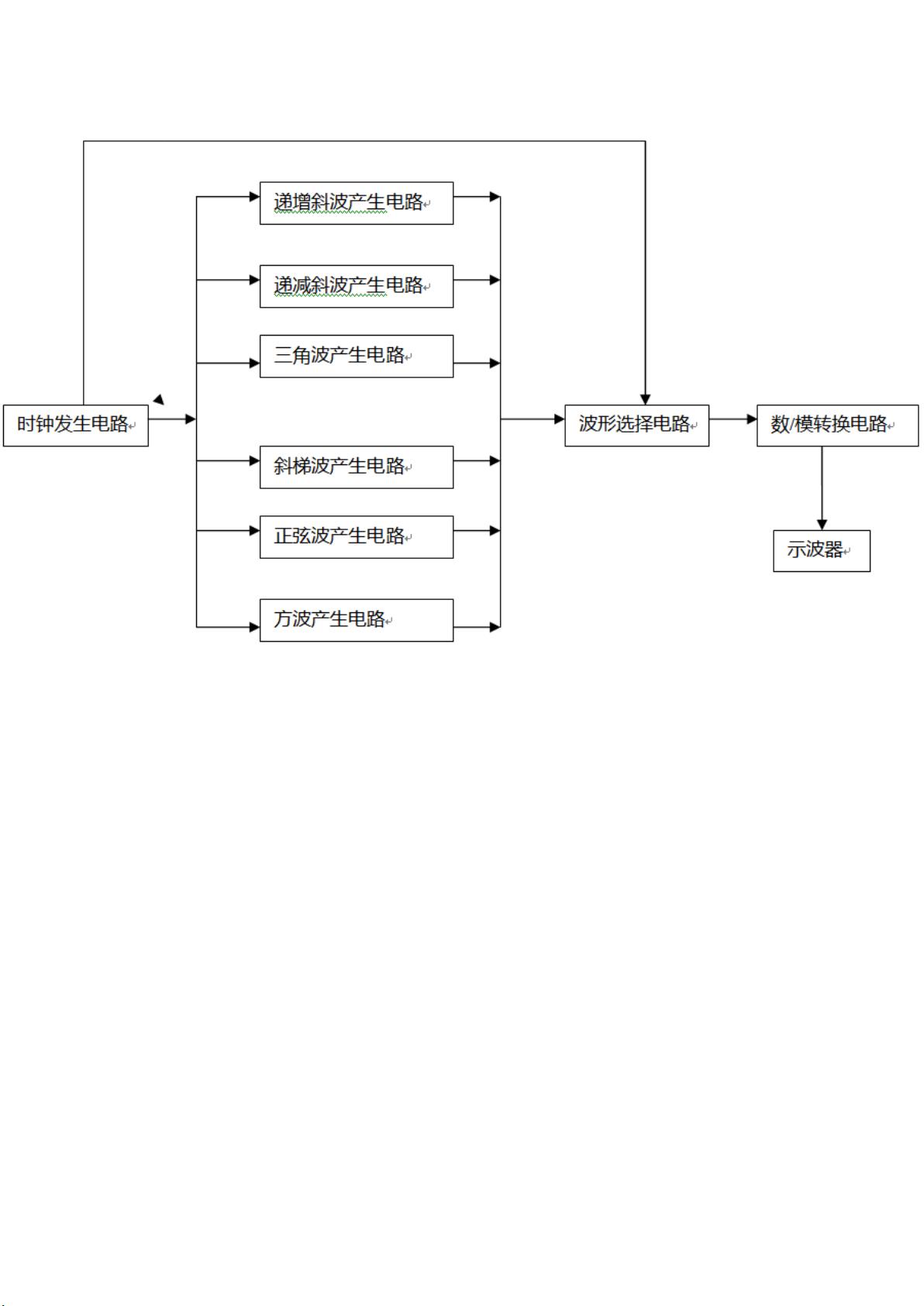

基于FPGA的函数信号发生器设计是本学期的EDA实验项目,作者江涛来自信息科学与工程学院电信09级,旨在采用VHDL语言构建一个功能全面的信号源。该信号发生器的核心目标是满足生产实践和科技领域的多样化波形需求,如正弦波、方波、三角波、锯齿波和阶梯波,同时具备灵活的波形选择功能。

设计过程采用了Altera公司的Quartus II软件,这是一款高度集成的可编程逻辑设计工具。Quartus II以其用户友好的界面、易用性和多功能性而闻名,它支持多种硬件描述语言(如Verilog HDL、AHDL和VHDL),允许设计师从原理图、结构框图或高级编程语言角度描述电路。通过该软件,设计者能够实现波形生成模块的描述和实现,进行电路设计、逻辑综合、布局布线以及功能和时序仿真的全流程工作。

波形产生模块和波形选择模块是设计中的关键组成部分,前者负责生成各种特定的波形,后者则提供了灵活的波形选择机制,使用户可以根据实际需要选择输出的波形类型。整个设计的目标不仅是产生标准波形,还要求输出质量和稳定性得到提升,包括频率范围宽广、频率稳定度高、准确度强以及分辨率优良。

本文的创新之处在于将现代电子测量对信号发生器的要求与EDA技术相结合,不仅提升了设备的实用性,也展示了VHDL在硬件描述中的高效性和灵活性。通过完成这个项目,学生不仅锻炼了VHDL编程技能,还加深了对FPGA工作原理和Quartus II工具的理解,为未来的电子设计职业奠定了坚实的基础。

2011-04-16 上传

2010-05-01 上传

2008-12-17 上传

2021-07-13 上传

2013-05-10 上传

2021-07-13 上传

yanzi0924

- 粉丝: 0

- 资源: 4

最新资源

- GTScriptableVariable:基于Ryan Hipple的可脚本化变量谈论具有可脚本化对象的游戏体系结构

- notifications-tutorial:Android中用于通知的示例应用

- connecticut_maps:用于创建康涅狄格州可自定义地图的脚本

- discovery_board_api:探索板 API

- MinimalSeedSets:从宏基因组学样品中确定最少的种子集

- 2020成都薪酬标准指南精品报告2020.rar

- third-party-payment:集成主流的第三方支付(支付宝支付,微信支付,银联支付,京东支付)

- ciu-trabajo集成商

- sbt-scoverage-multiproject-sample:sbt-coverage-multiproject-sample

- Messengo-crx插件

- WatchVideo:我曾经说过持之以恒,就是要坚持下去,不要在半途而废了。哪怕一天一天的积累,我希望一天会看到像种子一样的结果

- 易语言-[JSON解析与生成 / 哈希表]Quick And Simple EC

- OnlineCourses

- design-patterns:Java,OOP基础和原理中的设计模式示例

- 迷宫游戏

- java毕业设计——java基于蚁群算法路由选择可视化动态模拟系统的的设计与实现(论文+开题报告+翻译+外文翻译).zip