使用Formality进行形式验证:从RTL到门级的指南

需积分: 3 43 浏览量

更新于2024-06-16

收藏 4.47MB PDF 举报

"Formality是Synopsys提供的一款强大的形式验证工具,用于在数字集成电路设计流程中确保设计的正确性。形式验证通过对比不同阶段的设计在逻辑上的等价性,来验证电路的功能,避免传统仿真器的局限性,提高验证效率,并减少设计周期。Formality可以用于检查RTL设计与门级网表的一致性,以及门级网表在经过扫描链和JTAG链插入后的功能一致性。在提供的教程中,展示了如何使用Formality进行RTL与GATE网表的对比验证,包括设置参考设计和实现设计,以及通过图形用户界面进行操作的步骤。"

Formality作为形式验证的核心工具,其主要功能是对比不同阶段的设计,确保设计在功能上的等效性。这包括:

1. **检查RTL与GATE网表**:验证 RTL 源代码(如 fifo.v)和综合后的门级网表(如 fifo.vg)之间的功能一致性。在这一过程中,首先将RTL源代码设置为参考设计,然后将门级网表设置为实现设计。

2. **检查GATE网表与扫描链的GATE网表**:当设计中包含扫描链时,Formality可以用来验证扫描链插入后的门级网表(如 fifo_with_scan.vg)与未插入扫描链的版本是否一致。

3. **检查带有JTAG链的GATE网表**:对于需要JTAG链的测试和调试,Formality还可以比较带有JTAG链的门级网表(如 fifo_with_scan_jtag.vg)与扫描链版本的门级网表,确保它们在功能上等价。

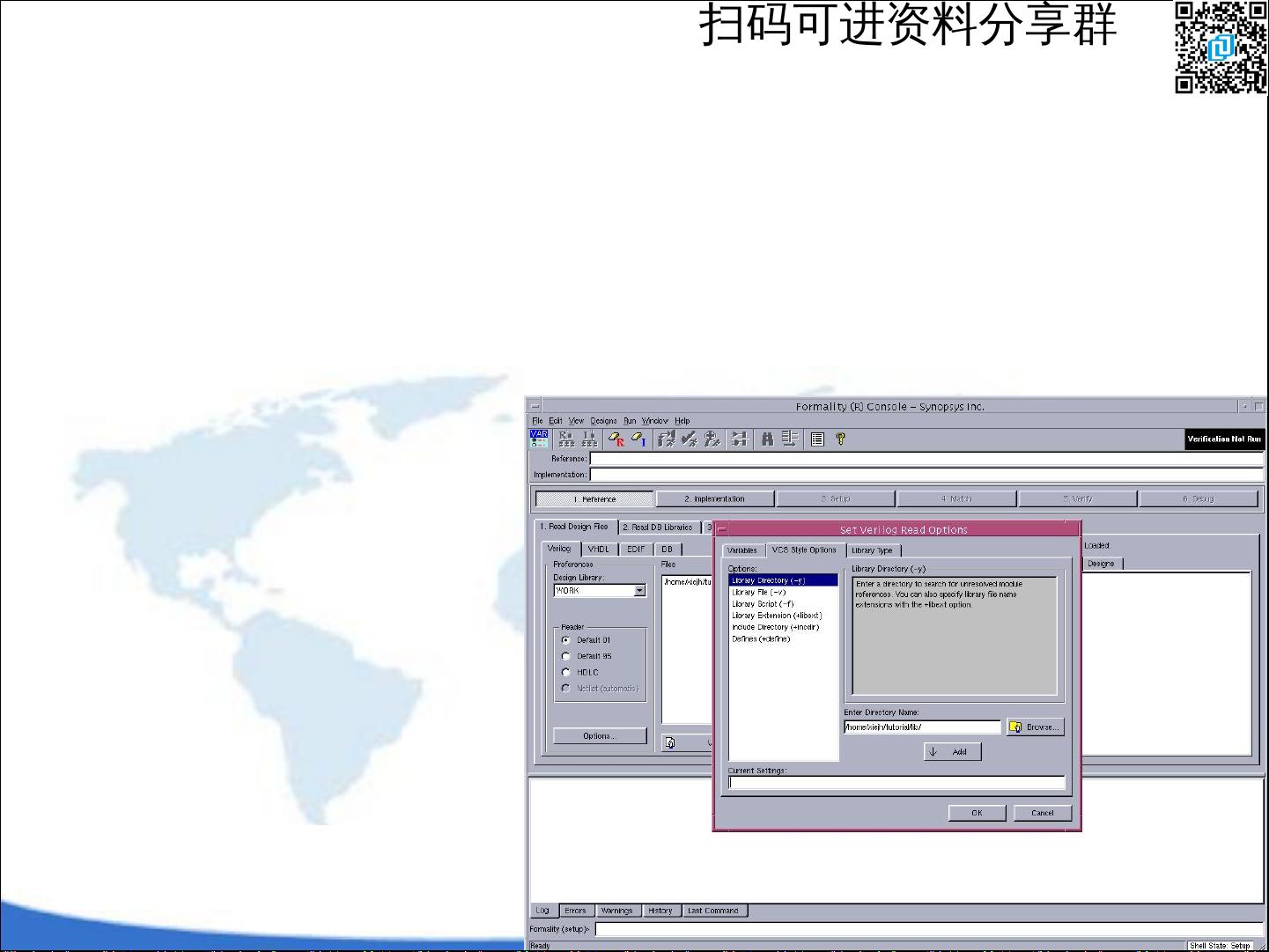

在实际操作中,用户可以通过Formality的图形用户界面(GUI)进行如下步骤:

- 启动Formality(fm或formality命令)。

- 使用`reference`按钮设置参考设计,读取Rtl目录下的Verilog源文件。

- 使用`option`按钮设置Verilog的读取选项,指定Design Compiler的安装目录。

- 设置实现设计,读取门级网表。

- 进行一致性检查,Formality会自动分析两个设计的逻辑等价性,并报告任何发现的差异。

通过这个教程,用户能够熟悉Formality的基本用法,进一步掌握数字集成电路设计中的形式验证技术,这对于确保数字芯片后端设计的正确性和可靠性至关重要。在不断增长的设计复杂度和验证需求面前,形式验证成为不可或缺的验证手段,Formality则提供了高效且全面的解决方案。

2021-03-04 上传

2023-06-23 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-10-12 上传

2023-06-02 上传

stefen_hou

- 粉丝: 216

- 资源: 4

最新资源

- Cucumber-JVM模板项目快速入门教程

- ECharts打造公司组织架构可视化展示

- DC Water Alerts 数据开放平台介绍

- 图形化编程打造智能家居控制系统

- 个人网站构建:使用CSS实现风格化布局

- 使用CANBUS控制LED灯柱颜色的Matlab代码实现

- ACTCMS管理系统安装与更新教程

- 快速查看IP地址及地理位置信息的View My IP插件

- Pandas库助力数据分析与编程效率提升

- Python实现k均值聚类音乐数据可视化分析

- formdotcom打造高效网络表单解决方案

- 仿京东套餐购买列表源码DYCPackage解析

- 开源管理工具orgParty:面向PartySur的多功能应用程序

- Flutter时间跟踪应用Time_tracker入门教程

- AngularJS实现自定义滑动项目及动作指南

- 掌握C++编译时打印:compile-time-printer的使用与原理