MDIN-200

Datasheet Version 0.4

Macro Image Technology, Inc. Confidential

9

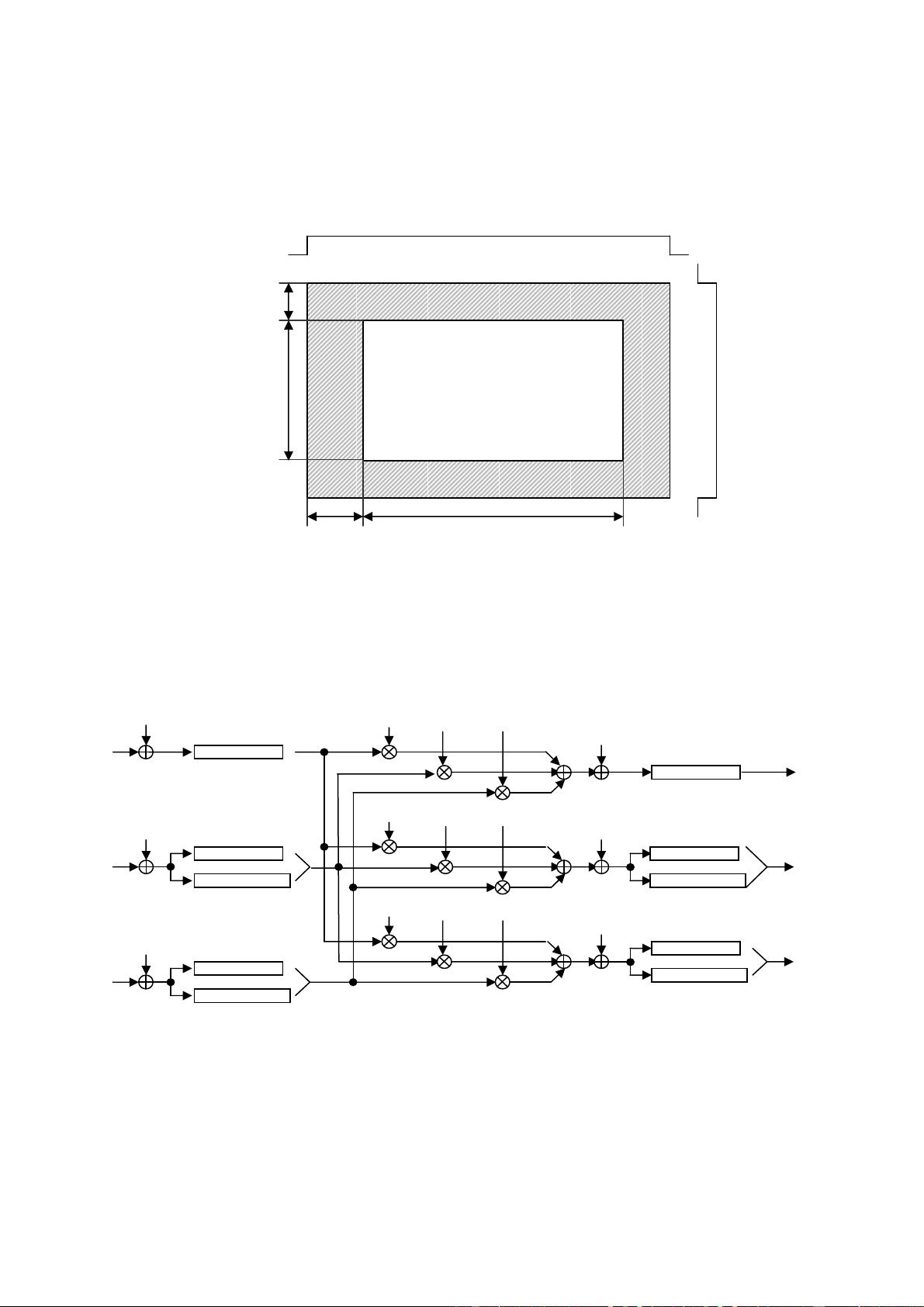

control register for preprocessing of video data value. The coefficient registers of csc_f_coef0, csc_f_coef1, …,

csc_f_coef7 and csc_f_coef8 in the input block are user programmable. All input components and output components

can be added or substracted by setting csc_f_offset_y, csc_f_offset_cb, csc_f_offset_cr, csc_f_offset_g,

csc_f_offset_b and csc_f_offset_r registers as user defined values. And it is possible to make the input and output

value clipped to a certain range. One way is clipping for Cb, Cr, B, R to be ranging from 0 to 1023 and the other is from -

512 to 511. User can select each clipping mode for each Cb, Cr, B, R. And Y and G signals are clipped to be ranging

from 0 to 1023. The CSC can be bypassed by setting csc_f_bypass bit of csc_f_control register. All the coefficient and

offset registers are 12-bit 2’s complement values, and 512 corresponds to 1.0 (unity).

The register values in the following example can be used to convert RGB video to the ITU-R BT.601 YCbCr format. The

RGB and YCbCr data are assumed a range of 0 to 1023. If the range is 64 to 940, the coefficient and offset registers

should be adjusted properly.

R0.172B0.511G0.339Cb

×+×−×−=

×−×+×−=

csc_f_coef0 = 0x12D, csc_f_coef1 = 0x03A, csc_f_coef2 = 0x099

csc_f_coef3 = 0xF52, csc_f_coef4 = 0x106, csc_f_coef5 = 0xFA8

csc_f_coef6 = 0xF25, csc_f_coef7 = 0xFD6, csc_f_coef8 = 0x106

csc_f_offset_g = 0x000, csc_f_offset_b = 0x000, csc_f_offset_r = 0x000

csc_f_offset_y = 0x000, csc_f_offset_cb = 0x200, csc_f_offset_cr = 0x200

csc_f_control = 0x1F8

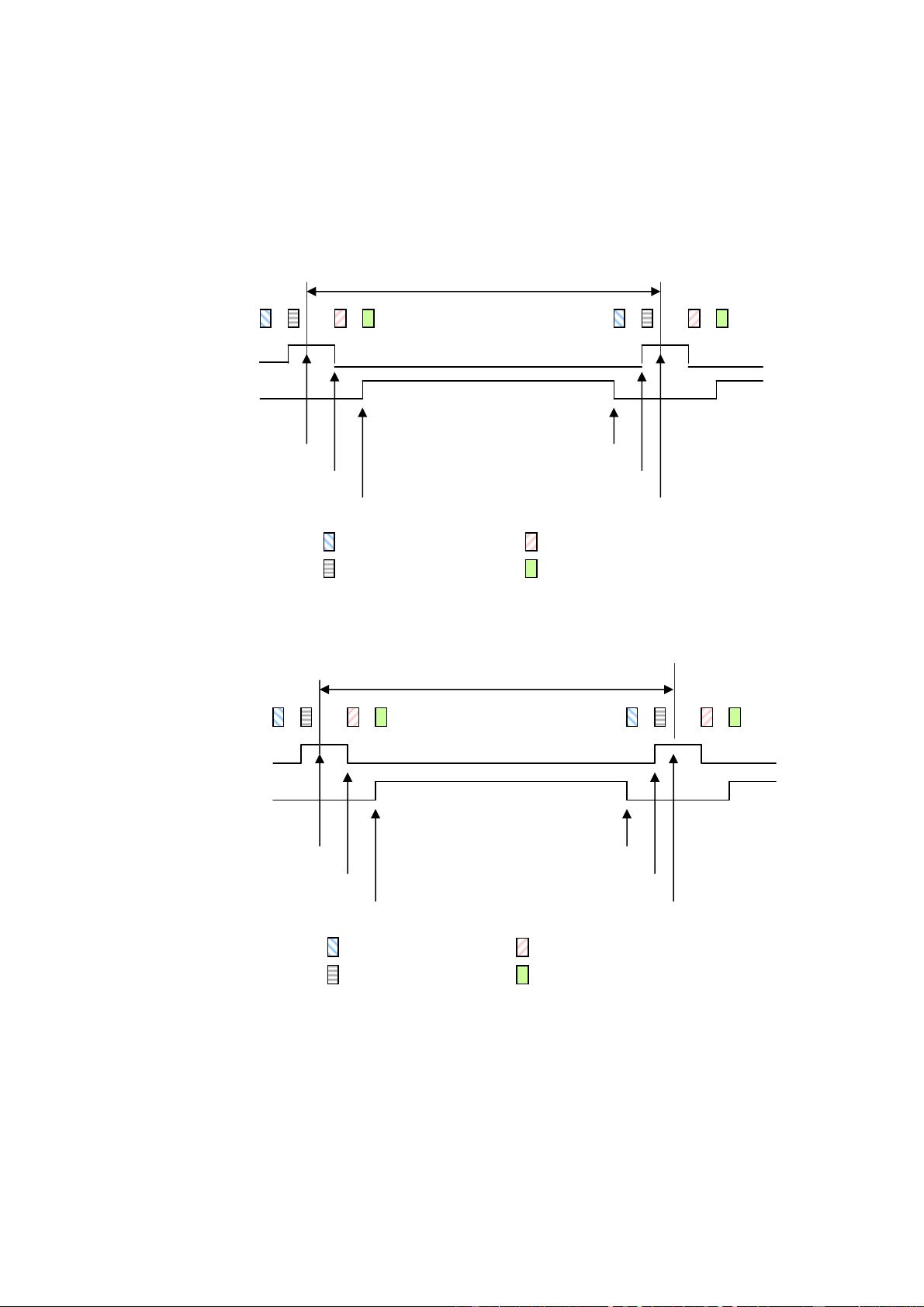

2.5 Auto Detection and Compensation of Input Video Sync

MDIN-200 provides input auto detection capability. Auto detection of the follwing parameters is supported - horizontal

sync period, horizontal size or the number of horizontal pixels for both the high and low period of horizontal sync, vertical

size or the number of vertical lines for both high and low period of vertical sync, and scan type. Auto detection on the

input port B is not necessary since it always receives video data with embedded timing references.

MDIN-200 also detects the existence of video sync signal and the change in the horizontal and vertical sync period. Auto

detection of sync existence or sync change is always performed and the other auto detection features are performed by

setting in_detect_en register. The results of auto detection are stored in input status registers (in_sync_lost, in_hsync,

in_scan_i, in_hsync_high, in_hsync_low, in_vsync_high, in_vsync_low) and they can be read and used by an

external host processor for the detection of exact input video format.

MDIN-200 supports composite sync input. It can extract the hsync and vsync from the composite sync signal which can

be obtained by slicing the bi-level or tri-level sync tips of the input video signal. MDIN-200 can receive a composite sync

signal through HACTIVE_A pin by setting in_sync_ctrl register.

And MDIN-200 can extract the sync information even though the input sync signals are in non-standard format. When the

timing of vsync-transition to hsync is different from the standard timing it can be compensated by setting

vsync_forced_rising_a register. In this case, the horizontal total size of input signal needs to be specified in

in_fieldid_ctrl register. And as prevention against unstable vsync-rising, the internal vsync signal can be forced to rise at

any position by setting vsync_forced_rising_a register. in_sync_sel register determines which input sync will be

selected between the original and compensated input sync signals.

2.6 Front Noise Reduction Filter

MDIN-200 has two blocks to perform noise reduction function. The first block is the front noise reduction filter and the

second block is the post noise reduction during deinterlacing process, i.e. 3D noise reduction. The front noise reduction

filter is a one dimensional filter for input video signal. Its characteristics are programmable. The information from this filter

is also used in deinterlacing process. The front noise reduction filter has two types of filter - median filter and FIR low

pass filter. The median filter has 3 taps and the FIR low pass filter has 15 taps and the coefficients are programmable.

The difference between input and output of the median filter is stored in median_flt_difference register and the

difference between input and output of the FIR low pass filter is stored in nr_flt_difference register. The difference

valuses are used in post noise reduction of deinterlacing process to reduce artifacts caused by noise, and user can

select which result to be used by setting noise_reduction_flt_diff_sel register. This front noise reduction filter,

alternatively, can be used as anti-aliasing filter. When the input video is scaled down in the horizontal direction this filter