同步时序逻辑电路详解:结构、输出与分类

需积分: 35 44 浏览量

更新于2024-07-22

收藏 3.43MB PPT 举报

同步时序逻辑电路是计算机硬件设计中的一种关键组成部分,它区别于组合逻辑电路,主要在于其输出不仅取决于当前的输入信号,还与电路过去的状态密切相关。以下是关于同步时序逻辑电路的详细解读:

1. **时序逻辑电路概述**:

- 组合逻辑电路:这类电路的输出在任何给定时刻都是由当时的输入信号决定的,不考虑电路先前的状态。例如,译码器、全加器和数据选择器等电路属于组合逻辑。

- 时序逻辑电路:与组合逻辑不同,时序逻辑电路如触发器、寄存器、计数器和移位寄存器等,它们的输出不仅受当前输入信号影响,还受到电路内部存储单元(如触发器)过去状态的影响。这是通过时钟信号来实现状态更新的,使得电路能够执行顺序操作和存储信息。

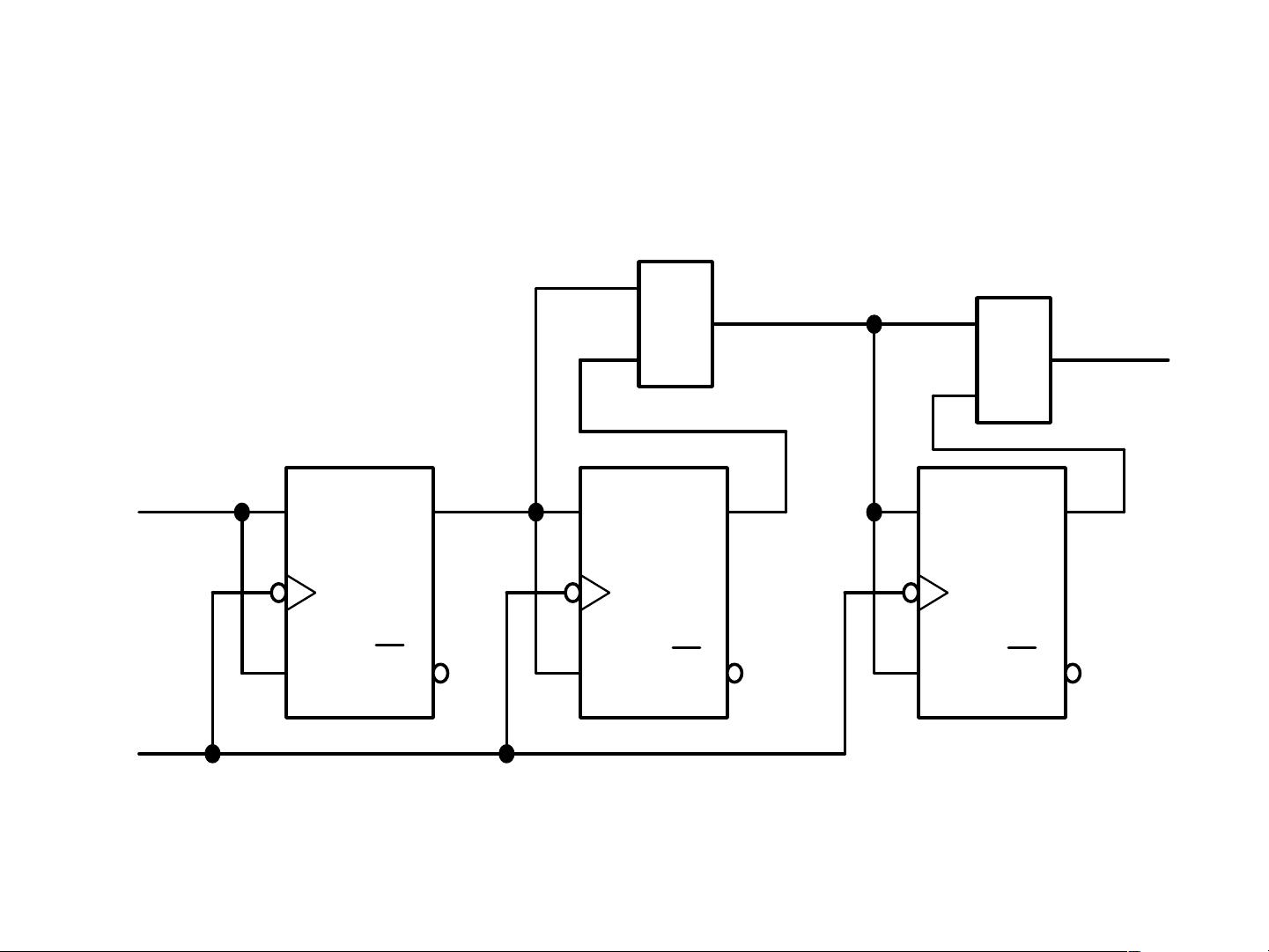

2. **时序电路结构图**:

时序逻辑电路通常包含输入端口(如x1, x2, xn)、输出端口(如Y1, Y2, Ym)、内部触发器或寄存器(如q1, qk, z1, zr),以及可能的控制逻辑(如f, g, h)。电路通过时钟信号(一般用clk表示)进行状态转换,每个时钟周期完成一次状态更新。

3. **电路组成**:

- 触发器:作为时序逻辑的基本元件,触发器结合了组合逻辑和记忆功能,具有反馈路径,如D触发器、JK触发器、T触发器等,它们的状态转移由驱动方程和状态方程共同确定。

- 输出方程:描述了电路的输出与输入和触发器状态的关系,如Y = f(q1, qk, ..., xn)。

- 驱动方程和状态方程:分别表示触发器的次态和现态,驱动方程定义了触发器状态的更新条件,状态方程则反映触发器在下一个时钟周期后的状态。

4. **分类**:

- 同步时序电路:所有触发器共享同一个时钟源,状态随时钟脉冲变化而同步更新。这种电路的时序关系清晰,易于设计和分析,常见于计算机CPU的时钟系统和数据处理部分。

- 异步时序电路:各触发器有自己的独立时钟源,不依赖于全局时钟,这种电路通常更复杂,因为需要处理不同时钟之间的同步问题,适用于对响应时间要求不高的应用。

同步时序逻辑电路在计算机系统中扮演着核心角色,通过精确的时钟控制实现了数据的存储和处理,对于理解和设计高效、稳定的电子设备至关重要。理解其基本原理、结构和分类对于从事硬件开发的工程师来说是必不可少的基础知识。

636 浏览量

2010-06-29 上传

272 浏览量

328 浏览量

515 浏览量

点击了解资源详情

点击了解资源详情

qq_27956793

- 粉丝: 0

- 资源: 2

最新资源

- 易语言源码文件属性对话框模块源码.rar

- moneyConvert

- digipost-api-client-java-5.0.zip

- labview控制,如何给c语言源码做个界面,c语言

- 64个24px图标 .sketch素材下载

- sdl-helper-cpp:一种使SDL更轻松,更快速的方法

- 14.0(FromXcode_12_beta_3_xip).zip

- homebrew-redis-cli:通过homebrew安装redis-cli

- 安卓Android二次元社区论坛bbs绘画app可导入AndroidStudio

- Universal-CollapsingTabLayout,折叠带Tablayout的工具栏布局。.zip

- blekso.github.io:米哈伊尔·伊施特万(MihaelIštvan)

- Baekjoon-Algorithm:算法研究

- 易语言枚举注册表

- opengrok_tool.zip

- Cross-platform-programming-Lab1

- matlab代码sqrt-machine_learning_PCA:基于Matlab的PCA