使用Synplify设计安全Verilog状态机

需积分: 49 117 浏览量

更新于2024-09-15

收藏 246KB PDF 举报

"这篇文档是关于在Verilog中设计安全状态机的指南,特别是强调了在使用Synplify工具时的注意事项和优化方法。"

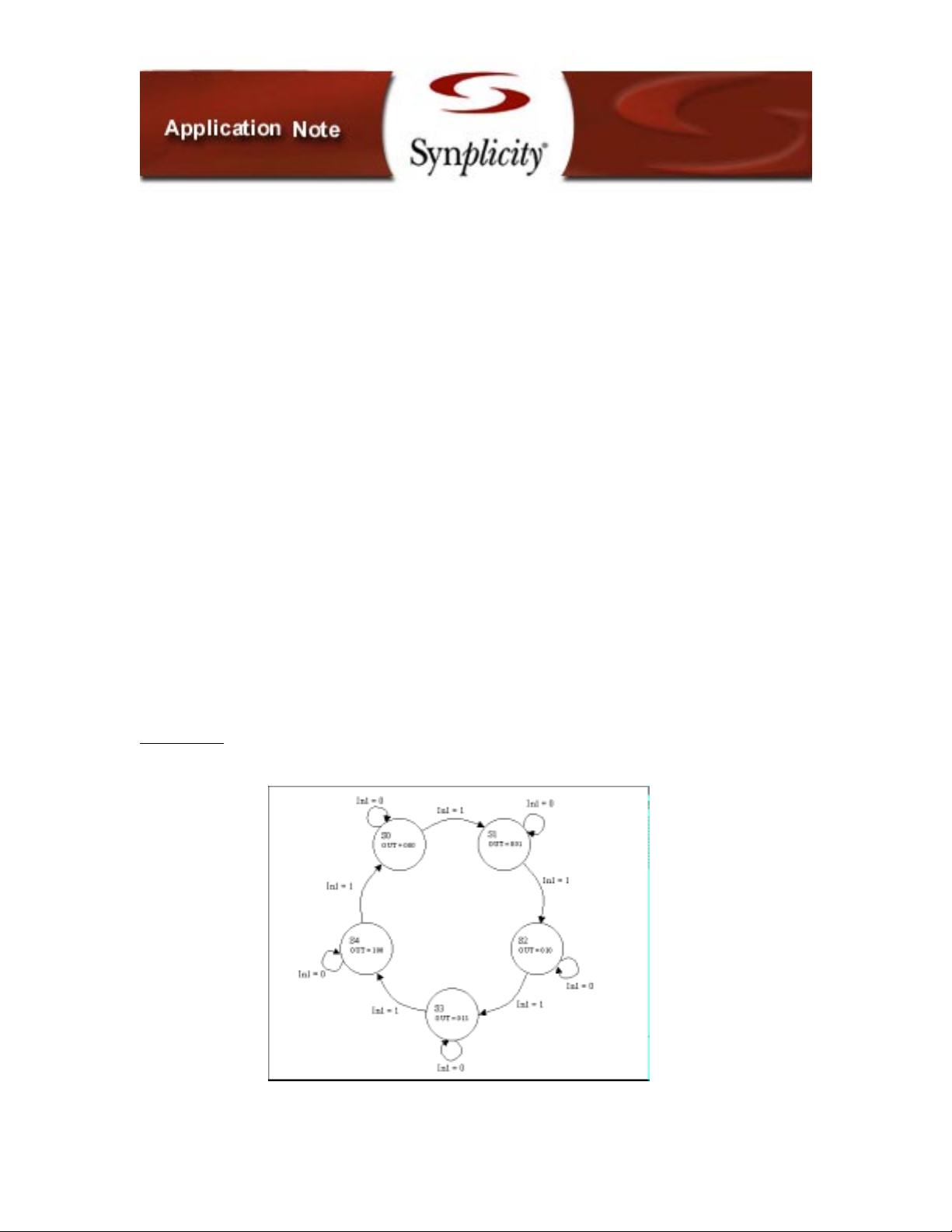

在Verilog中,状态机是一种常见的设计模式,用于控制系统的顺序行为。状态机的设计通常包括定义状态编码、状态转换以及输入和输出的行为。在给定的代码示例中,展示了一个基本的同步状态机(FSM1)设计,它使用了一种称为“onehot”编码的方式,这意味着只有一个状态变量为1,其余为0,这可以减少状态之间的转换错误。

状态机的关键组成部分包括:

1. **状态变量(state)**:在例子中,`state`是一个3位的寄存器,用于存储当前状态,使用宏定义`s0`到`s4`表示不同的状态。

2. **下一状态变量(next_state)**:用于存储在下一个时钟沿将要转变到的新状态。

3. **时钟(clk)**:状态机的同步信号,通常在时钟的上升沿进行状态转移。

4. **复位(rst)**:用于初始化状态机,当复位信号有效时,状态机返回初始状态`s0`。

5. **输入(in1)**:根据输入信号触发状态转换。

6. **输出(out1)**:根据当前状态产生相应的输出。

状态机的逻辑通常分为两部分:

- **边缘检测(edge detection)**:`always @(posedge clk or posedge rst)`块检测时钟边沿或复位信号,进行状态更新。

- **状态决策(state decision)**:`always @(state or in1)`块包含一个case语句,根据当前状态和输入决定下一个状态。

Synplicity的Synplify工具提供了一项强大的有限状态机(Finite State Machine, FSM)编译功能,它可以自动识别状态机,并以顺序、格雷码或one-hot编码实现。更重要的是,它能进行可达性分析,确定所有可能到达的状态,优化掉那些无法达到的状态和转换逻辑,从而产生高度优化的状态机实现。

然而,在某些特殊情况下,如在高辐射环境下运行的电路(如太空应用),不可达状态的删除可能是不可接受的。因为辐射可能导致存储元件(如触发器)的翻转,如果状态寄存器中的单个位发生变化,可能会导致未预期的行为。因此,在这些场景下,保留所有状态以确保系统鲁棒性是至关重要的。

设计安全状态机时,需要考虑以下几点:

- **状态编码的稳定性**:使用one-hot编码可以减少状态误触发的可能性,但可能增加硬件资源。

- **状态转移的完整性**:确保每个状态都有明确的进入和退出条件,避免出现悬挂状态。

- **故障恢复机制**:添加检测和恢复逻辑,以处理由于外部干扰或内部错误导致的不期望状态。

- **测试与验证**:进行充分的仿真和形式验证以确保状态机的正确性。

- **健壮性设计**:考虑在恶劣环境下的设计,如使用双冗余状态寄存器或错误检测/校正编码。

设计安全的Verilog状态机不仅涉及编码方式的选择,还应考虑其在特定应用场景下的可靠性需求和可能的故障条件。在利用Synplify等工具进行优化时,需谨慎权衡功能完整性和资源效率。

2021-07-13 上传

2009-09-21 上传

2021-07-13 上传

点击了解资源详情

2010-07-12 上传

2022-09-20 上传

2020-07-03 上传

2012-05-16 上传

2021-09-15 上传

thunderwalk

- 粉丝: 0

- 资源: 3

最新资源

- codezhifty

- jahresmeisterschaft_fsb:该程序用于评估射击俱乐部“FeldschützengesellschaftBolligen”的年度冠军(Jahresmeisterschaft)

- fm-contour-mapper:美国调频频谱互动图

- r4ioos:R的自动化和报告演示

- 记录用python实现的机器学习算法.zip

- DataMiningAlgorithms

- TodoList:这是一个包含搜索栏的待办事项列表

- 小轩菜单工具易语言源码-易语言

- POLS6480-Fall2020-UH-家庭作业

- Python库 | requests_ntlm-1.1.0-py2.py3-none-any.whl

- DailyCodingProblem

- Maze_Java

- 记录学习Python Web 框架 Flask的代码.zip

- FizzBuzzStrategy:具有Strategy模式的FizzBuzz实现

- PasswdSafe-开源

- node-ruby-sass