Xilinx 7Series PCIe IP核用户手册

需积分: 13 118 浏览量

更新于2024-07-20

收藏 15.13MB PDF 举报

"Xilinx PCIe IP核的用户手册,详述了在7系列FPGA中集成的PCI Express v1.7接口的功能、设计指南、Vivado设计套件的使用方法以及约束设置等关键内容。"

Xilinx公司的7系列FPGA集成的PCI Express (PCIe) IP核是一个高性能、低延迟的解决方案,适用于需要高速数据传输的应用。该IP核遵循PCI Express v1.7标准,提供了全面的产品规格和设计指导,以帮助开发者在FPGA中实现高效的PCIe接口。

**章节1:概述**

这部分介绍了PCIe IP核的主要特性,包括其在各种应用中的用途,如数据中心、网络设备、存储系统等。同时,它还提供了IP的授权和订购信息,这对于商业使用和项目规划至关重要。

**章节2:产品规范**

- **标准合规性**:确保IP核符合PCI Express规范,包括电气、协议和功能标准。

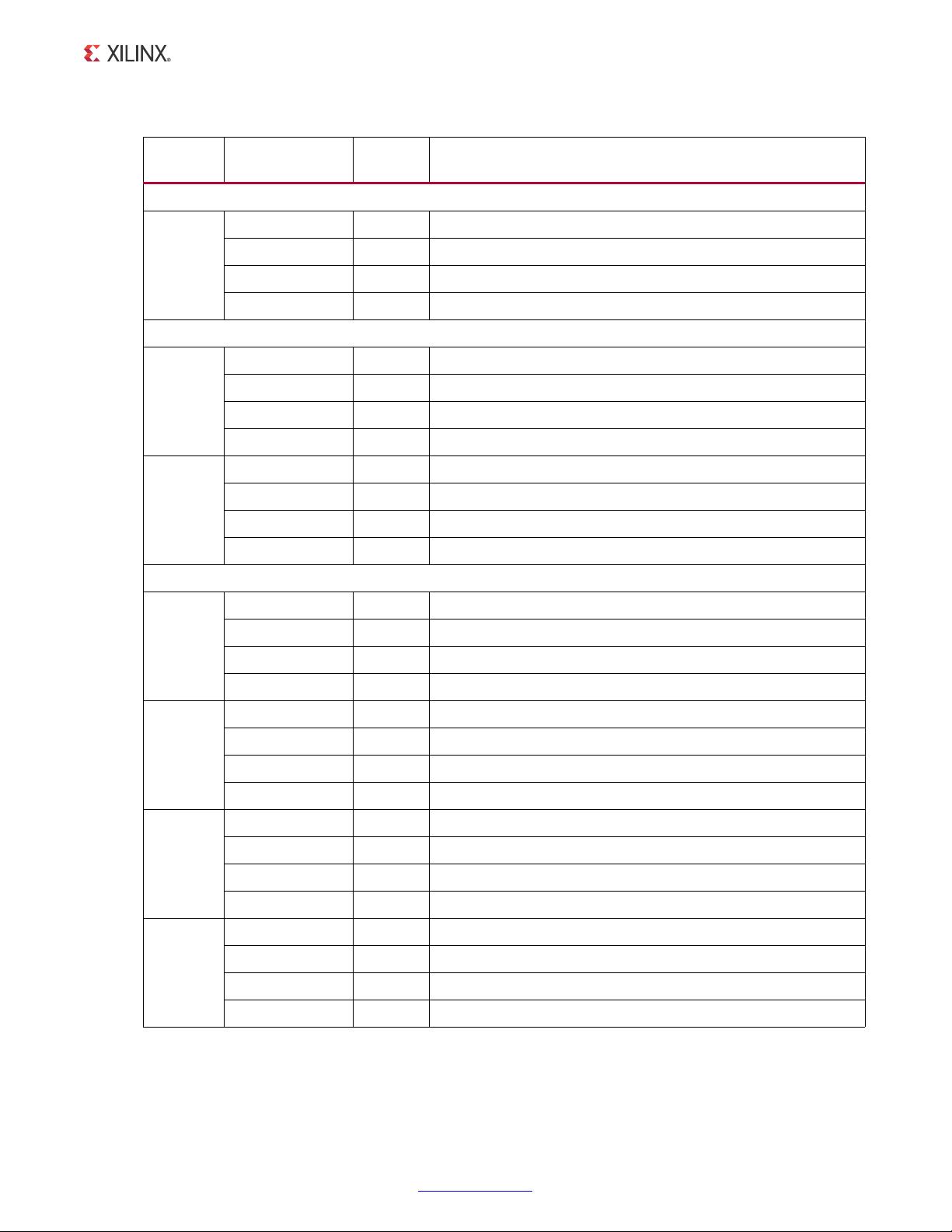

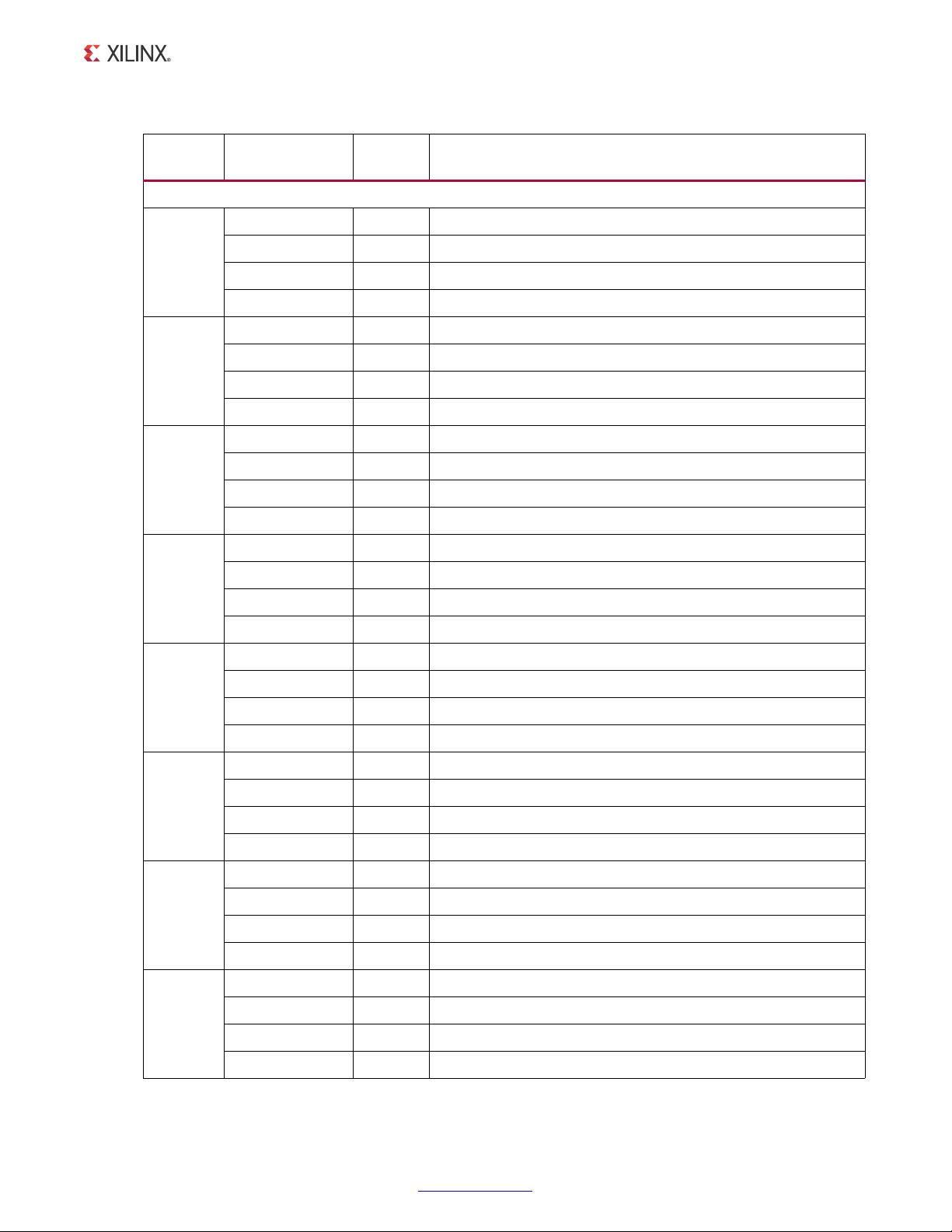

- **资源利用率**:详细列出了在7系列FPGA中实现PCIe IP所需的逻辑资源,如逻辑单元(LUT)、分布式RAM(BRAM)和时钟资源等。

- **最小设备要求**:指明了支持此IP的最低FPGA型号要求。

- **可用的PCIe集成块**:描述了不同类型的PCIe端点(EP)和根端点(RP)配置。

- **核心接口**:包括事务接口和PCI配置空间,事务接口处理PCIe总线上的数据传输,而配置空间则定义了设备的配置选项。

**章节3:设计指南**

- **一般设计准则**:提供了关于系统级设计的建议,如时钟管理、复位策略和协议层的理解。

- **时钟**:详细阐述了时钟域跨越、同步和时钟质量的重要性。

- **复位**:讨论了不同类型的复位信号及其在PCIe IP中的应用。

- **协议层**:解释了PCIe协议的物理层、数据链路层和事务层的关键概念。

- **FPGA配置**:涵盖了如何将配置数据加载到FPGA中,以启用PCIe IP的功能。

**章节4:Vivado设计套件定制与生成**

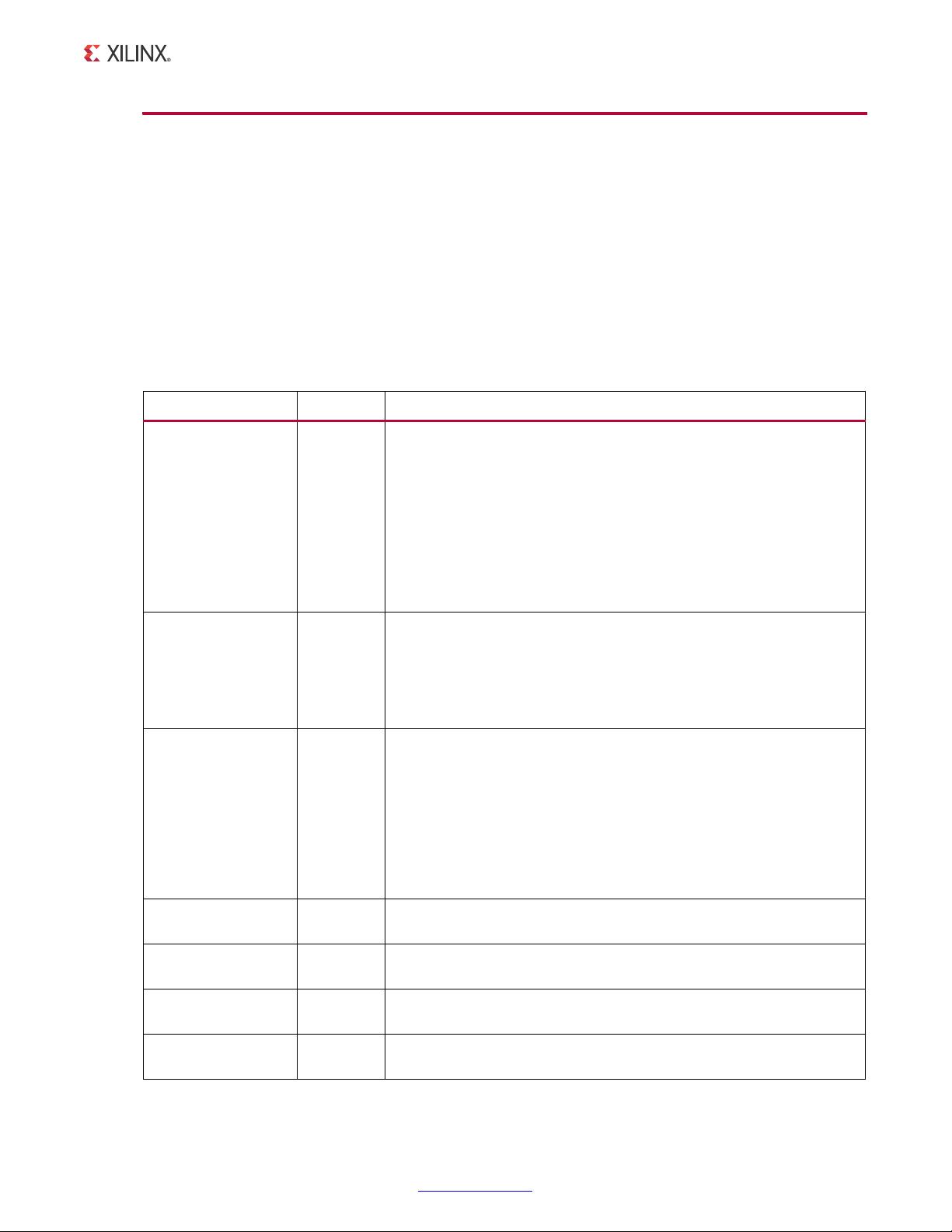

- **图形用户界面(GUI)**:介绍了使用Vivado工具自定义和生成PCIe IP核的过程,包括参数设置和配置选项。

- **输出生成**:说明了如何生成IP核的硬件描述语言(HDL)代码和相关文件,以便于集成到更大的系统设计中。

**章节5:约束设置**

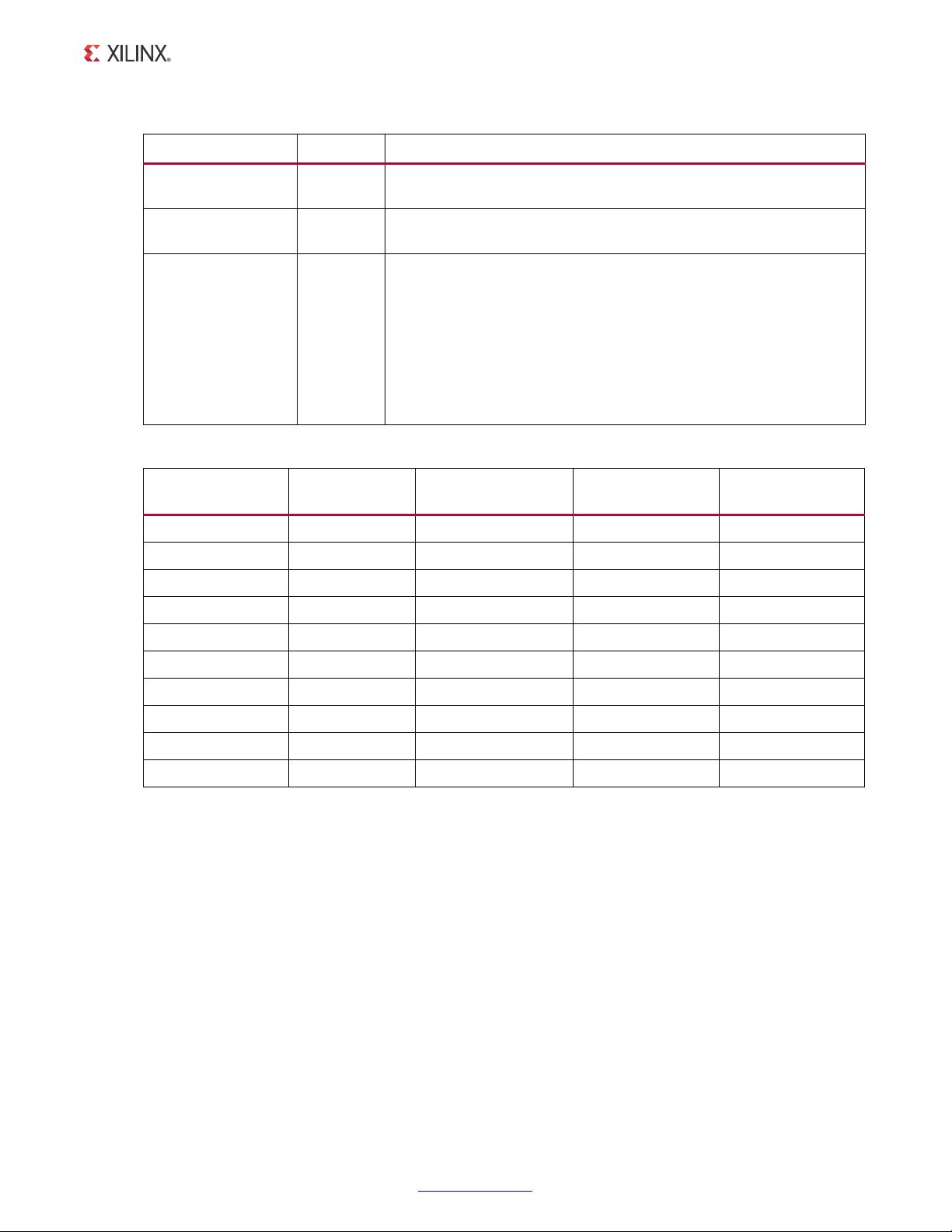

- **所需约束修改**:详细说明了对Xilinx约束文件(UCF或XDC)的必要改动,以确保IP核正确运行。

- **设备、封装和速度等级选择**:指导用户根据目标FPGA的特性进行选择。

- **IP I/O分配**:说明了如何指定PCIe接口的I/O引脚。

- **核心物理约束**:涵盖了布局和布线的指导,确保满足物理设计规则。

- **核心时序约束**:提供了解决时序收敛问题的技巧和策略。

"xilinx pcie ip doc" 提供了全面的信息,不仅涵盖了PCIe IP核的技术规格,还包括了在Vivado环境中进行设计、定制和实现的详细步骤,是开发基于Xilinx 7系列FPGA的PCIe系统的重要参考文档。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-03-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

lylcan

- 粉丝: 0

- 资源: 5

最新资源

- Windows CE Programming [PDA][C++].pdf

- Wince深入浅出教程.pdf

- PlatformBuilderandEmbeddedVisualC++.pdf

- SQL语法参考手册,简单易用

- profiler使用大全

- ejb3.0实例教程.pdf

- 数据挖掘概念与技术Ed2

- Arm system developer's giude.pdf

- SVM Nice paper

- Spring开发指南(PDF)

- SQL Server 2005安装使用教程

- 需求分析的模板要的下

- VIM用户使用手册中文版

- Fedora10正式版完全安装教程.pdf

- 高速PCB设计指南高速PCB设计指南高速PCB设计指南

- zend framework 分页类