FPGA实现MIPS单周期处理器设计详解

版权申诉

"基于FPGA的MIPS单周期处理器的实现"

本文主要介绍如何基于FPGA(Field-Programmable Gate Array)实现一个基于MIPS架构的单周期处理器。MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集计算机(RISC)体系结构,以其高效能和简单的流水线设计而闻名。在FPGA上实现MIPS单周期处理器,可以让我们深入理解处理器的内部工作原理,并提供了一个实践硬件设计和验证的平台。

首先,文章提到了使用Vivado设计套件,这是由Xilinx公司推出的一个集成设计环境,旨在提高开发效率,缩短产品上市时间,并支持大规模的可编程系统集成。Vivado提供了从系统级设计到IC级设计的全套工具,包括设计输入、综合、仿真、实现和调试等功能。它特别强调了IP核的设计,允许用户快速构建和扩展复杂的设计。

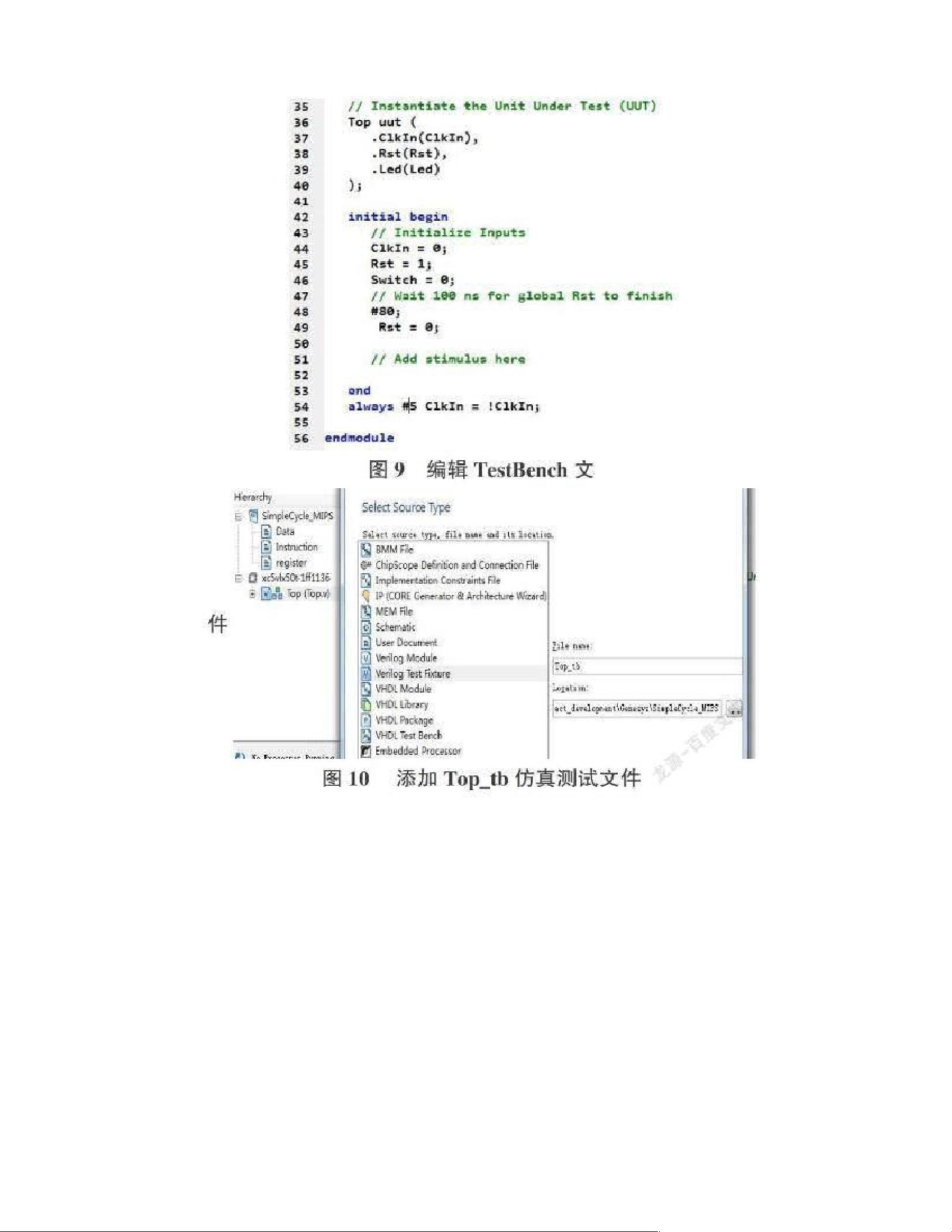

在创建新工程的过程中,开发者需要指定工程名称、存储路径以及FPGA型号(例如Nexys4-DDR),同时设定综合和仿真工具,选择Verilog作为描述语言。接着,通过Vivado界面,可以添加已经编写好的Verilog模块,如寄存器文件、符号扩展、数据内存、指令内存和算术逻辑单元(ALU)等关键组件,并定义顶层模块和控制逻辑。

编写Verilog代码是设计过程的核心。Verilog是一种硬件描述语言,它允许开发者以文本方式描述数字系统的结构和行为,既能够表示逻辑电路,也可以表达逻辑功能。与VHDL一起,Verilog是目前最广泛使用的两种硬件描述语言。

对于MIPS单周期处理器来说,其设计特点是所有操作在一个时钟周期内完成,简化了传统多周期处理器中的流水线延迟问题。这样的设计虽然牺牲了某些性能,但降低了硬件复杂性,使得理解和实现更为直观。处理器通常包括取指、译码、执行和写回等基本步骤,所有这些都在单个时钟周期内同步进行。

在Verilog代码中,开发者会详细描述每个模块的功能,例如ALU执行算术和逻辑运算,寄存器文件存储数据,指令内存存储程序指令,数据内存处理数据交换,以及控制单元根据指令解码结果生成合适的控制信号。通过仿真测试,验证设计是否正确实现了MIPS指令集,并在FPGA上下载验证,确保硬件能够正确执行预定的计算任务。

总结来说,基于FPGA的MIPS单周期处理器实现涉及到了硬件描述语言Verilog的使用,Vivado设计套件的工程管理,以及对MIPS处理器基本原理的理解。这一过程不仅锻炼了硬件设计技能,也为理解计算机体系结构提供了宝贵的实践经验。

2022-06-20 上传

2022-06-19 上传

2022-06-20 上传

227 浏览量

322 浏览量

2022-06-20 上传

3175 浏览量

G11176593

- 粉丝: 6927

- 资源: 3万+