5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A

ROM_LOC1_IN

ROM_LOC2_IN

HOST_AGT0_IN

IO_Mode_In

CFG_ID5

HOST_AGT1_IN

HOST_AGT2_IN

BOOTSEQ1_IN

SRDS_EN_IN

QE_PLL0_IN

QE_PLL1_IN

QE_PLL2_IN

QE_PLL3_IN

QE_PLL4_IN

QE_UCC_IN

TSEC1_WIDTH_IN

TSEC2_WIDTH_IN

TSEC1_PRTC0_IN

TSEC1_PRTC1_IN

TSEC2_PRTC0_IN

TSEC2_PRTC1_IN

RIO_SYS_SIZE_IN

PCI_IO_IMPD_IN

RST_CNF_STROBE

SYS_PLL0_OUT

SYS_PLL0_OUT

SYS_PLL1_OUT

SYS_PLL2_OUT

SYS_PLL3_OUT

CFG_ID6

CORE_PLL0_OUT

CORE_PLL1_OUT

CORE_PLL2_OUT

SW_HRST

PORST_N

QE_PLL0_OUT

QE_PLL1_OUT

QE_PLL2_OUT

QE_PLL3_OUT

CFG_PCI_CLKSEL

QE_PLL4_OUT

HOST_AGT0_OUT

SW_SRST

HOST_AGT1_OUT

HOST_AGT2_OUT

CFG_ID7

CFG_DDR_DEBUG

SYS_PLL0_IN

BOOTSEQ1_OUT

RIO_SYS_SIZE_OUT

SYS_PLL0_IN

RSRV_OUT

CFG_CPU_BOOT

CFG_IO_PORT1

ROM_LOC1_IN

ROM_LOC2_IN

HOST_AGT0_IN

HOST_AGT1_IN

HOST_AGT2_IN

BOOTSEQ1_IN

SRDS_EN_IN

QE_PLL0_IN

QE_PLL1_IN

CFG_BOOTSEQ0

QE_PLL2_IN

QE_PLL3_IN

QE_PLL4_IN

QE_UCC_IN

TSEC1_WIDTH_IN

ROM_LOC1_IN

TSEC2_WIDTH_IN

TSEC1_PRTC0_IN

TSEC1_PRTC1_IN

TSEC2_PRTC0_IN

TSEC2_PRTC1_IN

RIO_SYS_SIZE_IN

PCI_IO_IMPD_IN

PCI_ARBITER_IN

SYS_PLL1_IN

RSRV_IN

SYS_PLL2_IN

SYS_PLL3_IN

CORE_PLL0_IN

CORE_PLL1_IN

CORE_PLL2_IN

CPU_BOOT_IN

ROM_LOC0_IN

CFG_PCI_SPEED

PCI_IO_IMPD_OUT

CFG_IO_PORT2

CFG_PCI_DEBUG

CFG_DRAM0

PCI_ARBITER_OUT

TSEC2_WIDTH_OUT

TSEC1_PRTC0_OUT

TSEC1_PRTC1_OUT

TSEC2_PRTC0_OUT

TSEC2_PRTC1_OUT

ROM_LOC2_IN

HOST_AGT2_IN

ROM_LOC0_IN

HOST_AGT0_IN

HOST_AGT1_IN

BOOTSEQ1_IN

SRDS_EN_IN

QE_PLL0_IN

QE_PLL1_IN

QE_PLL2_IN

QE_PLL3_IN

QE_PLL4_IN

QE_UCC_IN

TSEC1_WIDTH_IN

TSEC2_WIDTH_IN

TSEC1_PRTC1_IN

TSEC2_PRTC0_IN

TSEC2_PRTC1_IN

RIO_SYS_SIZE_IN

PCI_ARBITER_IN

SYS_PLL1_IN

RSRV_IN

SYS_PLL2_IN

SYS_PLL3_IN

CORE_PLL0_IN

CORE_PLL1_IN

CORE_PLL2_IN

CPU_BOOT_IN

TSEC1_PRTC0_IN

SYS_PLL0_IN

SRDS_EN_OUT

PCI_IO_IMPD_IN

CFG_DRAM1

ROM_LOC1_OUT

ROM_LOC2_OUT

HOST_AGT0_OUT

HOST_AGT1_OUT

HOST_AGT2_OUT

BOOTSEQ1_OUT

CFG_IO_PORT0

PCI_ARBITER_IN

SRDS_EN_OUT

QE_PLL0_OUT

QE_PLL1_OUT

QE_PLL2_OUT

QE_PLL3_OUT

QE_PLL4_OUT

SYS_PLL1_IN

RSRV_IN

QE_UCC_OUT

TSEC1_WIDTH_OUT

TSEC2_WIDTH_OUT

TSEC1_PRTC0_OUT

TSEC1_PRTC1_OUT

SYS_PLL2_IN

SYS_PLL3_IN

TSEC2_PRTC0_OUT

TSEC2_PRTC1_OUT

RIO_SYS_SIZE_OUT

PCI_IO_IMPD_OUT

CORE_PLL0_IN

PCI_ARBITER_OUT

SYS_PLL1_OUT

RSRV_OUT

SYS_PLL2_OUT

SYS_PLL3_OUT

CORE_PLL0_OUT

CORE_PLL1_OUT

CORE_PLL2_OUT

ROM_LOC0_OUT

CORE_PLL1_IN

CORE_PLL2_IN

CPU_BOOT_IN

ROM_LOC0_IN

LED1_N

LED3_N

ASLEEP_OUT

READY_TRIG-OUT

LED2_N

ISP_TDO

ISP_TDI

ISP_TCK

ISP_TMS

LWE_N0

XLD[0..7]

XLA31

XLA28

XLA29

XLA30

XLA27

XLA[27..31]

XLD4

XLD5

XLD6

XLD0

XLD7

XLD1

XLD2

XLD3 LED_CFG

SW_S0

SW_S1

SW_SS0

SW_SS1

ROM_LOC1_OUT

ROM_LOC2_OUT

ROM_LOC0_OUT

QE_UCC_OUT

TSEC1_WIDTH_OUT

CFG_MEM_DEBUG

COP_HRST

COP_SRST

COP_TMS

COP_TRST

COP_TDO

COP_TDI

COP_TCK

CFG_CPU_BOOT

DGND

RST_CNTR_CLK

G2_NARROW_N

MII1EN_N

MII2EN_N

G1_NARROW_N

G3GMII_N

G3_CNF4

GETHRST_N

G4GMII_N

G3_CNF3

GETH4EN_N

G4_CNF4

GETH3EN_N

G4_CNF3

RS232EN_N

3V3

FLASH_RDY

BUFFEN_N

WP_N

FLASH_RST_N

UART1_EN_N

G3_010

G4_010

G4TXD0

ASLEEP

G4TXD7

G1_WIDE_N

G2_WIDE_N

UPC2_POS_N

GETH1EN_N

GETH2EN_N

3V3_IO

ENET8_EN_N

ENET5_EN_N

TDMF_EN_N

DDR_SEL

TDMA_EN_N

TDMB_EN_N

TDMC_EN_N

SPI_EN_N

ENET4_EN_N

ENET3_EN_N

E1_TXER

PWR_RST_N

CKSTP_OUT_B

CKSTP_IN_B

XUPC1_TXD13

XUPC1_TXD12

XUPC1_TXPRTY

XUPC1_TXD15

XUPC1_TXD14

XPCI1_GNT1

XPCI1_GNT2

E1_TXD1

E1_TXD0

E1_TXD2

E2_TXD2

E2_TXD1

E2_TXD0

E2_TXD6

E2_TXD5

G3TXD7

G3TXD0

LA27

LA28

LA29

LA30

LA31

LWE_N1

LWE_N2

LWE_N3

LALE

LBCTL

LGPL2

LGPL0

LWE_N0

LGPL5

LGPL3

MSRCID1

G3TXER

XPCI1_GNT3

XPCI1_GNT4

XLA[27..31]

XLD[0..7]

LCS_N3

LCS_N1

LGPL2

BOOT_WP

BRD_WP

CLKIOEN_N

3V3_PCIEDGE_N

IRQ_OUT_N

HRESET_REQ_N

RTC_RESET_N

PCIE_CLKDIS_N

MEMRST_N

XPCI1_RST_N

XPCI1_M66EN

PWRGD_MB

XPPEN

TRIG_IN

TRIG_OUT

X2JTAG_TDO

X2JTAG_TDI

X2JTAG_TMS

X2JTAG_TCK

X2JTAG_TRST

XJTAG_TDO

XJTAG_TDI

XJTAG_TMS

XJTAG_TCK

XJTAG_TRST

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TDI

SRESET_N

HRESET_N

CPU_TRST_N

TBI1_EN

TBI2_EN

S0

S1

SS0

SS1

E1_TXD4

E1_TXD6

E1_TXD5

EC_MDC

XUPC1_TXD10

MSRCID0

CFG_RSRV

5V0

MD_CNTR

G0_CNF3

G0_CNF4

G1_CNF3

G1_CNF4

G0_010

G1_010

XRESET_N

PCIEDGE_RST_N

DGND

3V3_IO

DGND

DGND

3V3

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

DGND

3V3

DGND

3V3

DGND

3V3

DGND

DGND

DGND

3V3

DGND

3V3_IO

3V3

3V3

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

DGND

3V3

3V3

DGND

DGND

3V3

DGND

3V3

5V0

DGND

3V3

Size Document Number Rev

Date: Sheet

of

C

419Thursday, August 02, 2007

Pilot

Size Document Number Rev

Date: Sheet

of

C

419Thursday, August 02, 2007

Pilot

Size Document Number Rev

Date: Sheet

of

C

419Thursday, August 02, 2007

Pilot

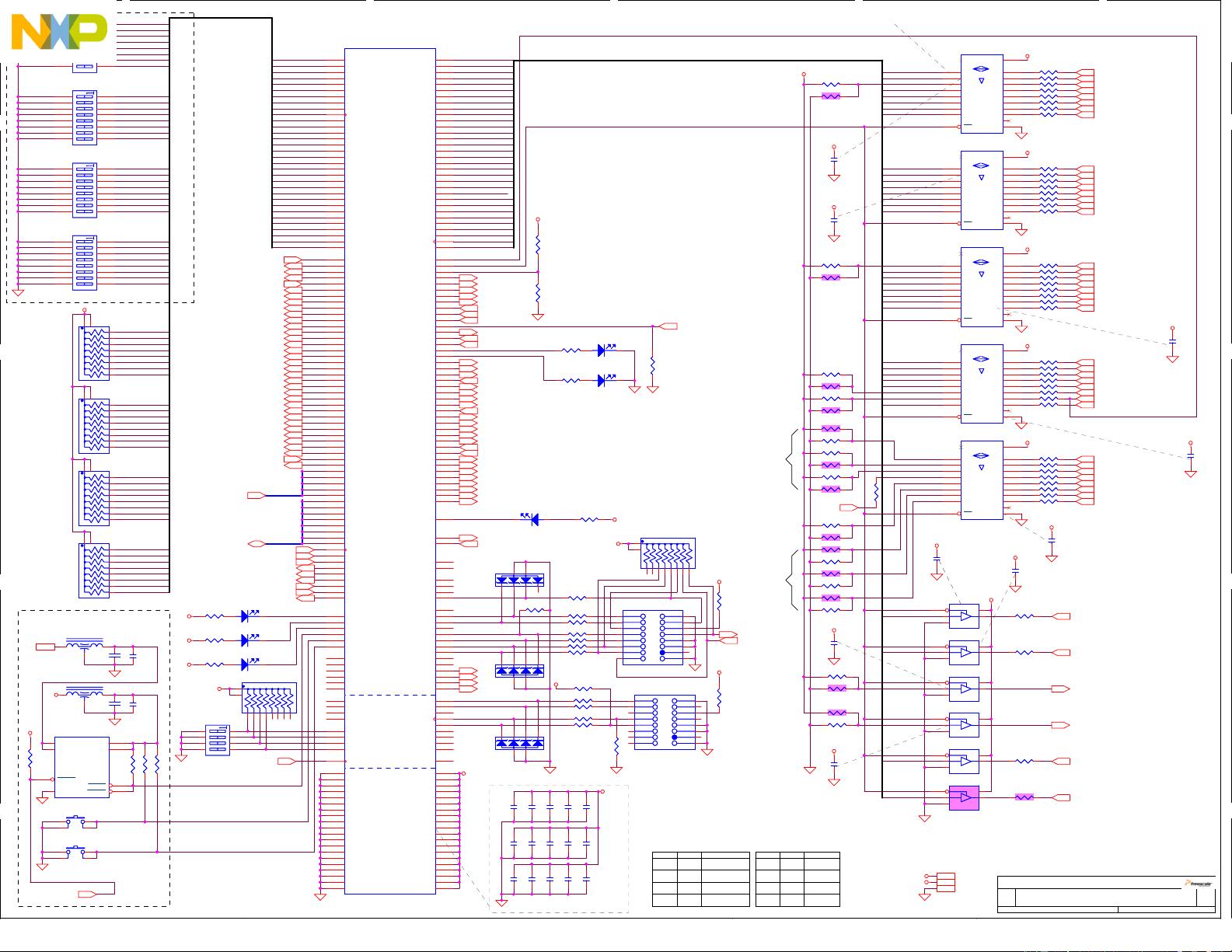

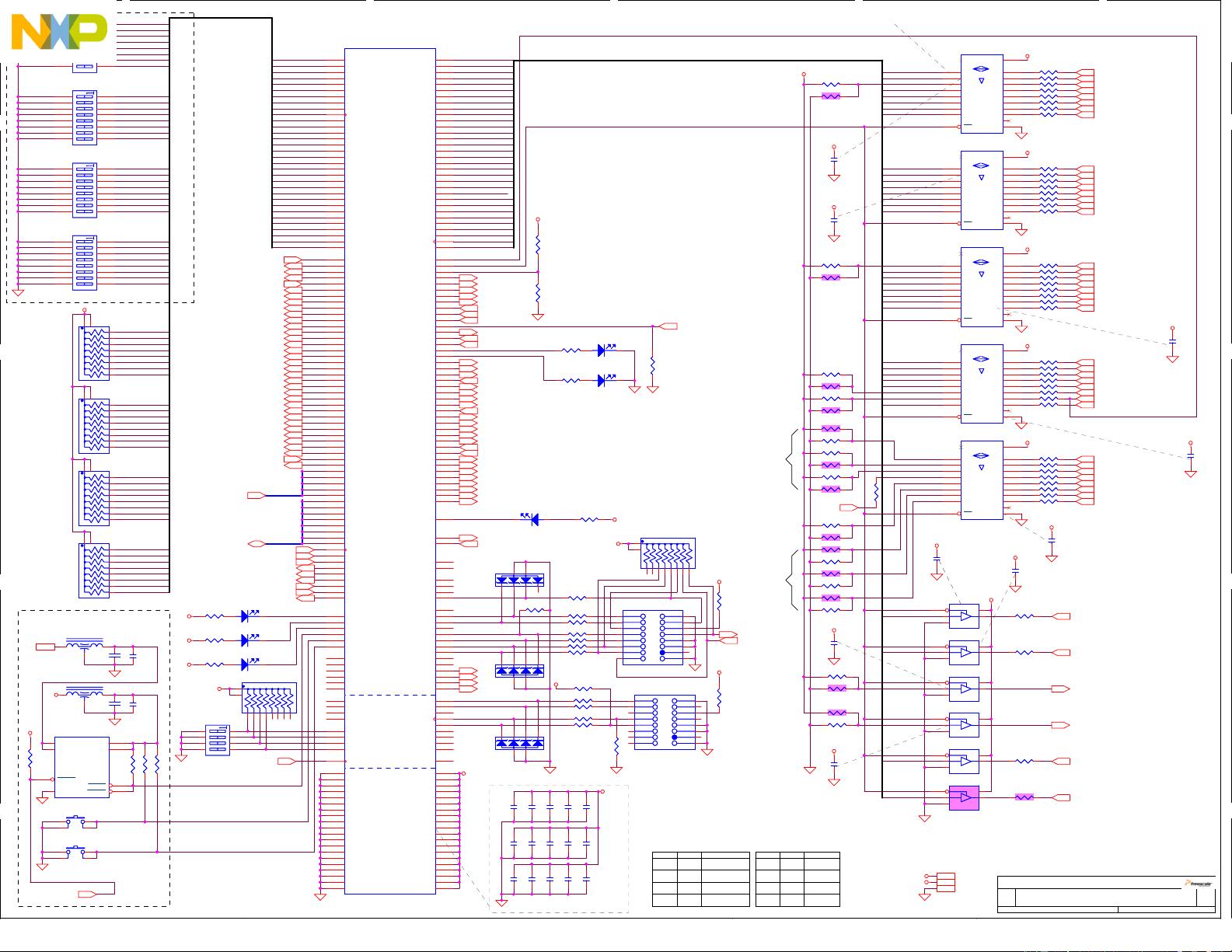

MPC8568E-MDS-PB (BOARD_CNTR)

084-00223-2

{

"Cfg_PCI Debug"

"Cfg_QE PLL0"

"Cfg_QE PLL2"

"Cfg_QE PLL1"

"Cfg_QE PLL4"

"Cfg_QE PLL3"

"Cfg_device_ID5"

"Cfg_DRAM TYPE0"

"Cfg_device_ID6"

"Cfg_device_ID7"

"Cfg_DRAM TYPE1"

"TSEC1 PRTC0"

"HOST/AGT0"

"HOST/AGT1"

"TSEC1 PRTC1"

"TSEC2 PRTC0"

"TSEC2 PRTC1"

"COP"

"HOST/AGT2"

"Cfg_PCI Clock Select"

"RIO SYS SIZE"

"PCI I/O IMPD"

"CORE PLL2"

"PCI ARBITER"

"QE PLL1"

"QE PLL0"

"QE PLL2"

"QE PLL3"

"SYS PLL0"

"SYS PLL1"

"SYS PLL2"

"SYS PLL3"

"CORE PLL0"

"CORE PLL1"

"QE PLL4"

"Cfg_PCI ARBITER"

"Cfg_PCI I/O IMPD"

{

Serial RapidIO x4 (1.25 Gbps);

PCI Express x4 (2.5 Gbps)

100-MHz reference clock

Serial RapidIO:

RX lane[0:3] -> SD_RX[4:7],

TX lane[0:3] -> SD_TX[4:7]

PCI Express:

RX lane[0:3] -> SD_RX[0:3],

TX lane[0:3] -> SD_TX[0:3]

PE8..10 = 011

PCI frequency at or above

33 MHz (1)

"Cfg_SYS PLL0"

"Cfg_SYS PLL2"

Configured as a RapidIO

host,the upper-order

device ID bits default

to zeros. (000)

"Cfg_SYS PLL1"

"Cfg_CORE PLL0"

"Cfg_SYS PLL3"

"Cfg_CORE PLL1"

"Cfg_CORE PLL2"

"SRST"

Trst ~350mS

RESET CNTR.

"HRST"

PCI operates

in normal mode. (1)

"Cfg_I/O PORT1"

"CNTR-ISP"

"Cfg_I/O PORT0"

"Cfg_I/O PORT2"

"Cfg_DDR Debug"

"Cfg_HOST/AGT0"

"Cfg_HOST/AGT1"

"Cfg_BOOTSEQ1"

"Cfg_HOST/AGT2"

{

Asynchronous mode.

PCI1_CLK is used as

the clock for the PCI

interface (0)

"Cfg_BOOTSEQ0"

"Cfg_CPU BOOT CONFIG"

{

"Cfg_TSEC1 PRTC1"

"Cfg_TSEC2 PRTC0"

"Cfg_TSEC1 PRTC0"

"Cfg_TSEC2 WIDTH"

"Cfg_TSEC2 PRTC1"

Debug information from the DDR SDRAM

controller is driven on the

MSRCID and MDVAL signals (1).

"Cfg_PCI Speed"

"Cfg_RIO SYS SIZE"

Boot sequencer is depended on

LGPL5 signal:

-No I2C ROM is accessed (11) or

-Extended I2C addressing mode is used (10)

{

Debug information is not driven

on ECC pins. ECC pins function

in their normal mode (1).

"QE UCC1,2"

"TSEC1 WIDTH"

"ROM LOC0"

"ROM LOC1"

"ROM LOC2"

"BOOTSEQ1"

"TSEC2 WIDTH"

DDR-II, FCRAM-I, FCRAM-II

1.8V, CKE low at reset (11)

DDR-I or FCRAM-I

2.5V, CKE low at reset (01)

"ASLEEP"

"TRIG_OUT"

"LED1"

"LED2"

"LED3"

CONFIG. SWITCHES

Programmable Pull-Up

{

"REG_CFG"

1(OFF)

1(OFF)

1(OFF)

0(ON) 0(ON)

SS1(4) SS0(3) SPREAD%

0(ON) 0(ON)

1(OFF)

CENTER+-0.25

DOWN -0.5

DOWN-0.75

NO SPREAD

0(ON)

SW6 DEFAULT POSITION:

100MHz, No Spread

0(ON)

1(OFF)

1(OFF)

S1(2) S0(1) CLK0:CLK1

1(OFF)0(ON)

25MHz

100MHz

125MHz

200MHz

0(ON)

1(OFF)

"S0"

"PCIe_CLK"

"S1"

"SS0"

"SS1"

"Cfg_ROM LOC0"

"Cfg_ROM LOC1"

"Cfg_ROM LOC2"

"Cfg_TSEC1 WIDTH"

"Cfg_QEGETH_V-SEL"

"Cfg_Memory Debug"

"SRDS_EN"

"CPU_BOOT"

"RSRV"

"0" - The QUICC Engine Block gigabit Ethernet interfaces operate at 2.5 V. (For RGMII and RTBI)

"1" - The QUICC Engine Block gigabit Ethernet interfaces operate at 3.3 V. (For MII, RMII, GMII, and TBI) (default)

"Cfg_SERDES_en"

{

{

SW3

GDH08S

SW3

GDH08S

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

R83390 R83390

C32

10uF

C32

10uF

R218390 R218390

C46

0.01uF

C46

0.01uF

R4010

No_Stuff

R4010

No_Stuff

R92390 R92390

R672 22R672 22

R195390 R195390

L9

NFM18PS105R0J3

L9

NFM18PS105R0J3

1 3

2

R87390 R87390

R678 22R678 22

R59390 R59390

R675 22R675 22

R94390 R94390

U22

SN74CB3Q3245RGYR

U22

SN74CB3Q3245RGYR

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

B8

11

GND

10

VCC

20

OE

19

NC

1

THERM_PAD

21

LD2

AP1608MGC

LD2

AP1608MGC

R5040

No_Stuff

R5040

No_Stuff

R164

390

R164

390

R216390 R216390

R673 22R673 22

LD11

AP1608SYCK

LD11

AP1608SYCK

R521

1.5K

R521

1.5K

R3931K R3931K

R674 22R674 22

R60390 R60390

R4620 R4620

R52390 R52390

RESET Cntr.

U66

DS1834AS+T&R

RESET Cntr.

U66

DS1834AS+T&R

5V

1

5VRST

2

5VTOL

3

GND

4

PBRST

5

3.3VTOL

6

3.3RST

7

3.3V

8

R91390 R91390

RN6

10K

RN6

10K

10

1

2

3

4

6

7

8

9

5

R33910K R33910K

R86390 R86390

R4021K R4021K

SW6

GDH04S

SW6

GDH04S

1

2

3

4

8

7

6

5

SW8

DTSMW-69R-VT/R

SW8

DTSMW-69R-VT/R

1

2

3

4

C509

0.01uF

C509

0.01uF

R4380

No_Stuff

R4380

No_Stuff

R3940

No_Stuff

R3940

No_Stuff

C90

1uF

C90

1uF

C86

0.01uF

C86

0.01uF

R78390 R78390

C99

0.01uF

C99

0.01uF

C69

0.01uF

C69

0.01uF

R5310 R5310

U24

SN74CB3Q3245RGYR

U24

SN74CB3Q3245RGYR

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

B8

11

GND

10

VCC

20

OE

19

NC

1

THERM_PAD

21

U93

SMS3.3.TCT

U93

SMS3.3.TCT

1

3

4

6

5

2

R1261K R1261K

U31

SN74CB3Q3245RGYR

U31

SN74CB3Q3245RGYR

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

B8

11

GND

10

VCC

20

OE

19

NC

1

THERM_PAD

21

R211390 R211390

R143

1K

R143

1K

R4200

No_Stuff

R4200

No_Stuff

C96

0.1uF

C96

0.1uF

R196390 R196390

R290

No_Stuff

R290

No_Stuff

R5330 R5330

R676 22R676 22

C361

0.01uF

C361

0.01uF

R1501K R1501K

L10

NFM18PS105R0J3

L10

NFM18PS105R0J3

1 3

2

R62390 R62390

R680 22R680 22

SW4

GDH08S

SW4

GDH08S

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

C254

0.1uF

C254

0.1uF

R4191K R4191K

C98

0.1uF

C98

0.1uF

R80390 R80390

R82390 R82390

R34110K R34110K

RN5

10K

RN5

10K

10

1

2

3

4

6

7

8

9

5

R95390 R95390

C126

0.01uF

C126

0.01uF

C24

0.01uF

C24

0.01uF

C140

0.01uF

C140

0.01uF

R681 22R681 22

C70

1uF

C70

1uF

C88

0.01uF

C88

0.01uF

R251K

No_Stuff

R251K

No_Stuff

U95

SMS3.3.TCT

U95

SMS3.3.TCT

1

3

4

6

5

2

C89

0.1uF

C89

0.1uF

R1490 R1490

R5030

No_Stuff

R5030

No_Stuff

LD12

AP1608SECK

LD12

AP1608SECK

R90390 R90390

SW2

GDH08S

SW2

GDH08S

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

R43410K R43410K

C71

0.1uF

C71

0.1uF

C242

0.01uF

C242

0.01uF

R93390 R93390

R698 10KR698 10K

VCC

GND

OE*

U6

NL17SZ125XV5T2G

VCC

GND

OE*

U6

NL17SZ125XV5T2G

4

1

2

5

3

R301K R301K

R84390 R84390

R1810

No_Stuff

R1810

No_Stuff

R163

390

R163

390

R81390 R81390

R217390 R217390

KEY

TRST

GND

NC

NC

CKSTPI

SNS

NCTDO

TDI

QREQ

TCK

TMS

SRST

HRST

CKSTPO

P4

HTSS-108-01-S-DV

KEY

TRST

GND

NC

NC

CKSTPI

SNS

NCTDO

TDI

QREQ

TCK

TMS

SRST

HRST

CKSTPO

P4

HTSS-108-01-S-DV

1

3

5

7

9

11

13

15

2

4

6

8

10

12

14

16

R682 22R682 22

R268

330

R268

330

R1511K

No_Stuff

R1511K

No_Stuff

LD1

AP1608SECK

LD1

AP1608SECK

R193390 R193390

R4630

No_Stuff

R4630

No_Stuff

R1291K

No_Stuff

R1291K

No_Stuff

R156390 R156390

R553390 R553390

R219390 R219390

R197390 R197390

RN7 10KRN7 10K

10

1

2

3

4

6

7

8

9

5

R154390 R154390

R706

1K

R706

1K

RN2 10KRN2 10K

10

1

2

3

4

6

7

8

9

5

R240 R240

R694

100K

R694

100K

R89390 R89390

VCC

GND

OE*

U40

NL17SZ125XV5T2G

No_Stuff

VCC

GND

OE*

U40

NL17SZ125XV5T2G

No_Stuff

4

1

2

5

3

R53390 R53390

R58390 R58390

KEY

TRST

GND

NC

NC

CKSTPI

SNS

NCTDO

TDI

QREQ

TCK

TMS

SRST

HRST

CKSTPO

P5

HTST-108-01-SM-DV

KEY

TRST

GND

NC

NC

CKSTPI

SNS

NCTDO

TDI

QREQ

TCK

TMS

SRST

HRST

CKSTPO

P5

HTST-108-01-SM-DV

1

3

5

7

9

11

13

15

2

4

6

8

10

12

14

16

LD10

AP1608MGC

LD10

AP1608MGC

VCC

GND

OE*

U43

NL17SZ125XV5T2G

VCC

GND

OE*

U43

NL17SZ125XV5T2G

4

1

2

5

3

R679 22R679 22

C84

1uF

C84

1uF

R85390 R85390

U46

SN74CB3Q3245RGYR

U46

SN74CB3Q3245RGYR

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

B8

11

GND

10

VCC

20

OE

19

NC

1

THERM_PAD

21

C87

0.1uF

C87

0.1uF

R162

390

R162

390

R1531K

No_Stuff

R1531K

No_Stuff

R1790 R1790

LD9

AP1608SECK

LD9

AP1608SECK

R130390 R130390

C367

0.01uF

C367

0.01uF

R4371K R4371K

C129

0.01uF

C129

0.01uF

R54390 R54390

U78

EPM1270F256C5N

U78

EPM1270F256C5N

IO_B0_C2

C2

IO_B0_C3

C3

IO_B0_D1

D1

IO_B0_D2

D2

IO_B0_D3

D3

IO_B0_E1

E1

IO_B0_E2

E2

IO_B0_E3

E3

IO_B0_E4

E4

IO_B0_E5

E5

IO_B0_F1

F1

IO_B0_F2

F2

IO_B0_F3

F3

IO_B0_F4

F4

IO_B0_F5

F5

IO_B0_F6

F6

IO_B0_G1

G1

IO_B0_G2

G2

IO_B0_G3

G3

IO_B0_G4

G4

IO_B0_G5

G5

IO_B0_G6

G6

IO_B0_H1

H1

IO_B0_H2

H2

IO_B0_H3

H3

IO_B0_H4

H4

IO_B0_J1

J1

IO_B0_J2

J2

IO_B0_J3

J3

IO_B0_J4

J4

IO_B0_K1

K1

IO_B0_K2

K2

IO_B0_K3

K3

IO_B0_K4

K4

IO_B0_K5

K5

IO_B0_K6

K6

IO_B0_L1

L1

IO_B0_L2

L2

IO_B0_L3

L3

IO_B0_L4

L4

IO_B0_L5

L5

IO_B0_M1

M1

IO_B0_M2

M2

IO_B0_M3

M3

IO_B0_M4

M4

IO_B0_N1

N1

IO_B0_N2

N2

IO_B0_N3

N3

IO_B0_P2

P2

IO_B2_C14

C14

IO_B2_C15

C15

IO_B2_D13

D13

IO_B2_D14

D14

IO_B2_D15

D15

IO_B2_D16

D16

IO_B2_E12

E12

IO_B2_E13

E13

IO_B2_E14

E14

IO_B2_E15

E15

IO_B2_E16

E16

IO_B2_F11

F11

IO_B2_F12

F12

IO_B2_F13

F13

IO_B2_F14

F14

IO_B2_F15

F15

IO_B2_F16

F16

IO_B2_G11

G11

IO_B2_G12

G12

IO_B2_G13

G13

IO_B2_G14

G14

IO_B2_G15

G15

IO_B2_G16

G16

IO_B2_H13

H13

IO_B2_H14

H14

IO_B2_H15

H15

IO_B2_H16

H16

IO_B2_J13

J13

IO_B2_J14

J14

IO_B2_J15

J15

IO_B2_J16

J16

IO_B2_K11

K11

IO_B2_K12

K12

IO_B2_K13

K13

IO_B2_K14

K14

IO_B2_K15

K15

IO_B2_K16

K16

IO_B2_L11

L11

IO_B2_L12

L12

IO_B2_L13

L13

IO_B2_L14

L14

IO_B2_L15

L15

IO_B2_L16

L16

IO_B2_M13

M13

IO_B2_M14

M14

IO_B2_M15

M15

IO_B2_M16

M16

IO_B2_N13

N13

IO_B2_N14

N14

IO_B2_N15

N15

IO_B2_N16

N16

IO_B2_P14

P14

IO_B2_P15

P15

IO_B1_A2

A2

IO_B1_A4

A4

IO_B1_A5

A5

IO_B1_A6

A6

IO_B1_A7

A7

IO_B1_A8

A8

IO_B1_A9

A9

IO_B1_A10

A10

IO_B1_A11

A11

IO_B1_A12

A12

IO_B1_A13

A13

IO_B1_A15

A15

IO_B1_B1

B1

IO_B1_B3

B3

IO_B1_B4

B4

IO_B1_B5

B5

IO_B1_B6

B6

IO_B1_B7

B7

IO_B1_B8

B8

IO_B1_B9

B9

IO_B1_B10

B10

IO_B1_B11

B11

IO_B1_B12

B12

IO_B1_B13

B13

IO_B1_B14

B14

IO_B1_B16

B16

IO_B1_C4

C4

IO_B1_C5

C5

IO_B1_C6

C6

IO_B1_C7

C7

IO_B1_C8

C8

IO_B1_C9

C9

IO_B1_C10

C10

IO_B1_C11

C11

IO_B1_C12

C12

IO_B1_C13

C13

IO_B1_D4

D4

IO_B1_D5

D5

IO_B1_D6

D6

IO_B1_D7

D7

IO_B1_D8

D8

IO_B1_D9

D9

IO_B1_D10

D10

IO_B1_D11

D11

IO_B1_D12

D12

IO_B1_E6

E6

IO_B1_E7

E7

IO_B1_E8

E8

IO_B1_E9

E9

IO_B1_E10

E10

IO_B1_E11

E11

IO_B1_F7

F7

IO_B1_F10

F10

IO_B3_L7

L7

IO_B3_L10

L10

IO_B3_M6

M6

IO_B3_M7

M7

IO_B3_M10

M10

IO_B3_M11

M11

IO_B3_M12

M12

IO_B3_N5

N5

IO_B3_N6

N6

IO_B3_N7

N7

IO_B3_N8

N8

IO_B3_N9

N9

IO_B3_N10

N10

IO_B3_N11

N11

IO_B3_N12

N12

IO_B3_P4

P4

IO_B3_P5

P5

IO_B3_P6

P6

IO_B3_P7

P7

IO_B3_P8

P8

IO_B3_P9

P9

IO_B3_P10

P10

IO_B3_P11

P11

IO_B3_P12

P12

IO_B3_P13

P13

IO_B3_R1

R1

IO_B3_R3

R3

IO_B3_R4

R4

IO_B3_R5

R5

IO_B3_R6

R6

IO_B3_R7

R7

IO_B3_R8

R8

IO_B3_R9

R9

IO_B3_R10

R10

IO_B3_R11

R11

IO_B3_R12

R12

IO_B3_R13

R13

IO_B3_R14

R14

IO_B3_R16

R16

IO_B3_T2

T2

IO_B3_T4

T4

IO_B3_T5

T5

IO_B3_T6

T6

IO_B3_T7

T7

IO_B3_T8

T8

IO_B3_T9

T9

IO_B3_T10

T10

IO_B3_T11

T11

IO_B3_T12

T12

IO_B3_T13

T13

IO_B3_T15

T15

GCLK0p

H5

GCLK1p

J5

GCLK2p

J12

GCLK3p

H12

GNDIO-1

A1

GNDIO-2

A16

GNDIO-3

B2

GNDIO-4

B15

GNDIO-5

G7

GNDIO-6

G8

GNDIO-7

G9

GNDIO-8

G10

GNDIO-9

K7

GNDIO-10

K8

GNDIO-11

K9

GNDIO-12

K10

GNDIO-13

R2

GNDIO-14

R15

GNDIO-15

T1

GNDIO-16

T16

GNDINT-1

H7

GNDINT-2

H9

GNDINT-3

J8

GNDINT-4

J10

TMS

N4

TDO

M5

TDI

L6

TCK

P3

DEV_OE

M8

DEV_CLRn

M9

VCCIO1-1

C1

VCCIO1-2

H6

VCCIO1-3

J6

VCCIO1-4

P1

VCCIO2-1

A3

VCCIO2-2

A14

VCCIO2-3

F8

VCCIO2-4

F9

VCCIO3-1

C16

VCCIO3-2

H11

VCCIO3-3

J11

VCCIO3-4

P16

VCCIO4-1

L8

VCCIO4-2

L9

VCCIO4-3

T3

VCCIO4-4

T14

VCCINT-1

H8

VCCINT-2

H10

VCCINT-3

J7

VCCINT-4

J9

R677 22R677 22

R33810K R33810K

C85

1uF

C85

1uF

R132390 R132390

R155390 R155390

U23

SN74CB3Q3245RGYR

U23

SN74CB3Q3245RGYR

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

12

B8

11

GND

10

VCC

20

OE

19

NC

1

THERM_PAD

21

C255

0.1uF

C255

0.1uF

RN4

10K

RN4

10K

10

1

2

3

4

6

7

8

9

5

R61390 R61390

R1281K R1281K

R450 R450

R131390 R131390

SW7

DTSMW-69N-VT/R

SW7

DTSMW-69N-VT/R

1

2

3

4

C72

1uF

C72

1uF

R1521K

No_Stuff

R1521K

No_Stuff

R699

1K

R699

1K

R267

390

R267

390

R194390 R194390

U94

SMS3.3.TCT

U94

SMS3.3.TCT

1

3

4

6

5

2

VCC

GND

OE*

U61

NL17SZ125XV5T2G

VCC

GND

OE*

U61

NL17SZ125XV5T2G

4

1

2

5

3

RN3

10K

RN3

10K

10

1

2

3

4

6

7

8

9

5

C97

0.01uF

C97

0.01uF

VCC

GND

OE*

U39

NL17SZ125XV5T2G

VCC

GND

OE*

U39

NL17SZ125XV5T2G

4

1

2

5

3

R88390 R88390

C31

10uF

C31

10uF

R182 330R182 330

R5320 R5320

R110

10K

R110

10K

VCC

GND

OE*

U45

NL17SZ125XV5T2G

VCC

GND

OE*

U45

NL17SZ125XV5T2G

4

1

2

5

3

SW1

GDH08S

SW1

GDH08S

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9