时间交错ADC技术解析:提升采样速率

需积分: 17 141 浏览量

更新于2024-09-07

收藏 724KB PDF 举报

"交错ADC揭秘.pdf"

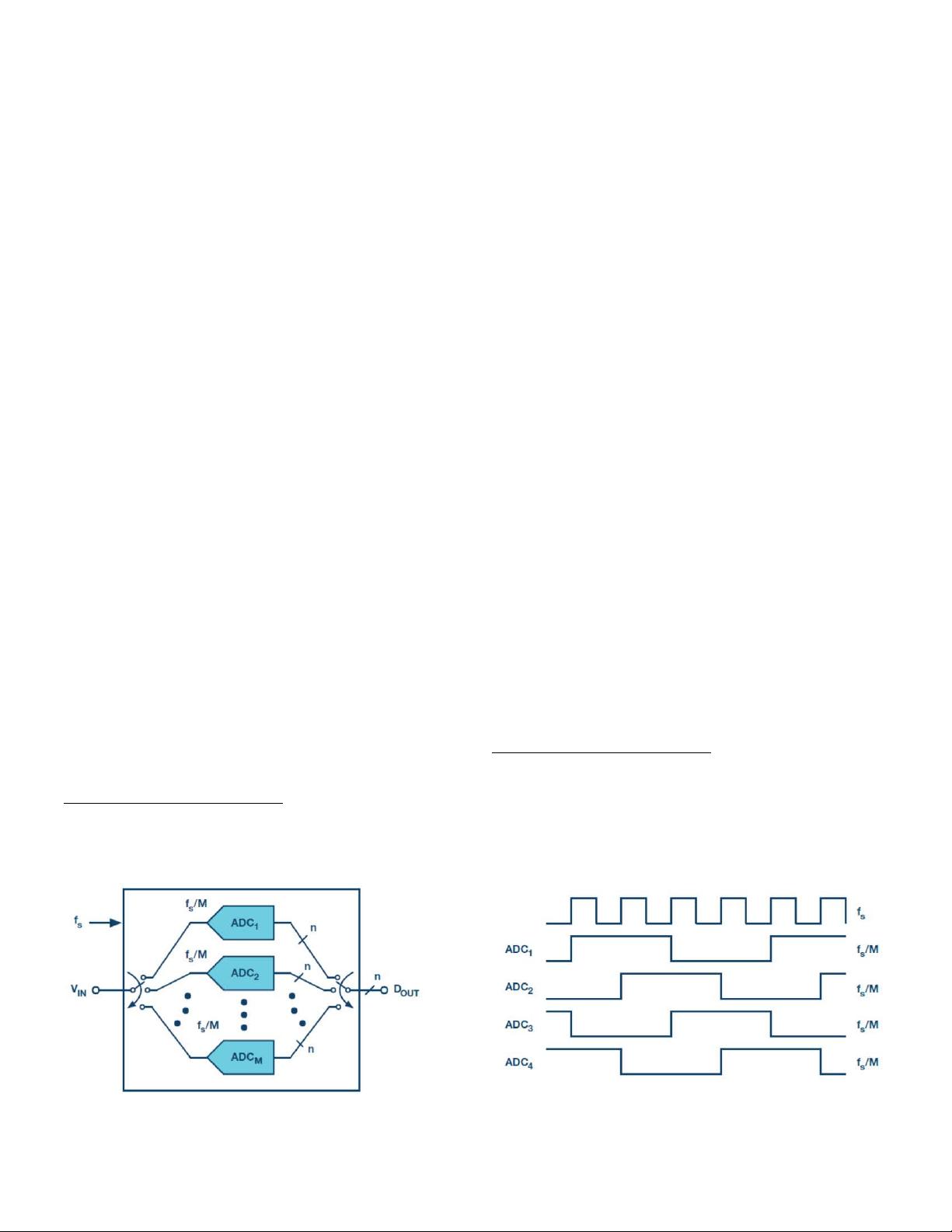

交错ADC(Interleaved ADC)是一种高效的方法,用于提升模数转换器(ADC)的采样速率,而无需使用单一高速ADC。该技术利用多个相同速度的ADC并行工作,通过时间多路复用的方式实现更高的总体采样率。在描述中提到,时间交错技术将M个ADC并联,每个ADC以较低的速率fs/M进行采样,但整体采样速率可以达到fs,这是通过在不同时间点对输入信号进行采样并交错输出数据来实现的。

例如,如果使用四个10位、100 MSPS(百万样本每秒)的ADC,通过交错,理论上可以实现一个等效的10位、400 MSPS ADC的性能。ADC的采样顺序是按照预设的时间间隔Ts进行,每个ADC在Ts的整数倍时采样输入信号VIN(t),形成一个数字输出序列DOUT。

在系统中,ADC的输出数据经过解复用器重新排序,形成连续的高数据速率输出序列。这个过程的关键在于,尽管每个通道的ADC采样速度较慢,但它们的输出被有效地合并在一起,使得整体采样速率提高,从而实现更高的信号重建质量。

然而,交错ADC技术也面临挑战。其中一个重要问题是通道间同步和数据流的正确重组。在数字域中重新组合来自多个通道的数据时,需要精确的时间同步,以确保能准确地重建原始输入信号VIN。此外,交错ADC可能会引入额外的噪声和失真,比如通道间增益和相位不匹配,这可能会影响系统的信噪比(SNR)和无杂散动态范围(SFDR)。

解决这些问题通常需要精心设计的同步电路和数字后处理算法,比如误差校正和通道补偿。这些技术有助于减少通道间的不一致性和提高系统的整体性能。

交错ADC技术在许多领域都有应用,包括通信、成像、测试测量和信号处理等,它能够提供高性能采样解决方案,同时避免了高速ADC设计的复杂性和成本。尽管存在挑战,但通过巧妙的系统设计和算法优化,交错ADC已成为实现高速数据采集系统的一种实用方法。

2019-09-13 上传

2019-09-15 上传

2021-08-10 上传

2019-08-27 上传

2021-11-24 上传

2021-05-20 上传

2021-09-21 上传

2022-11-27 上传

2022-11-27 上传

weixin_39840914

- 粉丝: 436

- 资源: 1万+

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍