数字逻辑实验:二进制加法器设计与仿真

需积分: 25 6 浏览量

更新于2024-07-16

收藏 466KB DOCX 举报

"该文档是华中科技大学计算机科学与技术学院的一份数字逻辑实验报告,主要涉及二进制加法器的设计与仿真。学生需要利用Logisim软件完成5种不同类型的二进制加法器设计,包括半加器、全加器、串行进位的四位并行加法器和先行进位的四位并行加法器,并对设计的电路进行虚拟实验仿真。实验旨在训练学生的传统逻辑电路设计、仿真和调试能力。"

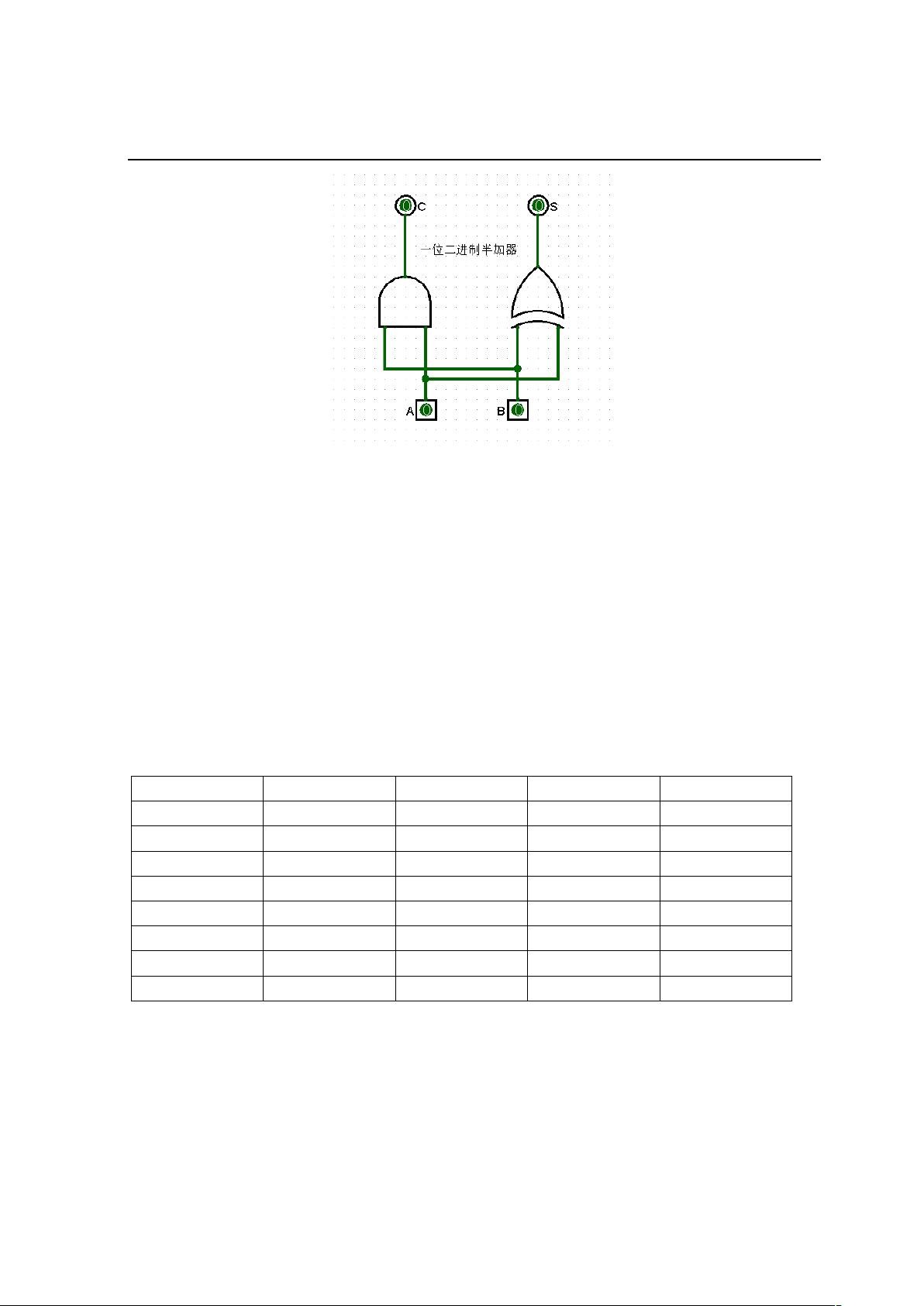

在数字逻辑实验中,二进制加法器是基础且重要的概念。半加器是其中最简单的形式,它只有两个输入A和B,分别代表被加数和加数,以及两个输出S和C,其中S表示本位和,C表示进位。全加器则增加了一个输入Ci,代表来自低位的进位,输出除了S之外还多了一个Co,同样表示向高位的进位。这两种加法器在实际计算中用于处理二进制数的加法运算。

实验内容详细列出了五种不同类型的加法器设计:

1. 一位二进制半加器:设计电路以实现A和B的加法,输出S和C。

2. 一位二进制全加器:在半加器的基础上增加了Ci输入,考虑了进位情况。

3. 串行进位的四位二进制并行加法器:通过四个全加器串联,使得高位的进位依次传递,实现了四位二进制数的并行加法。

4. 先行进位的四位二进制并行加法器:利用超前进位技术,可以更快地计算出高位的进位,提高了加法运算的速度。

5. 封装先行进位的四位二进制并行加法器:将设计好的电路封装成一个自定义组件,便于后续实验使用,并验证其正确性。

实验过程中,Logisim软件是一个关键工具,它提供了一个可视化平台,让学生能够设计、仿真和调试逻辑电路。通过这些实验,学生不仅能掌握基本的逻辑门(如AND、OR、NOT、XOR等)的运用,还能理解二进制加法背后的逻辑原理,并学会如何通过逻辑门组合实现复杂的计算功能。

此外,实验报告的编写也是对学生表达能力和逻辑思维能力的锻炼,要求他们清晰地记录实验步骤、结果分析和可能的问题解决方案。这样的实践教学方式有助于提升学生的理论知识与实际操作技能的结合,为将来在计算机硬件设计、嵌入式系统开发等领域的工作打下坚实的基础。

120 浏览量

2022-03-13 上传

236 浏览量

6430 浏览量

207 浏览量

2022-07-01 上传

weixin_44808897

- 粉丝: 0

最新资源

- DENSITY超快速压缩库:高速压缩与领先算法

- Matlab开发工具:EditorTemplatesPackage代码模板库

- Gmail机密模式替代Secure Gmail扩展程序指南

- 电子秤通讯协议与数据格式解析

- 蓝色公安局信息网模板html项目源码下载

- Python编程自学指南:笨办法学Python(第四版)

- JBText:一个跨平台的开源纯文本编辑器项目

- 从失败中学习:培养软件开发者成长心态

- MATLAB脚本功能:bringEditorsToFocus.m解析

- 太阳能MPPT控制器:成本低廉实现最大效能

- Rust语言中快速开发优质命令行界面的quicli工具

- C++实现数据结构顺序表与单链表

- Angular项目开发与部署流程解析

- Python库twint_fork-2.1.24详细使用指南与安装教程

- TechCodeDev技术开发新进展

- Matlab GUI开发:入门标签的创建与欢迎界面