运算器实验:探索ALU与超前进位加法器原理

需积分: 29 23 浏览量

更新于2024-09-08

2

收藏 24.32MB DOC 举报

“运算器实验报告,软件学院软件工程专业,通过TD-CMA教学实验系统理解运算器结构和工作原理,重点探讨ALU、超前进位加法器,涉及CPLD、EDA软件使用。”

在“运算器实验”中,主要目标是理解和掌握运算器的构成和工作方式,以及超前进位加法器的原理和设计。实验设备主要包括TD-CMA教学实验系统和PC微机,利用这些设备,学生可以实际操作并观察运算器内部的运算过程。

运算器是计算机核心组件之一,它包含算术逻辑单元(ALU)和暂存器等部分。ALU是执行基本算术和逻辑运算的地方,如加法、减法、逻辑与、逻辑或等。在ALU中,设置暂存器A和B是为了能够存储待处理的数据,以便进行运算。当改变S3~S0和CN的状态时,可以执行不同的运算操作,比如加法、减法或逻辑操作,进而观察操作结果的变化。

T4脉冲在运算器中起到关键作用,它通常作为时钟信号的一部分,用于触发ALU的特定操作。在实验中,T4脉冲的出现会影响ALU的运算周期,确保在正确的时间进行数据的读取、处理和写回。

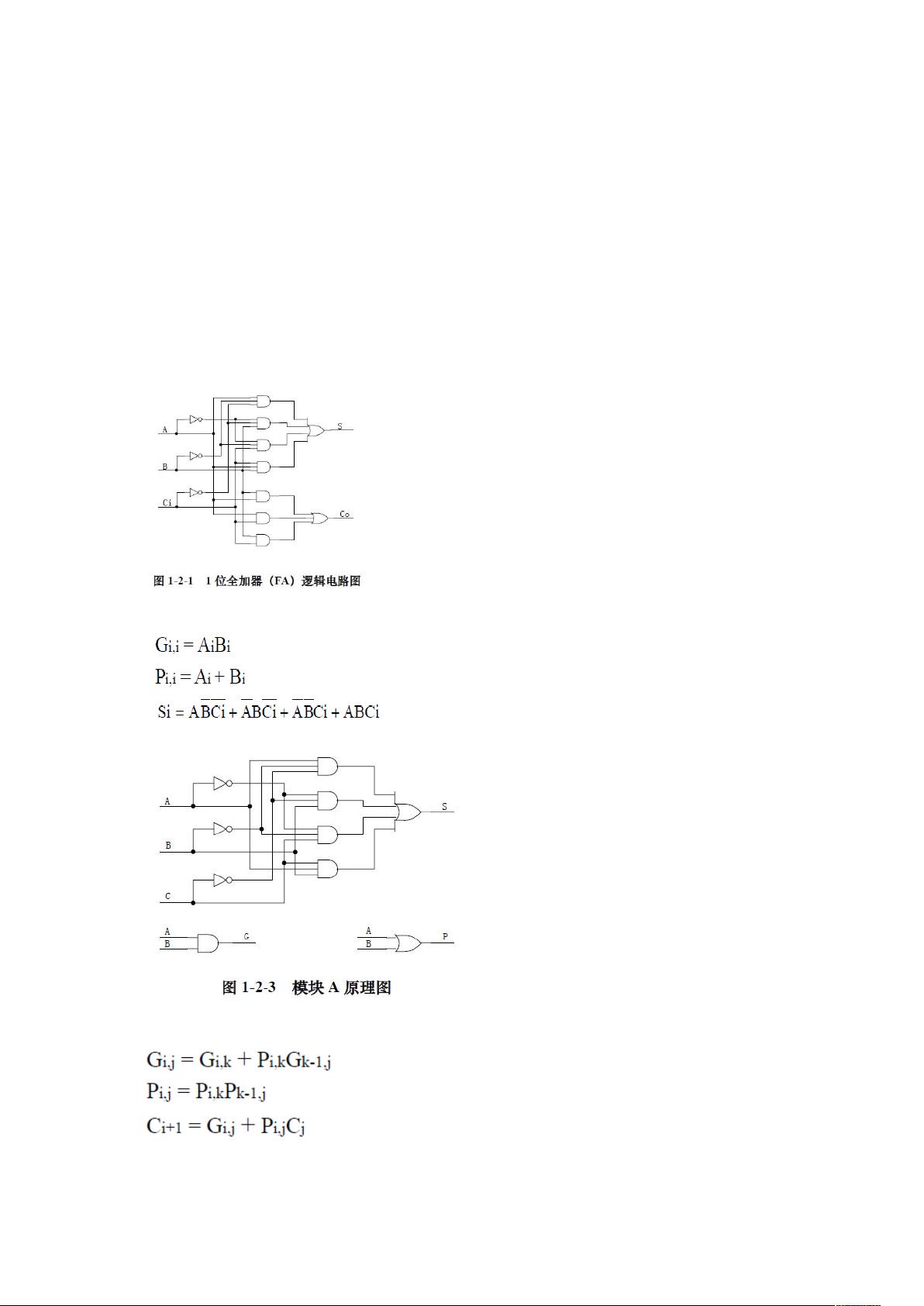

超前进位加法器是提高运算速度的重要技术,它能在低位进行加法运算的同时计算高位的进位,从而减少了整个加法过程所需的时间。全加器是超前进位加法器的基础,它不仅考虑当前位的加法,还考虑低位的进位。全加器的逻辑表达式包括和(S)和进位(Co)的计算,涉及三个输入(A、B和低位进位Ci)。

实验步骤中,学生需要正确连接实验电路,设置控制信号,然后通过输入开关向暂存器A置数。通过改变数据开关的状态,可以观察不同数值在ALU中的运算结果,同时注意进位标志FC和零标志FZ的变化,以了解运算状态。

通过这个实验,学生不仅能学习到运算器的基本构造和工作原理,还能熟悉CPLD(复杂可编程逻辑器件)的应用以及EDA(电子设计自动化)软件的使用,这些都是现代数字系统设计的关键技术。实验结束后,学生应能独立分析和设计简单的运算器功能,为后续的计算机体系结构学习打下坚实基础。

11319 浏览量

131 浏览量

2023-12-18 上传

138 浏览量

304 浏览量

2023-11-16 上传

140 浏览量

qq_35434235

- 粉丝: 10

- 资源: 16

最新资源

- NLP_practices:涉及日常实验室和作业

- HierarchicalComputerFileSystem:C ++程序,可模拟简单的分层计算机文件系统

- app开发之React Native教程合集.zip_zipapp lite

- Python二级编程题.zip

- laravel-web-to-pdf

- 大学物理实验目录及正文.rar

- v2ex-ios::globe_showing_Europe-Africa: v2ex - 创意工作者社区

- E-Comm-laravel

- 女性个人简历信息响应式网页模板

- 网上购物系统:AT Project Sem-5

- Python_ProgramingExperience_to_Pythonic。记录编程过程中遇到的一些问题和解决资料.zip

- tcbot:Tcbot 是 IRC 到 WoW Channel 桥接机器人

- lein-git-inject:Leiningen中间件,它在构建时从环境git上下文中计算“版本”(请考虑最新标签)

- grbl1.1f20170801-stm32f103c8t6

- 微信小程序Demo:小费计算器

- 《Python编程:从入门到实践》、《笨办法学Python》练习题.zip