Cortex-M3内核详解:配置与编程指南

需积分: 17 92 浏览量

更新于2024-07-25

收藏 1.78MB PDF 举报

Cortex-M3内核手册是一份详细的指南,专注于Cortex-M3处理器的技术特性、编程模型和系统控制。该手册旨在帮助开发者理解和利用Cortex-M3处理器的潜力,以实现高效能和精确的嵌入式系统设计。

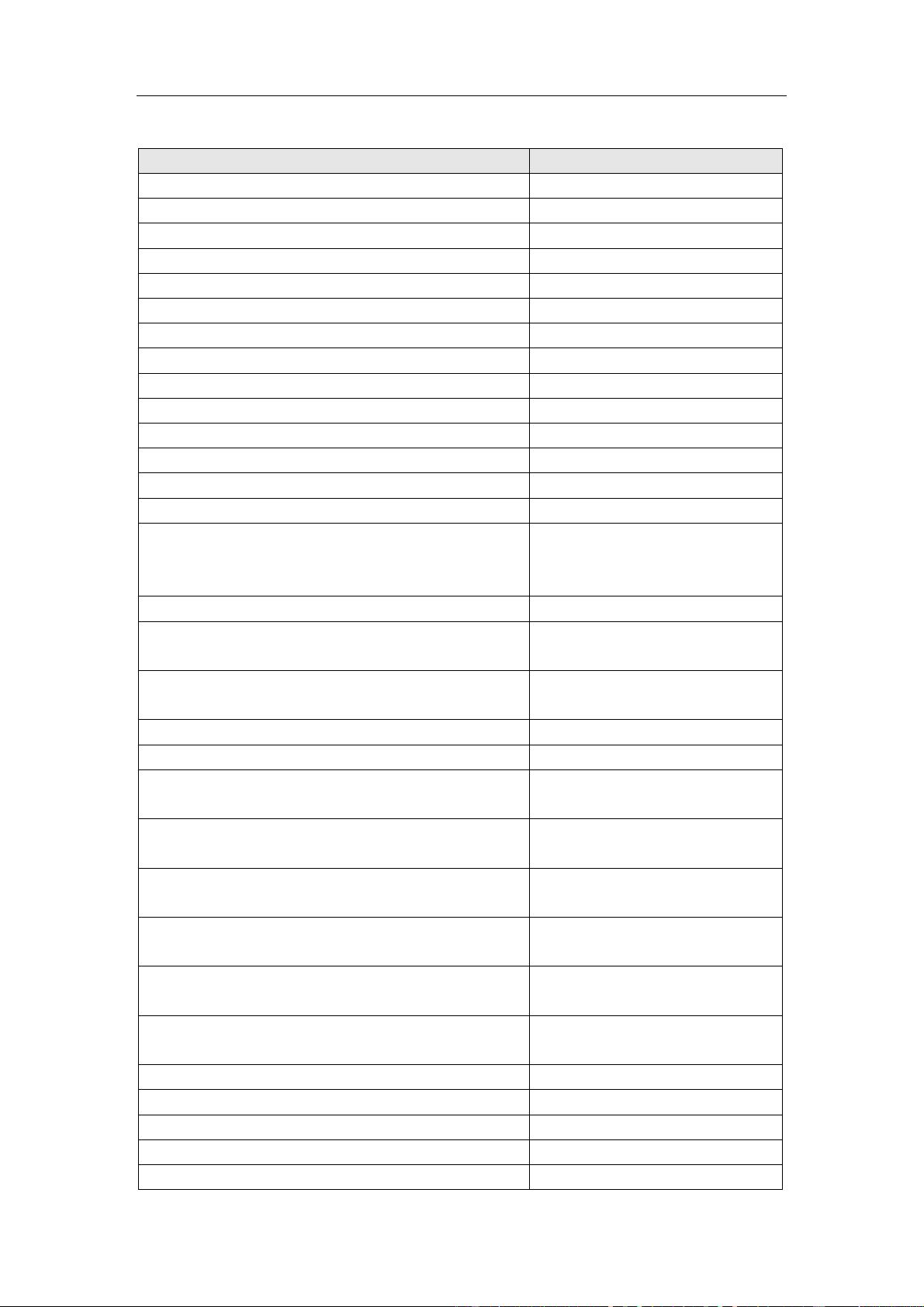

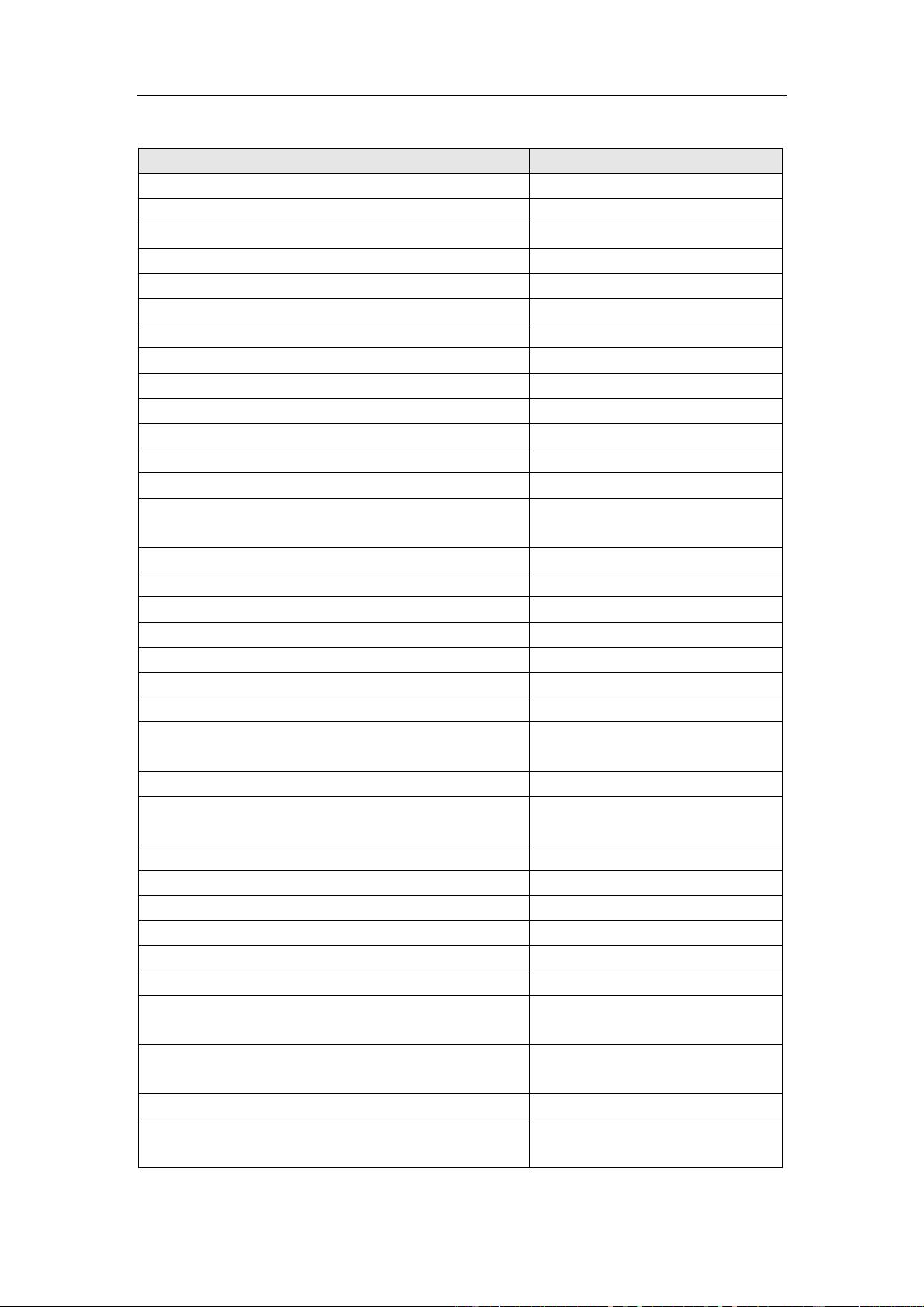

在第一章“概述”中,介绍了处理器的基本概念,包括Cortex-M3的层次结构和实现选项。处理器内核是核心组件,它提供了基础的运算处理能力;NVIC(Nested Vectored Interrupt Controller)负责管理中断处理;总线矩阵确保了不同模块间的通信;FPB(Flash Program Bus)、DWT(Data Watchpoint and Trace Unit)提供调试功能;ITM(In-Trace Macrocell)和MPU(Memory Protection Unit)用于内存管理和权限控制;ETM(Embedded Trace Macrocell)则支持代码分析;TPIU(Trace Port Interface Unit)协助跟踪;SW/JTAG-DP(Software/JTAG Debug Port)则是调试接口。

第二章“编程模型”深入解析了处理器的工作模式和状态,区分了特权访问和用户访问,强调了主堆栈和进程堆栈的概念。此外,还详细介绍了寄存器体系,如通用寄存器和特殊用途的程序状态寄存器xPSR,以及数据类型、存储器格式和指令集。

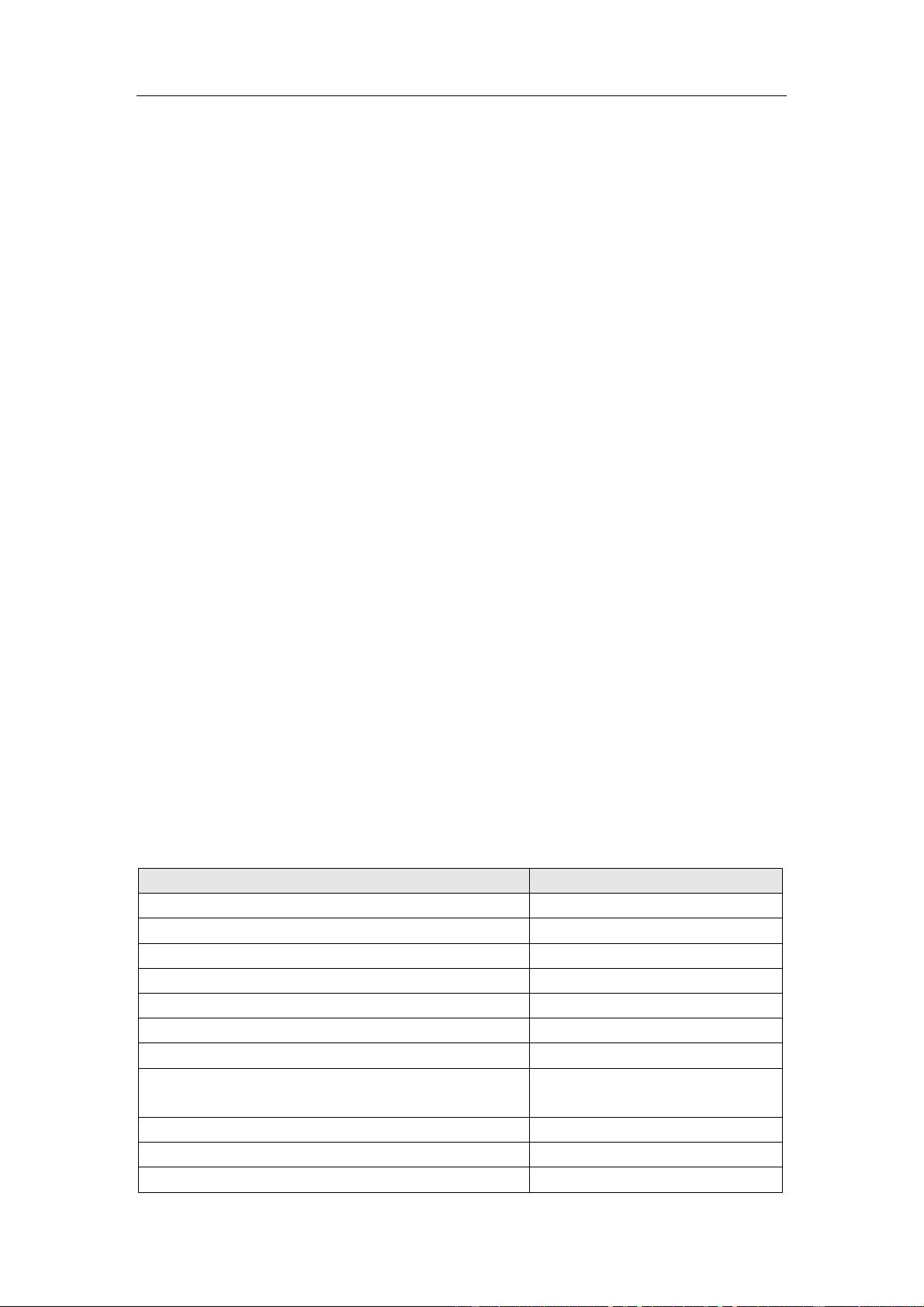

第三章“系统控制”涵盖了处理器寄存器的全面介绍,包括NVIC寄存器、调试接口寄存器、存储器保护单元寄存器等,以及跟踪端口接口和嵌入式跟踪宏单元。这些寄存器对于控制处理器行为和优化系统性能至关重要。

第四章“存储器映射”讨论了存储器的组织方式,包括Bit-banding技术,直接访问别名区和bit-band区,以及ROM存储器表的设计。

第五章“异常”是手册的核心部分,详细解释了异常模型、异常类型、优先级、特权和堆栈处理,以及异常控制权转移、复位机制和启动顺序。这部分内容对理解和解决系统故障、处理中断异常至关重要。

Cortex-M3内核手册为Cortex-M3处理器的使用者提供了全面的技术支持,无论是硬件配置、软件编程还是异常处理,都能从中找到相应的指导和细节说明。通过深入学习和理解这份手册,开发者能够充分利用Cortex-M3的特性,构建出强大而稳定的嵌入式解决方案。

2022-07-14 上传

2022-09-21 上传

2013-06-30 上传

2013-05-10 上传

2022-09-22 上传

2015-10-29 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

節奏

- 粉丝: 1

- 资源: 24

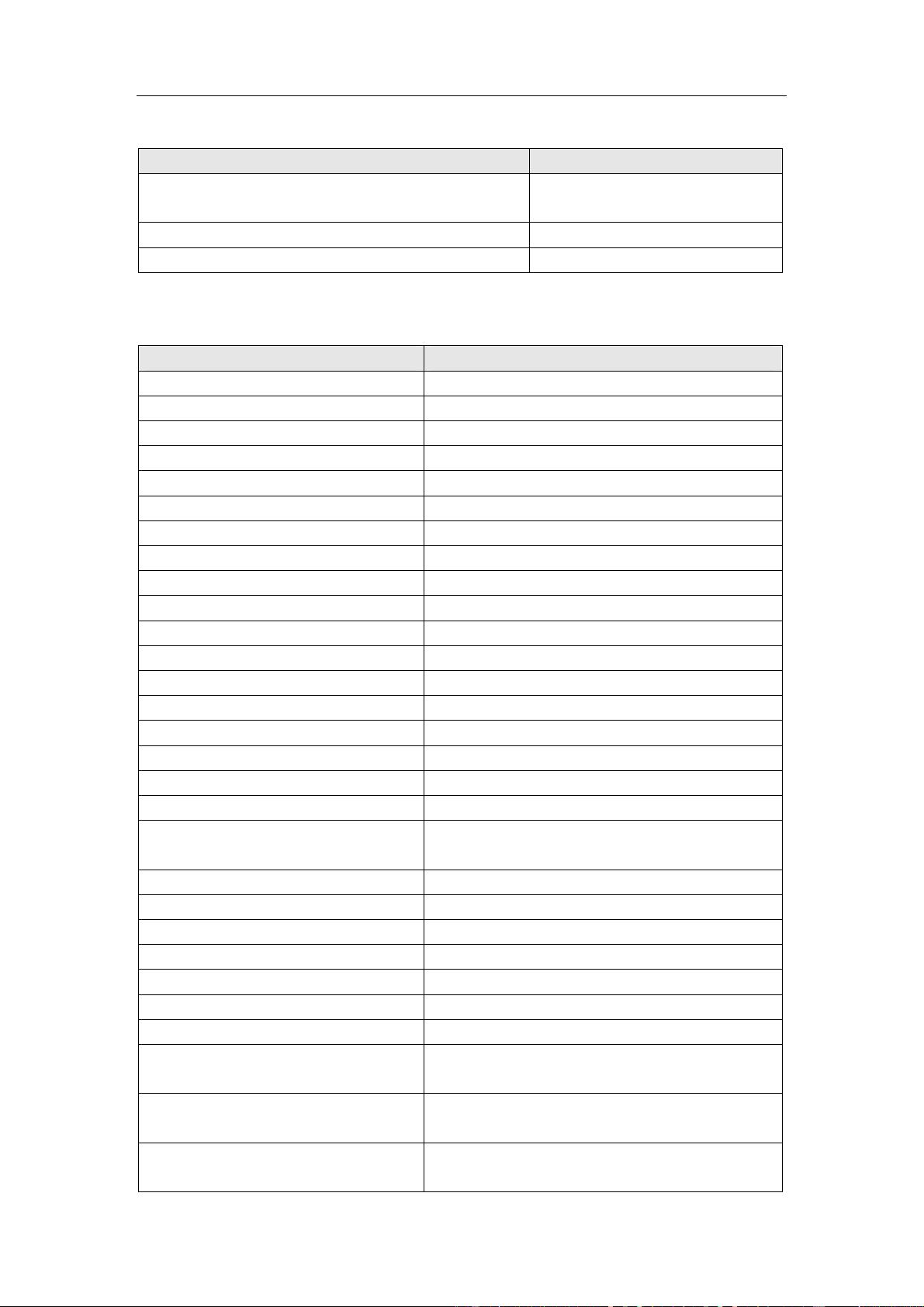

最新资源

- morphline-mr:MapReduce 与 Kite Morphline

- RestApi:laravel学习

- Laravel:Laravel框架5.7.29

- 围攻塔:sgdvxdrfgdrgdr

- MightyCal: Zope/Cocoon Calendar Product-开源

- Android-Project-01

- 用JavaScript路由正交图连接器

- Compiler

- 行业分类-设备装置-跨平台的多屏互动方法、装置及系统.zip

- qnotify:发送2b2t队列通知到电话!

- personaApp

- Bots:只是我所有机器人的一个项目

- Food_Website:响应式食品网站

- bbdoc64V112.zip

- crudASP

- python-LRU缓存.zip