时钟恢复系统 PLL 锁相环设计与仿真

117 浏览量

更新于2024-08-29

收藏 237KB PDF 举报

"基于相位控制技术的时钟恢复系统的PLL锁相环电路设计,包括鉴相器、电荷泵、环路滤波器、压控振荡器和分频器的设计,采用2.5V,0.25μm First Silicon CMOS工艺,具有高速、低噪声特点"

在数字通信系统中,时钟恢复是一项至关重要的技术,它用于从接收到的数据流中恢复出稳定的时钟信号。基于相位控制技术的时钟恢复系统通常采用锁相环(Phase-Locked Loop, PLL)结构。本文重点探讨了设计这样一个系统的PLL锁相环电路。

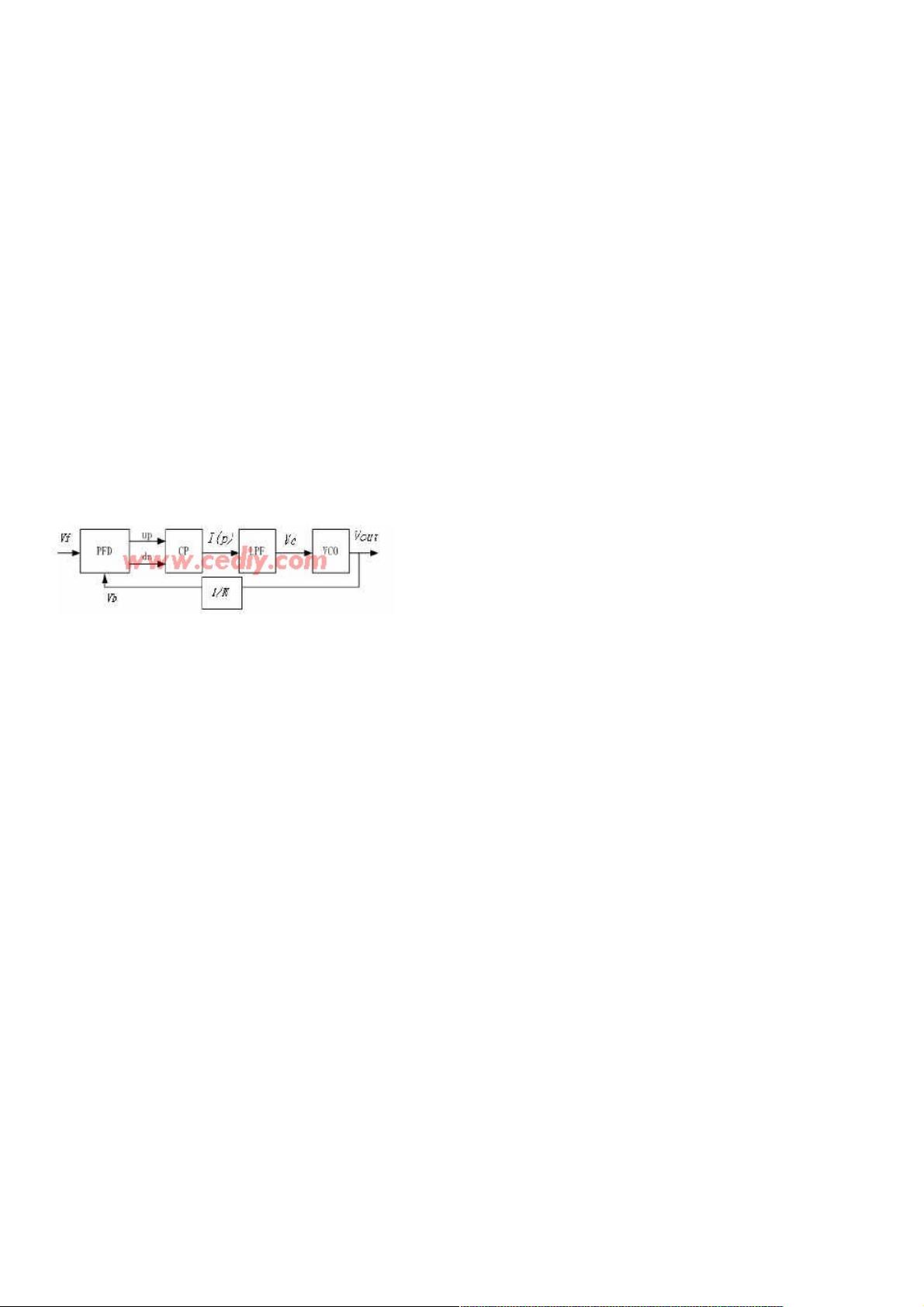

首先,PLL锁相环由多个关键单元组成。鉴频鉴相器(PFD,Phase Frequency Detector)是其核心部分,它的作用是检测输入参考时钟和压控振荡器(VCO,Voltage-Controlled Oscillator)输出之间的相位差,并根据相位差的正负产生相应的控制信号。电荷泵(Charge Pump)接收鉴相器的控制信号,产生电流以调整VCO的频率。环路滤波器(Loop Filter)则平滑电荷泵产生的脉冲电流,将其转化为电压控制信号,确保VCO的频率调整平滑且无抖动。压控振荡器根据这个电压控制信号改变自身的振荡频率,以使输出信号的相位与输入参考信号保持一致。最后,分频器(Frequency Divider)用于将VCO的高频信号分频,以匹配输入参考时钟的频率。

在设计中,作者选择了2.5V,0.25μm的First Silicon CMOS工艺,这有助于减小电路尺寸,降低功耗,同时提高工作速度。通过SPICE仿真平台,作者验证了设计的性能。仿真结果显示,该PLL锁相环的锁定时间仅为2.4us,这意味着系统能快速锁定到输入信号,具有良好的同步能力。此外,输出频谱的高纯度表明了系统的低噪声特性,这对于高速通信和数据传输至关重要。

随着系统级芯片(System-on-a-Chip, SoC)和知识产权核(IP Core)技术的进步,锁相环作为基本的ASIC宏单元,在无线通信和微处理器电路中的应用越来越广泛。特别是在现代通信行业,如蜂窝电话和蓝牙技术,对片内和片间的同步有着严格的要求。因此,设计高速、低噪声的PLL锁相环电路对于满足这些需求至关重要。

本文提出的设计方案考虑了工作频率、工作速度以及相位噪声等多方面因素,优化了锁相环性能,为时钟恢复系统提供了高效的解决方案。这样的设计不仅提高了系统的时钟恢复效率,还降低了噪声对信号质量的影响,有助于提升整体通信系统的性能和可靠性。

2022-07-11 上传

2016-07-07 上传

2023-09-08 上传

2012-05-31 上传

2011-08-06 上传

2022-09-22 上传

2021-11-19 上传

2021-05-23 上传

2022-09-24 上传

weixin_38682518

- 粉丝: 3

- 资源: 935

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程