Copyright © 2009 IEEE. All rights reserved. 3

VERIFICATION OF LOW POWER INTEGRATED CIRCUITS IEEE Std 1801-2009

— Place and Route tools read both the netlist and the UPF files and produce outputs, potentially

including an output UPF file.

UPF is a concise power design intent specification capability. Power design intent can be easily specified

over many elements in the design. A UPF specification can be included with the other deliverables of

intellectual property (IP) blocks and reused along with the other delivered IP. UPF supports various

methodologies through carefully defined semantics, flexibility in specification, and, when needed, defined

rational limitations that facilitate automation in verification and implementation.

A UPF specification defines how to create a supply network to supply power to each design element, how

the individual supply nets behave with respect to one another, and how the logic functionality is extended to

support dynamic power switching to these logic design elements. By controlling the operating voltages of

each supply net and whether the supply nets (and their connected design elements) are turned on or off, the

supply network only provides power at the level the functional areas of the chip need to complete the

computational task in a timely manner.

1.4 Power supply network design intent

Designing electronics to meet low power design constraints requires the specification of a power supply

network that can control the distribution of that supply to minimize energy consumption. UPF supports the

specification of the power supply distribution network so the supply network can be automatically

implemented at a relatively abstract level.

To help manage the complexity of the supply network specification, power domains are defined to group

elements from the logic hierarchy that share common supply needs. By default, all logic elements in a power

domain use the same primary supply. Additional supplies may be defined to serve different uses in a power

domain. In addition to the primary supply, UPF provides well-defined semantics for other supplies for both

verification and implementation contexts.

The supply network consists of supply ports, switches, and supply nets. Supply network objects are defined

within the logical hierarchy relative to the context of a power domain. Supply ports provide the supply

interface to the logical hierarchy and the power domain’s elements. Supply ports also provide the supply

interface to switches. Switches control the supply distribution. Supply nets connect supply ports.

Although there is an obvious inference to the actual wires and ports in the implemented hardware, a UPF

supply network is an abstraction of the electrical network on the chip. UPF defines no routing or layout

information. As the supply network is specified apart from the logic design, the logic design specification

remains independent of a specific power supply network specification.

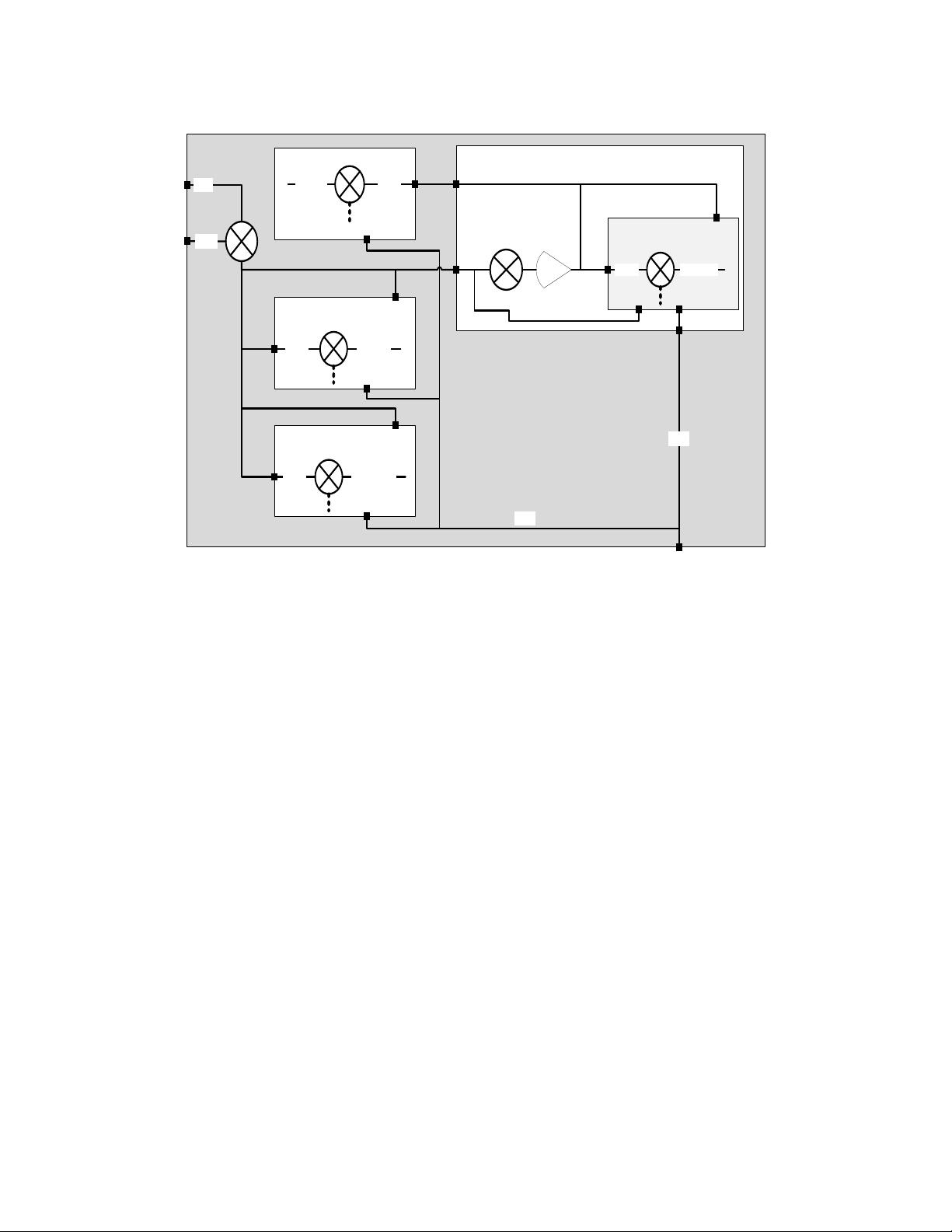

Figure 2

shows an example supply distribution network for a hypothetical chip, mySoC. A top-level power

domain, mySoC_PD defined at the U_top instance level in the logical hierarchy, is defined with three

supply ports, Pbat, Pwall, and GND. These ports represent the off-chip power sources. A single switch

(S1) controls whether the chip receives its supply from Pbat or Pwall. Supply nets connect the output

from S1 to each power domain defined within the top-level power domain. mySoC_PD does not contain

any logic elements other than the root of the design U_top; its purpose is to define the interface to the off-

chip power sources and provide the top-level supply network.

Authorized licensed use limited to: ST Microelectronics. Downloaded on May 27, 2009 at 11:23 from IEEE Xplore. Restrictions apply.