CMOS多频段低噪声放大器设计:单个LNA解决方案

91 浏览量

更新于2024-08-31

收藏 219KB PDF 举报

"本文主要探讨了模拟技术中的CMOS多频段低噪声放大器(LNA)设计,针对无线通信技术日益增长的需求,提出了一种并行式多频段LNA解决方案,旨在解决多频段移动终端接收系统中的关键问题。传统方法包括并联多个单频段LNA、开关式LNA和宽带LNA,但这些方法各有弊端,如功耗大、占用面积多、成本增加以及干扰信号放大等。设计中提出的并行式多频段LNA通过优化电路结构,实现了单个LNA同时工作在多个频段的功能,有效降低了功耗和芯片面积,提高了系统的效率和性能。"

在无线通信系统中,低噪声放大器(LNA)作为接收链的第一级,对于保持信号质量和降低系统噪声至关重要。传统的多频段LNA设计策略包括并联多个单频段的LNA,这可能导致高功耗和芯片面积的显著增加,不适应接收标准的持续扩展。开关式LNA虽然可以节省功耗,但仅能工作在一个频段,无法满足多频段同时工作的需求。而宽带LNA虽能覆盖多个频段,却可能引入不必要的干扰信号。

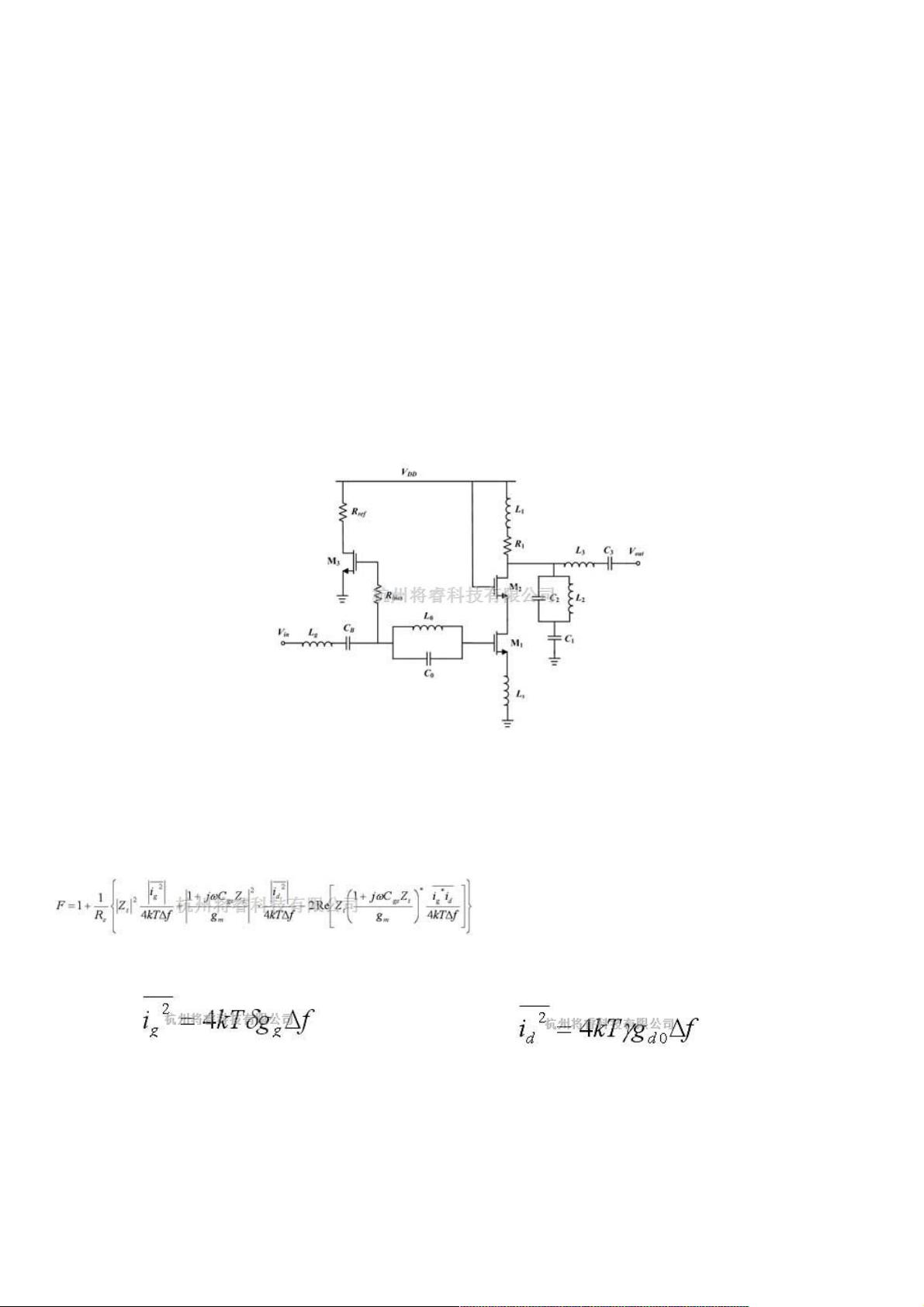

本设计采用了一种创新的并行式多频段LNA架构,它以单个LNA单元实现多频段操作,降低了系统复杂性,减小了芯片面积,同时减少了不必要的功率消耗。具体实现方式是通过精细的电路设计,例如采用具有源极电感的共源MOSFET结构,并对噪声性能进行优化。在1.8GHz、1.9GHz和2GHz相近的频段,设计了一个0.9/1.9GHz双频段LNA,通过扩大中心频率1.9GHz的带宽,覆盖1.8至2GHz,从而覆盖所需的四个频段。

在噪声分析方面,高频MOSFET的噪声源主要包括漏电流噪声和栅电流噪声。通过计算输入级品质因数Qs,可以优化噪声系数,确保在功耗限制和阻抗匹配条件下,LNA具有良好的噪声性能。噪声系数的计算涉及源极电阻Rs、栅极和源极的阻抗以及MOSFET的栅电流和漏电流噪声。

此外,为了进一步提升LNA的性能,还需要考虑增益、线性度、电源抑制比(PSRR)以及输入和输出阻抗匹配等问题。通过精心选择元器件参数和采用先进的工艺技术,可以在保证多频段工作的同时,确保LNA在各个频段都有稳定的增益和良好的线性响应,抑制电源噪声对信号的影响,并与前端天线和后端信号处理电路实现良好的接口匹配。

该设计展示了在模拟技术中,通过CMOS工艺实现多频段低噪声放大器的一种有效方法,这对于推动无线通信设备的发展,特别是支持多标准的移动终端,具有重要的实践意义。通过不断的电路优化和技术创新,未来多频段LNA的设计将进一步提升性能,满足更多频段、更高效能的无线通信需求。

2024-02-21 上传

2023-06-01 上传

2023-07-14 上传

2023-07-25 上传

2023-05-12 上传

2023-06-26 上传

2023-09-12 上传

2024-04-10 上传

2023-06-22 上传

weixin_38588854

- 粉丝: 11

- 资源: 958

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展