Verilog HDL:数据流与行为级建模解析

176 浏览量

更新于2024-08-28

1

收藏 323KB PDF 举报

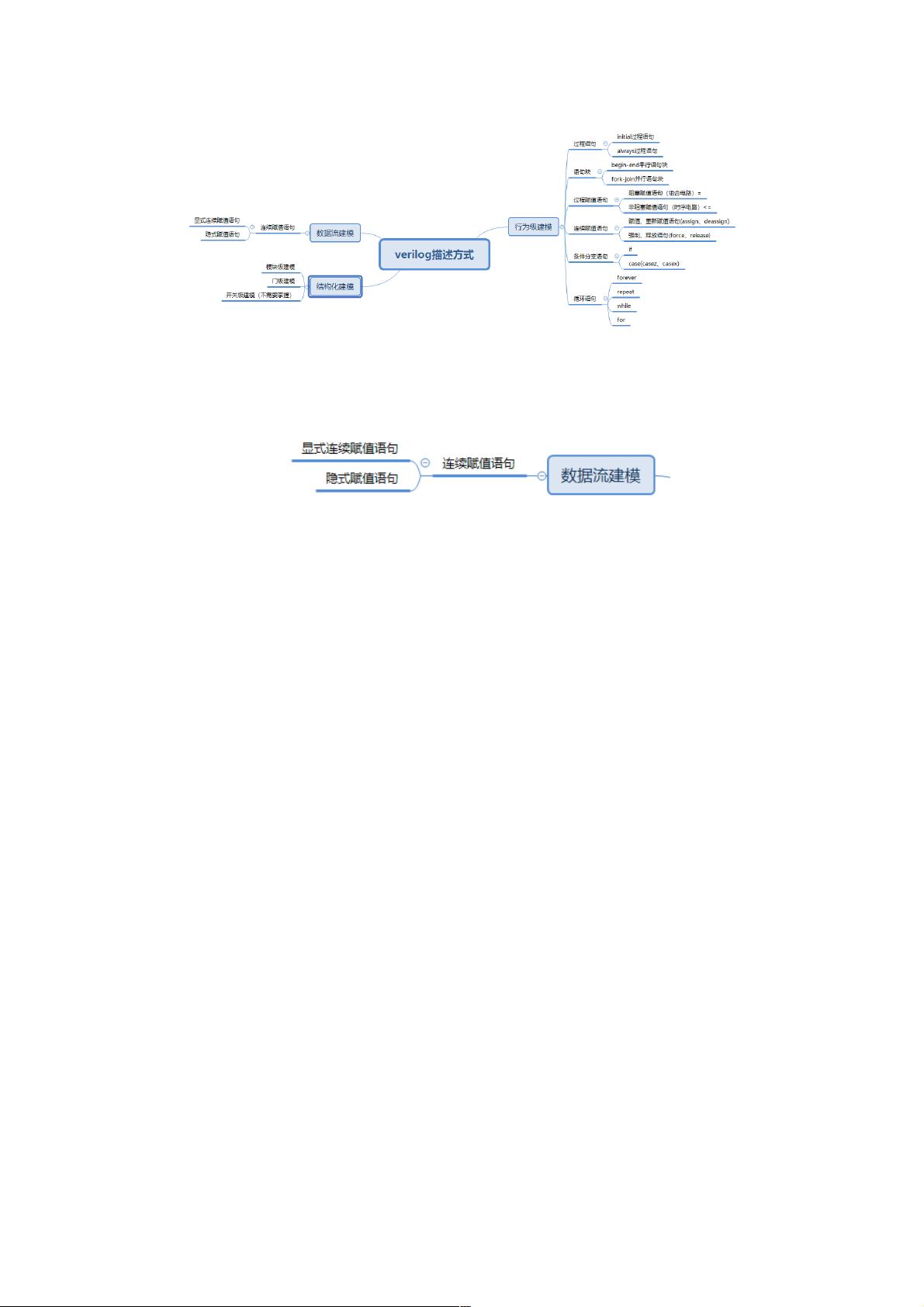

"本文将详细解释Verilog HDL的三种描述方式:数据流建模、行为级建模以及结构级建模。数据流建模主要通过连续赋值语句实现,包括显式和隐式赋值。行为级建模则从电路的外部行为角度进行描述,其中涉及initial和always过程语句,以及语句块的使用。"

在数字电路设计中,Verilog HDL是一种广泛使用的硬件描述语言,它提供了多种描述方式来构建和仿真电路。下面我们将深入探讨这三种描述方式:

1. **数据流建模**:在组合逻辑电路中,数据流建模是最基础的方式,它反映了数据如何随输入信号的变化而流动。这种建模的核心是连续赋值语句,适用于连线型变量(wire)。连续赋值有两种形式:

- **显式连续赋值**:首先声明变量类型和位宽,然后使用`assign`关键字赋值,可以指定延迟。

- **隐式连续赋值**:无需`assign`关键字,但包含驱动强度和延迟信息。

2. **行为级建模**:行为级建模更注重电路的行为表现,而不是物理实现。它分为过程语句和语句块。

- **过程语句**:

- **initial过程语句**:用于仿真初始化,如设定激励向量,仅在仿真开始时执行一次。

- **always过程语句**:根据指定的敏感事件列表(如信号的上升沿或下降沿)执行语句块。时序电路描述中,需合理选择敏感事件。

- **语句块**:当有多个语句需要一起执行时,可以使用`begin-end`或`fork-join`来组织代码。

3. **结构级建模**:结构级建模模仿硬件结构,用实例化(instance)子模块的方式描述电路。它将复杂电路拆分成基本模块,并连接这些模块,形成整体的电路结构。每个子模块可以用数据流或行为级描述,或者进一步分解为更低层次的结构。

在Verilog HDL中,不同的描述方式适用于不同的设计需求。数据流建模适合简单逻辑操作,行为级建模则能表达复杂的时序逻辑,而结构级建模则用于构建大型系统的模块化设计。理解并灵活运用这些描述方式,对于设计高效、可读性强的Verilog代码至关重要。

2014-10-25 上传

2022-09-20 上传

2020-12-09 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情