两级运放设计与分析:提升增益与输出电压摆幅

"该资源是一份关于两级运算放大器的西交大内部课件,主要讲解如何设计两级共源共栅运算放大器,用于满足特定的性能指标,如增益、带宽和相位裕度。课程涵盖了差动放大器的直流扫描、交流和瞬态分析方法,并使用SMIC0.18um3.3V CMOS工艺的晶体管模型。"

本文将深入探讨两级放大器的设计,特别是共源共栅结构的第一级和第二级运放,以及在设计过程中的参数计算和优化。

两级运放通常由一个高增益的第一级和一个增大输出电压摆幅的第二级组成。在本例中,目标是设计一个当VDD为3.3V时,功率P为16.5mW,相位裕度PM大于60度,直流增益Av为80dB(相当于1000倍),单位增益带宽为150MHz的运算放大器。

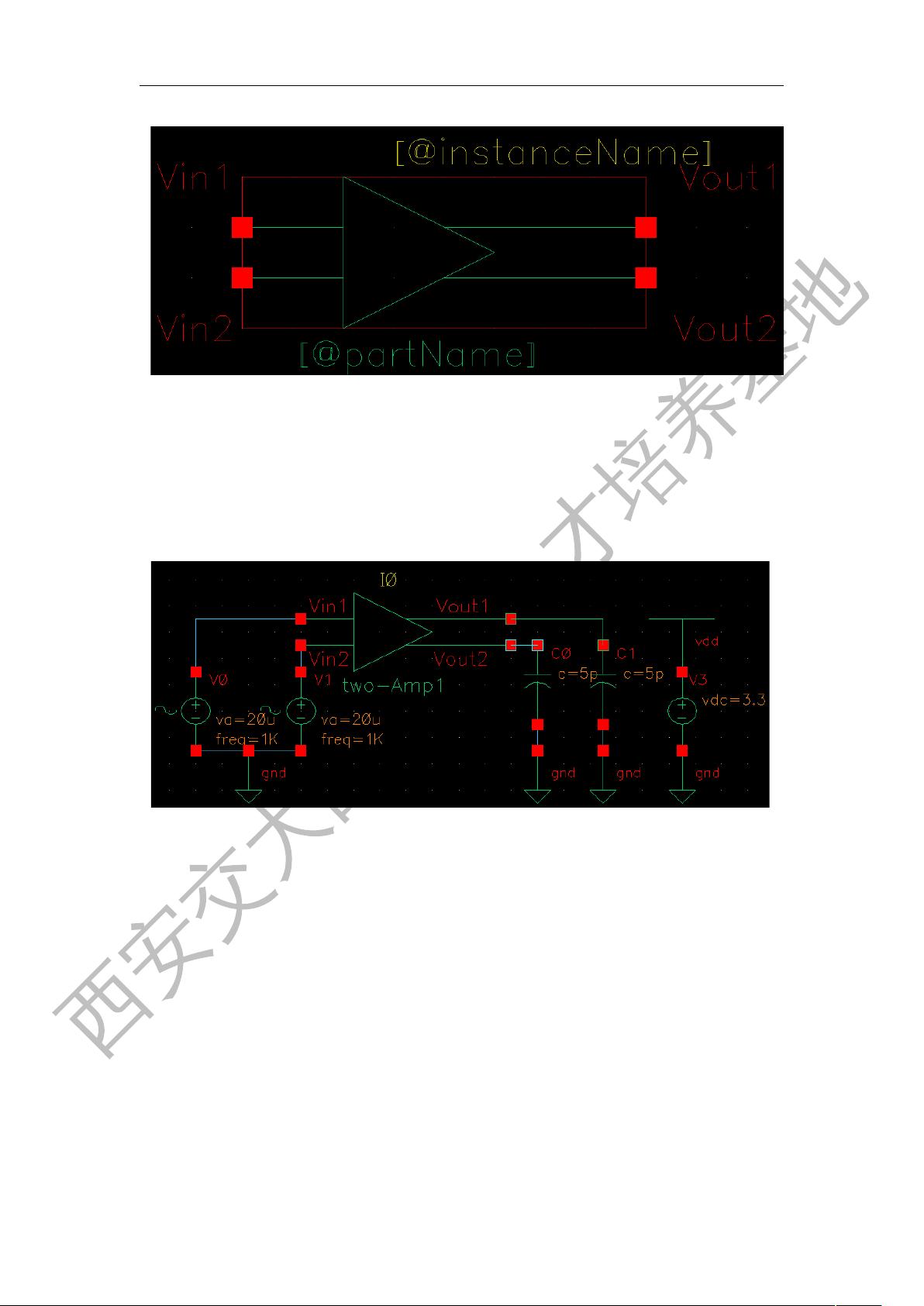

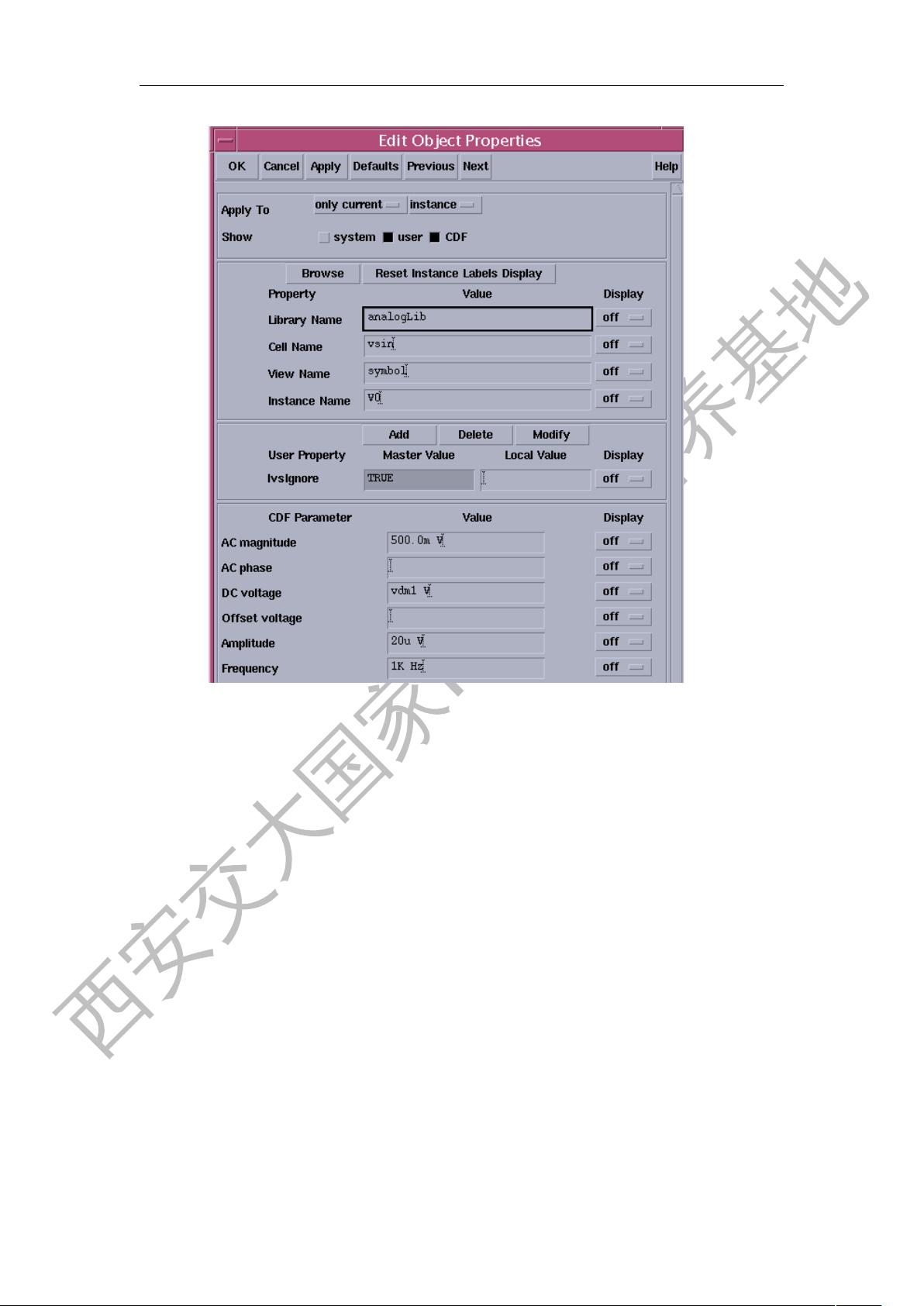

设计步骤首先从启动CADENCE工具开始,通过输入命令`cds.setup icfb&`进入电路设计环境。第一级电路采用套筒式共源共栅结构,这种结构可以提供高增益。设计时需注意mos管的衬底连接规则,即PMOS管的衬底接电源,NMOS管的衬底接地,并直接用电压源提供偏置电压。

参数计算是设计的关键环节。在给定的条件中,总电流IDS为16.5mW / 3.3V = 5mA,第一级和第二级分别分配3mA和2mA。在第一级中,由于两条支路对称,所有非M8的MOS管电流均为1.5mA,M8的电流为两个输入支路电流之和,即3mA。

过驱动电压(VOD)的分配基于mos管的电流需求。较大的电流对应较大的过驱动电压,例如M8的VOD设为0.4V。对于其他MOS管,过驱动电压的分配应确保足够的电流流动,但不会过度驱动导致效率降低或性能损失。

在实际设计中,还需要考虑mos管的电容特性(COX),以及衬底电荷系数un和up。这些参数影响mos管的开关速度和静态工作点。此外,选择合适的晶体管模型(如p33和n33)对于确保电路在0.18um CMOS工艺下的性能至关重要。

交流和瞬态分析是验证设计是否符合预期的关键步骤。差动放大器的DC扫描分析检查静态工作点,AC分析则关注频率响应,而瞬态分析则揭示电路在不同时间尺度上的动态行为。

设计两级运算放大器涉及多方面的工程判断和计算,包括增益、带宽、相位裕度和功率的平衡,以及mos管参数的选择与优化,以实现高性能的模拟电路。通过这样的实践,学生能够深入理解模拟电路设计的核心概念和技术。

2019-04-03 上传

2023-05-26 上传

2021-09-26 上传

2009-11-15 上传

2023-05-26 上传

whl2018

- 粉丝: 1

- 资源: 5

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫