高速DAC杂散源定位与解决策略

需积分: 40 153 浏览量

更新于2024-08-20

1

收藏 1.26MB DOCX 举报

本文主要探讨了高速数字模拟转换器(DAC)中出现的杂散问题,特别是近端杂散的定位方法。文档介绍了几种可能的杂散来源,并提供了定位和解决问题的流程。

在高速DAC中,杂散噪声的产生可能源于多个因素。首先,直接数据频率合成器(DDS)由于其高频率变换能力和低相位噪声特性而广泛使用,但也存在相位截断杂散和相位-幅度转换相关的杂散,这些是由DDS设计中有限的相位和幅度分辨率引起的。其次,DAC自身的非理想特性,如开关行为,可能导致基波和镜像谐波的功率增强,特别是在低阶谐波上。此外,系统时钟与内部分谐波时钟(如SYNC_CLK)的混合也可能产生杂散。

定位杂散源的关键在于观察杂散噪声相对于DDS/DAC输出基波的频率偏移。通过改变DDS的频率调谐字,可以追踪这些杂散噪声的频率变化。如果杂散的频率偏移随着调谐字的变化而变化,那么DDS/DAC很可能是杂散源。反之,如果频率偏移保持不变,这可能意味着杂散来源于DDS电源的耦合或者参考时钟源的问题。

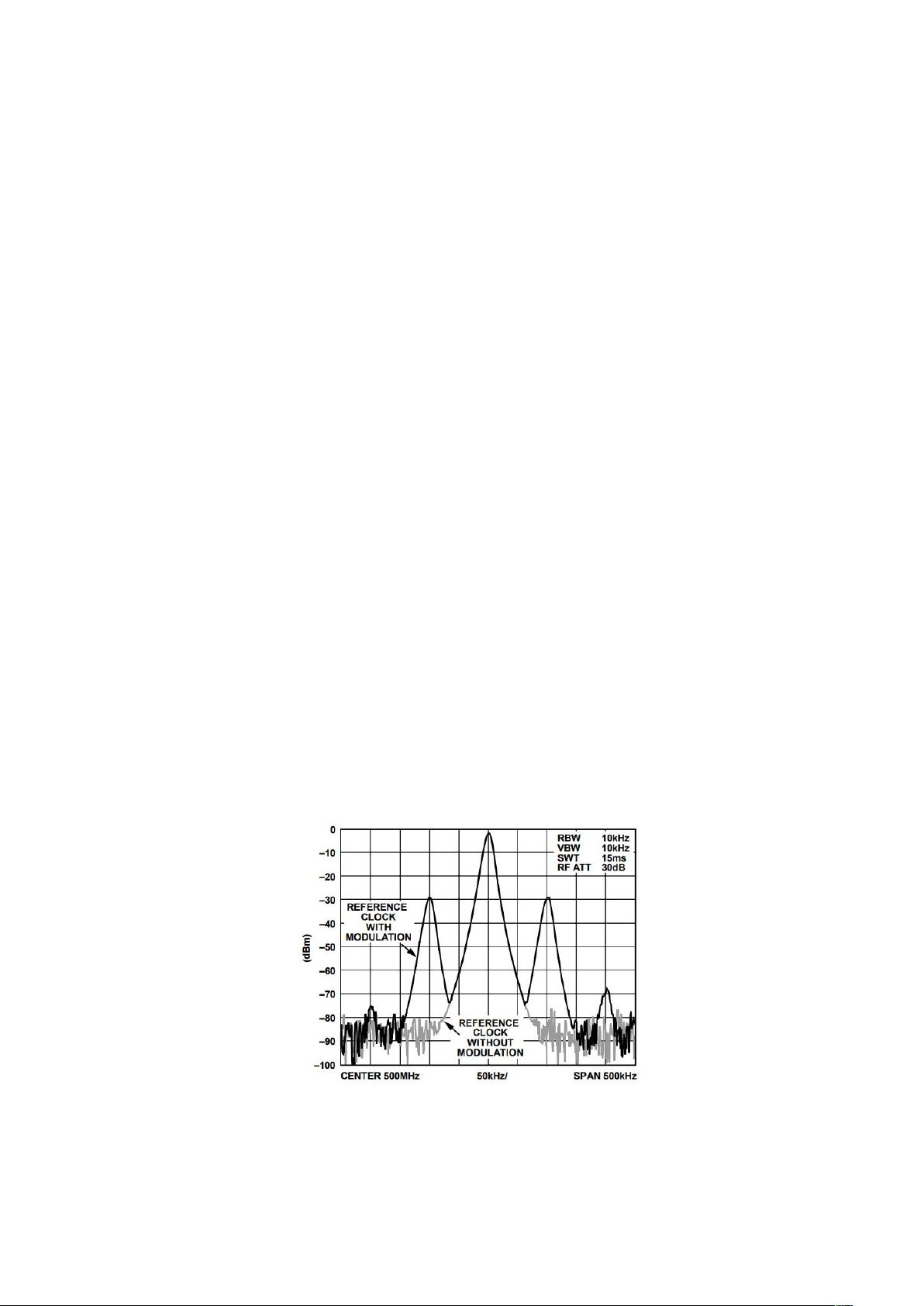

对于参考时钟源产生的杂散,文档通过实例进行了详细说明。图1展示了带有100kHz AM调制的500MHz参考时钟,其调制不影响频率偏移,但会影响杂散的幅度。图2显示了在四个不同的DDS载波下,参考时钟杂散的频率偏移保持恒定,但幅度会根据参考时钟与DDS载波频率的比例变化,遵循20log(x)的规律。

解决杂散问题的步骤通常包括:

1. 确定杂散是否随DDS调谐字变化而变化,以识别可能的来源。

2. 检查DDS电源,查找可能的耦合噪声。

3. 分析参考时钟源,检查其是否包含调制或其他不期望的频率成分。

4. 如果使用了内部参考时钟乘法器(PLL),考虑其可能引入的固定边带杂散。

通过上述步骤,工程师能够更有效地诊断和解决高速DAC中的杂散问题,从而提高系统性能。在实际应用中,可能还需要考虑滤波器设计、电路布局优化以及其他信号完整性措施来进一步减少杂散的影响。

2020-07-25 上传

2021-06-24 上传

2024-07-16 上传

2020-07-25 上传

2022-12-25 上传

2022-06-24 上传

2022-11-03 上传

天下无敌小霸王

- 粉丝: 156

- 资源: 16

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码