CMOS触发器CP边沿工作特性分析与异常研究

105 浏览量

更新于2024-08-31

收藏 301KB PDF 举报

"CMOS触发器在CP边沿的工作特性研究"

CMOS触发器是数字集成电路中的关键组件,尤其在时序逻辑电路中扮演着重要角色。时钟脉冲(CP)的边沿时间对触发器的性能至关重要,因为它们决定了触发器能否准确地捕获和传递数据。在CP边沿陡峭的情况下,即上升时间和下降时间较短,触发器的可靠性得以保证。CMOS电路的基本触发单元通常由传输门和或非门构建的主从结构组成,数据通过传输门进入电路。

然而,当CP边沿时间过长时,可能会引发一系列问题。首先,长时间的CP边沿可能导致触发器无法正确响应,这可能是因为在时钟边沿变化期间,数据未能完全稳定,从而造成数据的错误转换。其次,为了确保触发器的正常工作,必须限制CP边沿时间,并且需要理解这个限制与触发器参数之间的关系。这包括计算和测量CP边沿时间的方法,以便在设计和使用中避免触发器的异常行为。

在研究中,通过标准的CMOS CD4000系列、高速CMOS 74HC和74HCT系列的触发器作为实验样本,研究人员深入探究了CP边沿时间过长时的异常现象及其成因。通过建立CMOS触发器在CP边沿工作的电路模型,可以更深入地理解触发器的工作原理,同时揭示CP边沿时间与触发器参数之间的定量关系。

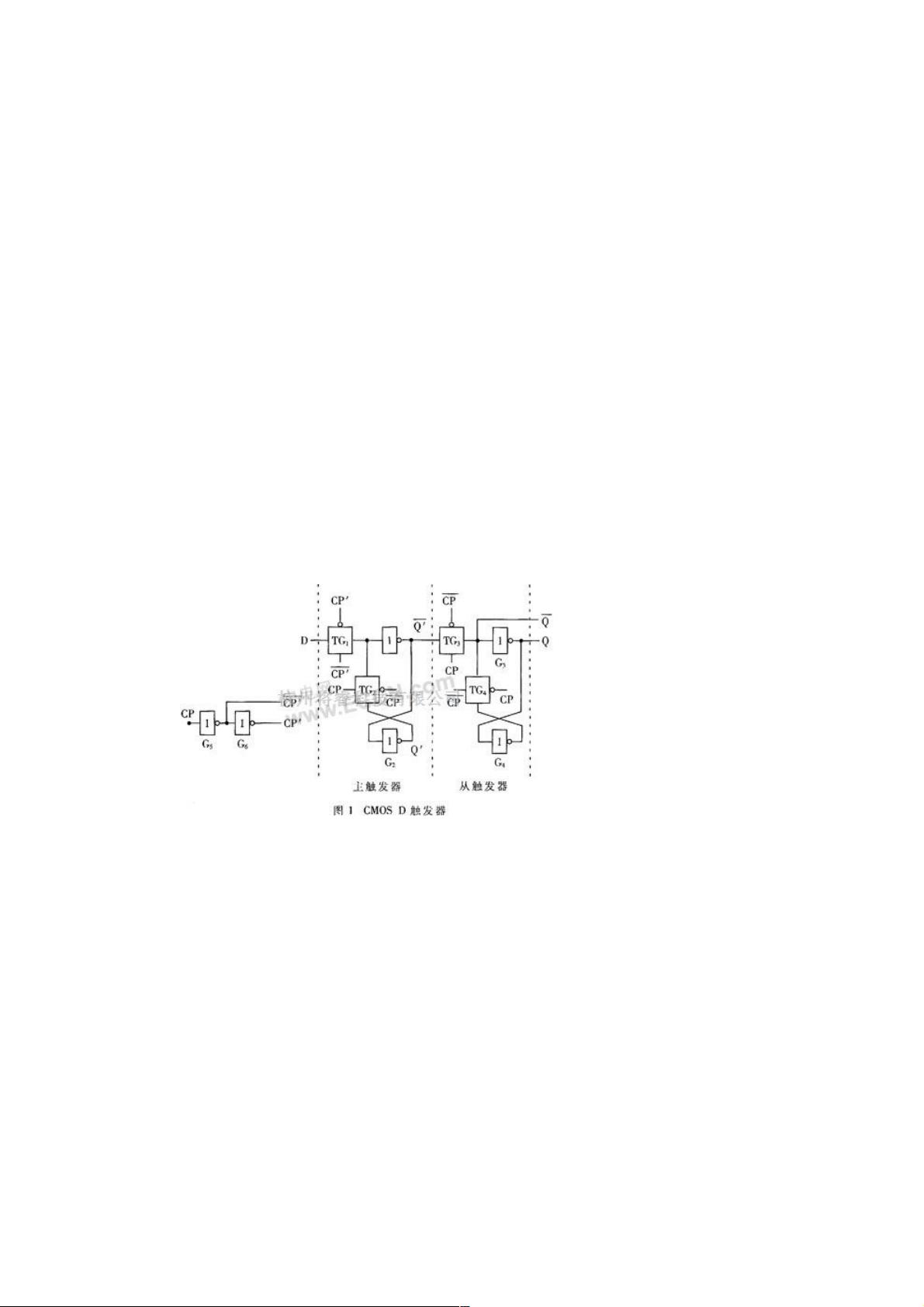

以CMOS D触发器为例,该触发器采用主从结构,由传输门和反相器构建。主触发器负责在时钟边沿捕获数据,而从触发器则在下一个时钟周期保持状态。传输门TG1、TG2与反相器G1、G2组成主触发器,而TG3、TG4与G3、G4则构成从触发器部分。当CP上升时,数据被锁定在主触发器中,而在CP的下降沿,数据从主触发器传递到从触发器,从而实现状态的稳定存储。

在实际应用中,对于CMOS触发器,必须考虑CP边沿时间与触发器建立时间、保持时间等参数的匹配。建立时间是指数据信号必须在CP上升沿之前稳定的时间,而保持时间则是数据信号在CP上升沿后必须保持稳定的时间。如果CP边沿时间过长,可能导致数据在触发器内部无法及时稳定,从而违反这些时间要求,引起触发器工作异常。

因此,对CMOS触发器在CP边沿的工作特性的深入研究不仅有助于理解触发器的内在机制,而且对优化设计、提高电路性能和确保系统可靠性具有重要意义。通过精确计算和测量CP边沿时间,可以有效地预防潜在的问题,确保触发器在各种应用场景中都能稳定、可靠地工作。这对于CMOS触发器的正确使用、设计改进以及提升产品整体质量提供了坚实的理论基础。

110 浏览量

2292 浏览量

2023-07-14 上传

466 浏览量

240 浏览量

2021-09-16 上传

115 浏览量

2870 浏览量

127 浏览量

weixin_38690376

- 粉丝: 2

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程