嵌入式USB2.0主机控制器IP核设计与实现

179 浏览量

更新于2024-08-30

收藏 315KB PDF 举报

"一种嵌入式USB2.0主机控制器IP核的研究与设计"

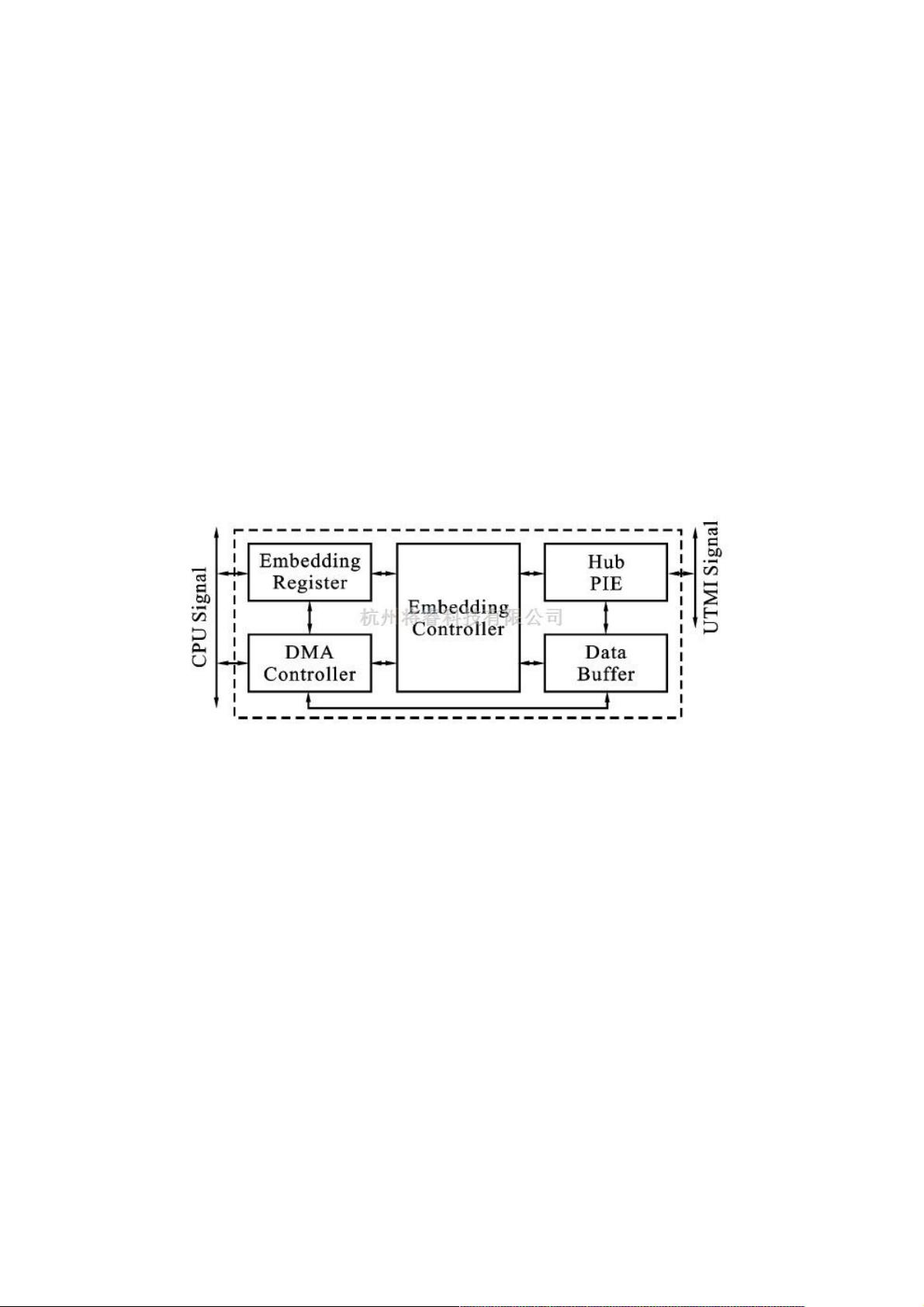

本文主要探讨了一种使用Verilog HDL语言设计实现的嵌入式USB 2.0主机控制器IP核,该核适用于嵌入式系统,能独立运作并进行数据传输。作者首先概述了嵌入式USB主机设计的背景,指出USB自诞生以来,经过2.0版本的规范,已经成为成熟且广泛使用的接口标准。在USB的架构中,主机扮演着关键角色,负责所有数据传输的发起和控制。

设计中,作者强调了主机控制器IP核的结构划分和各个模块的设计分析。USB主机控制器通常包括以下关键模块:

1. 主控制器:作为核心组件,主控制器负责协调和管理其他所有模块,确保USB通信的正确执行。它处理USB协议的解析、数据包的发送和接收,以及错误检测和恢复。

2. 总线管理器:负责仲裁总线使用权,确保多个设备的有序访问,防止冲突。

3. USB物理层:实现USB的物理接口,包括信号传输、时钟恢复和信号完整性保证。

4. 数据缓冲区:用于存储待发送和接收的数据包,确保数据传输的连续性和一致性。

5. 事务传输器:负责数据包的传输,包括控制、批量、中断和同步传输四种类型。

6. 描述符管理器:处理设备配置、接口和端点描述符,帮助主机了解USB设备的特性和功能。

7. 中断和事件处理:提供中断机制,通知主机控制器关于设备连接、状态改变或数据传输完成等事件。

8. 协议栈:理解和执行USB协议,包括枚举、配置、设备状态管理和错误处理等。

在设计完成后,作者采用nc2verilog进行功能仿真,这是一种常用的Verilog代码验证工具,能够模拟IP核的行为,检查其设计是否符合预期。接着,通过FPGA(Field-Programmable Gate Array)验证方案,将IP核部署在可编程逻辑器件上进行实际硬件测试,以验证其在真实环境下的性能和稳定性。

通过nc2verilog仿真和FPGA验证,设计的嵌入式USB 2.0主机控制器IP核表现出良好的功能和兼容性,证明了它可以成功应用于各种嵌入式系统,扩展USB技术在非PC平台的应用范围,例如嵌入式设备间的点对点通信,实现更灵活的数据交换。

这项工作为嵌入式系统提供了自定义的USB主机控制器解决方案,推动了USB技术在嵌入式领域的应用,特别是在缺乏嵌入式操作系统支持或对成本和功耗有严格要求的场合,这样的IP核设计具有显著的实用价值和市场前景。

weixin_38637764

- 粉丝: 10

- 资源: 953

最新资源

- node-v7.8.0-linux-s390x.tar.gz

- sunrise-challenge-backend:我对日出挑战的建议

- 施工管理资料表格-040103_卷材防水层检验批质量验收记录表

- monocle-3-a-peek-into-the-future:关于Scala光学未来的演讲

- 用梯度下降算法开发的rbf神经网络曲线拟和程序.rar

- 软件缺陷管理小程序-毕业设计,基于微信小程序+SSM+MySql开发,源码+数据库+毕业论文+视频演示

- MXL1014 Dual Quad Precision Op Amps-综合文档

- 三维弹性波地下波场正演模拟

- 小程序源码 ViewPager使用不错的代码.rar

- ASP窗帘销售网站平台设计(源代码+论文).rar

- 语言学习AI智能助手app ui .fig素材下载

- 西门子WINCC_Flexible_精简屏快速组态入门.rar

- 在线选课小程序-毕业设计,基于微信小程序+SpringBoot+MySql开发,源码+数据库+开题报告+毕业论文+视频演示

- 橙色黄金矿工挖宝游戏小程序源码.zip

- jdoodle-client-example:JavaScript JDoodle API客户端示例

- matlab如何敲代码-irf:使用随机森林的眼动事件检测