详解ModelSim仿真流程:从入门到高级应用

需积分: 10 68 浏览量

更新于2024-08-02

收藏 1018KB PDF 举报

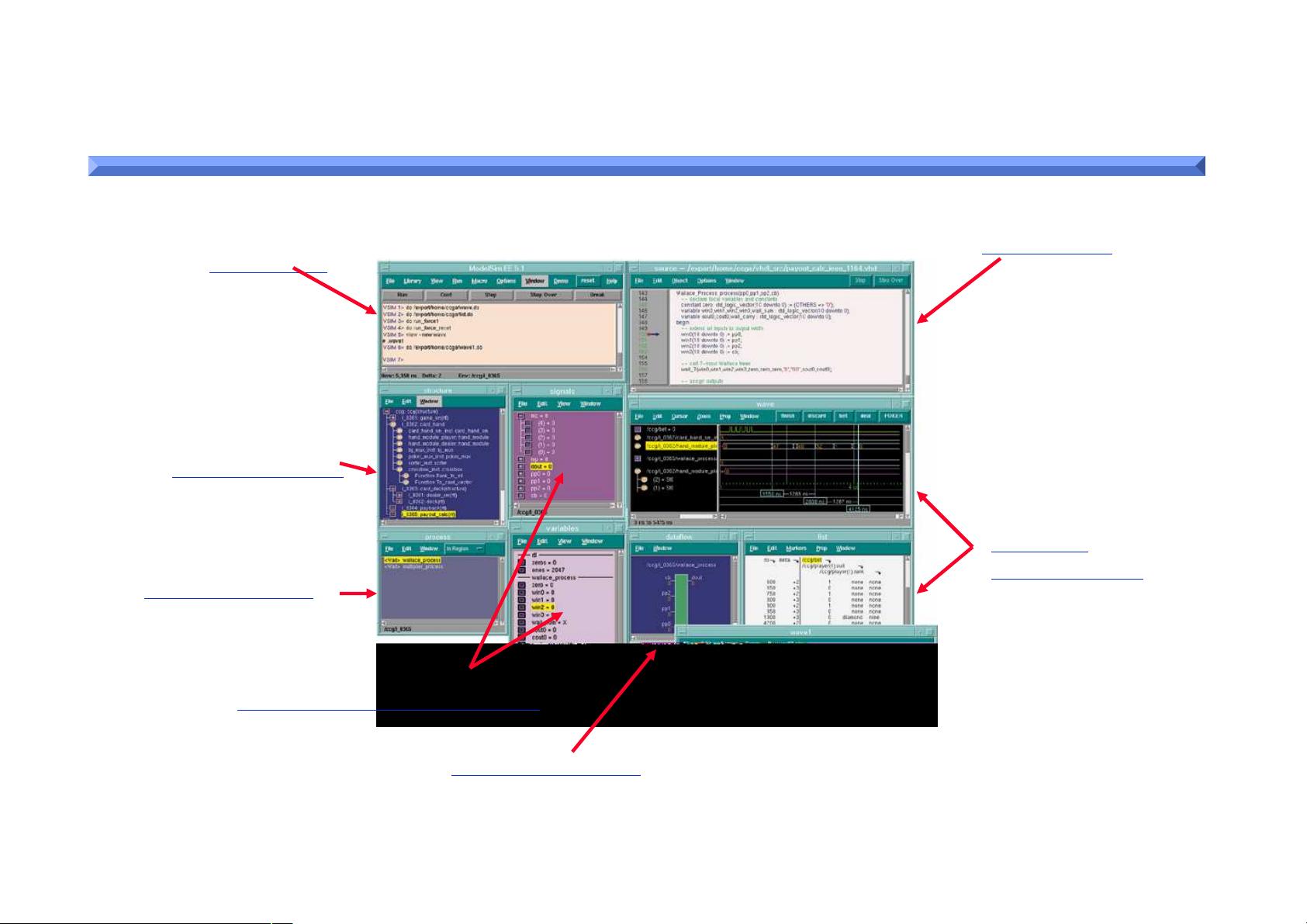

ModelSim仿真流程是一种广泛应用于硬件描述语言(HDL)设计验证的工具,特别是在数字电路设计领域。以下是一份详细的ModelSim仿真流程步骤:

1. **环境配置**:

- 首先,确保你已经安装了ModelSim,通常它提供了Verilog和VHDL两种语言的支持。选择适合你的设计的版本(如ModelSim/VHDL、ModelSim/Verilog等)。

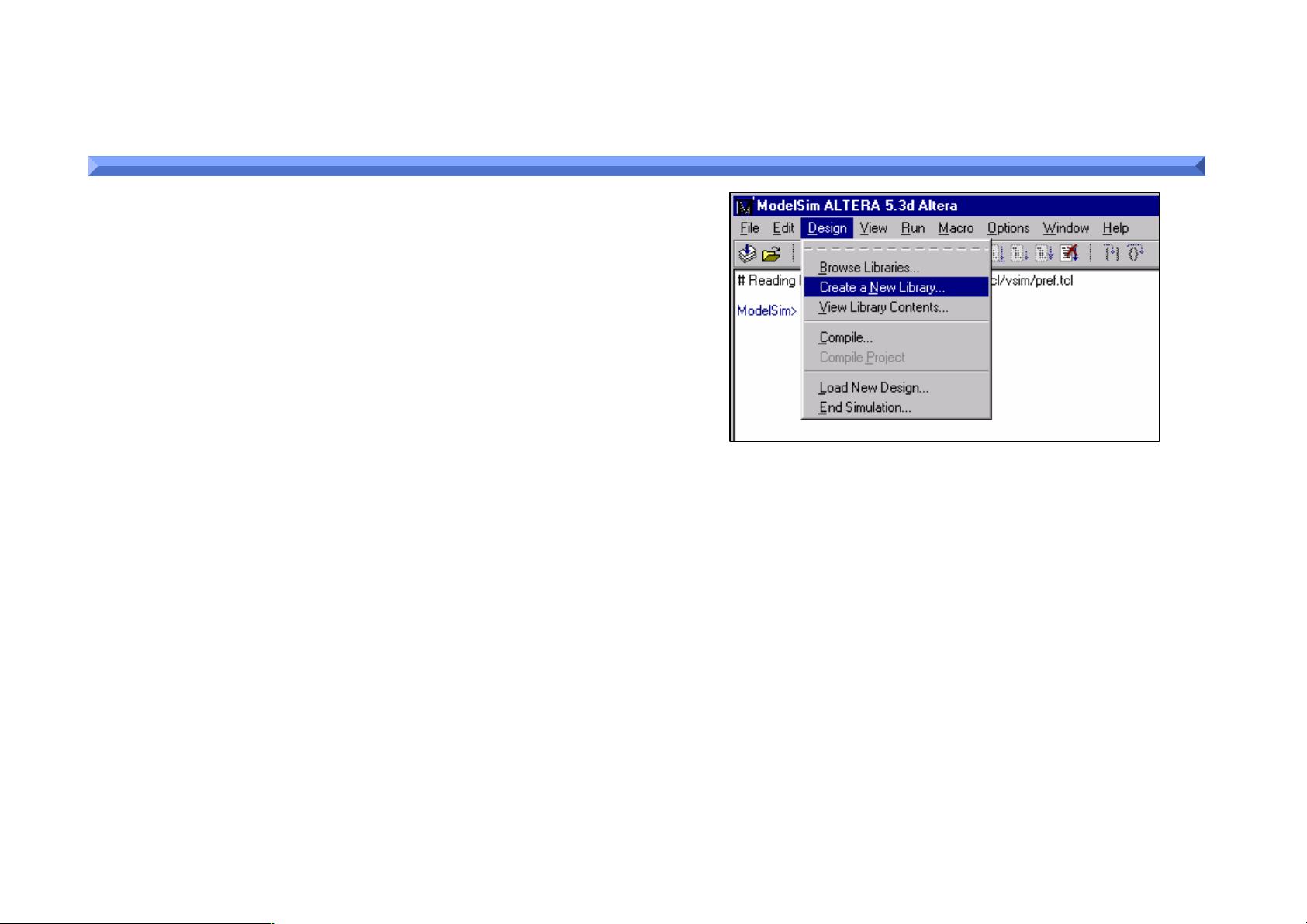

2. **项目设置**:

- 创建一个新的项目,并将设计文件(如RTL级代码,即 Register Transfer Level)导入,包括你的源代码文件(如Verilog或VHDL模块)、网表文件(Synthesis后的结果)和设计结构文件(如`main`、`structure`、`process`等)。

3. **语言预处理**:

- 在ModelSim中,使用`vsim`命令启动仿真器,预处理你的设计文件,这可能包括宏定义、参数化等。

4. **仿真初始化**:

- 设置时钟周期(`timescale`),定义仿真时间范围(`$stop_time`)以及仿真信号的初始状态(如波形设置)。

5. **设计编译**:

- 在仿真器中,通过`work`或`uvm`关键字编译设计,确保所有的模块都已正确加载和连接。

6. **运行仿真**:

- 使用`run`命令启动仿真,从指定的时间点开始,或者从设计的起始点开始。你可以设置断点和观察点来检查信号的行为。

7. **数据流分析**:

- 数据流仿真允许你在设计中查看信号的流动和操作,这对于理解设计行为非常有用。

8. **波形和信号分析**:

- ModelSim提供波形视图(Waveform)功能,可以观察信号的变化情况,同时也可以查看变量值和逻辑状态。

9. **调试与错误检查**:

- 如果发现异常,可以使用`display`或`probe`语句检查信号值,使用`assert`进行条件断言,协助定位问题。

10. **仿真结束**:

- 当达到预设的停止条件或者完成所有测试后,使用`quit`命令结束仿真。

11. **结果分析与报告**:

- 分析仿真结果,确保设计符合预期,生成详细的仿真报告,记录关键信号变化和测试结果。

12. **模型库和扩展**:

- ModelSim支持多种标准,如IEEE 1364-1995 Verilog、SDF1.0-3.0等,以及特定OEM或厂商的库。

13. **与其他工具集成**:

- ModelSim可以与Quartus等其他EDA工具集成,提高整体设计流程的效率。

通过以上步骤,ModelSim可以帮助硬件设计师验证设计的正确性,优化性能,并在实际应用前发现潜在的问题。

145 浏览量

218 浏览量

2022-06-20 上传

点击了解资源详情

106 浏览量

点击了解资源详情

241 浏览量

izeukin

- 粉丝: 2

最新资源

- 海盗船HS40耳机v2.0.37驱动更新,提升游戏音效体验

- Vue TodoList项目开发与部署指南

- Sengoku ixa-meta:适用于Firefox Android的Sengoku IXA转换工具

- 机械模具绘图经验技巧与案例分析

- Plexy:用Elixir打造优质API的全新工具包

- 实现jQuery标签添加与删除功能的代码教程

- Java编程作业解析与指南

- 结构力学教程基础理论精讲

- 季度统计报表后台网站模板-2016年第一季度

- 探索流星技术:kikombe-meteor项目解析

- CreaTechs:打造无障碍残疾人工作门户

- C# 异步Socket客户端实现与字符接收功能详解

- Invoicer:一款为.NET平台快速生成PDF发票的C#库

- Delphi7实现FTP上传下载功能及断点续传教程

- 创意404页面动画模板:HTML5太空人

- 蒙恬行动笔迹王myInk:电脑手写输入与分享新体验