使用VHDL进行电路设计

需积分: 10 39 浏览量

更新于2024-07-27

收藏 5.01MB PDF 举报

"CircuitDesignwithVHDL" 是一本由 Volnei A. Pedroni 所著的书籍,专注于介绍使用 VHDL 进行电路设计的方法。这本书由 MIT Press 出版,详细讨论了使用 VHDL 这一硬件描述语言进行电子电路设计和系统设计的实践与理论。

在《CircuitDesignwithVHDL》中,作者 Volnei A. Pedroni 首先介绍了VHDL(Very High Speed Integrated Circuit Hardware Description Language),这是一种用于电子设计自动化(EDA)的高级语言,特别适用于数字系统的建模和仿真。VHDL 允许设计师以文本形式描述电子电路和系统的行为和结构,从而实现逻辑设计、验证、综合和仿真。

第一部分“CIRCUIT DESIGN”开始时,书中的第一章“Introduction”讲解了 VHDL 的基本概念。这一章可能会涵盖以下内容:

1.1 关于VHDL:

- VHDL 的起源和发展,作为 IEEE 标准的演变过程。

- VHDL 的主要用途,包括数字系统设计、FPGA 和 ASIC 设计。

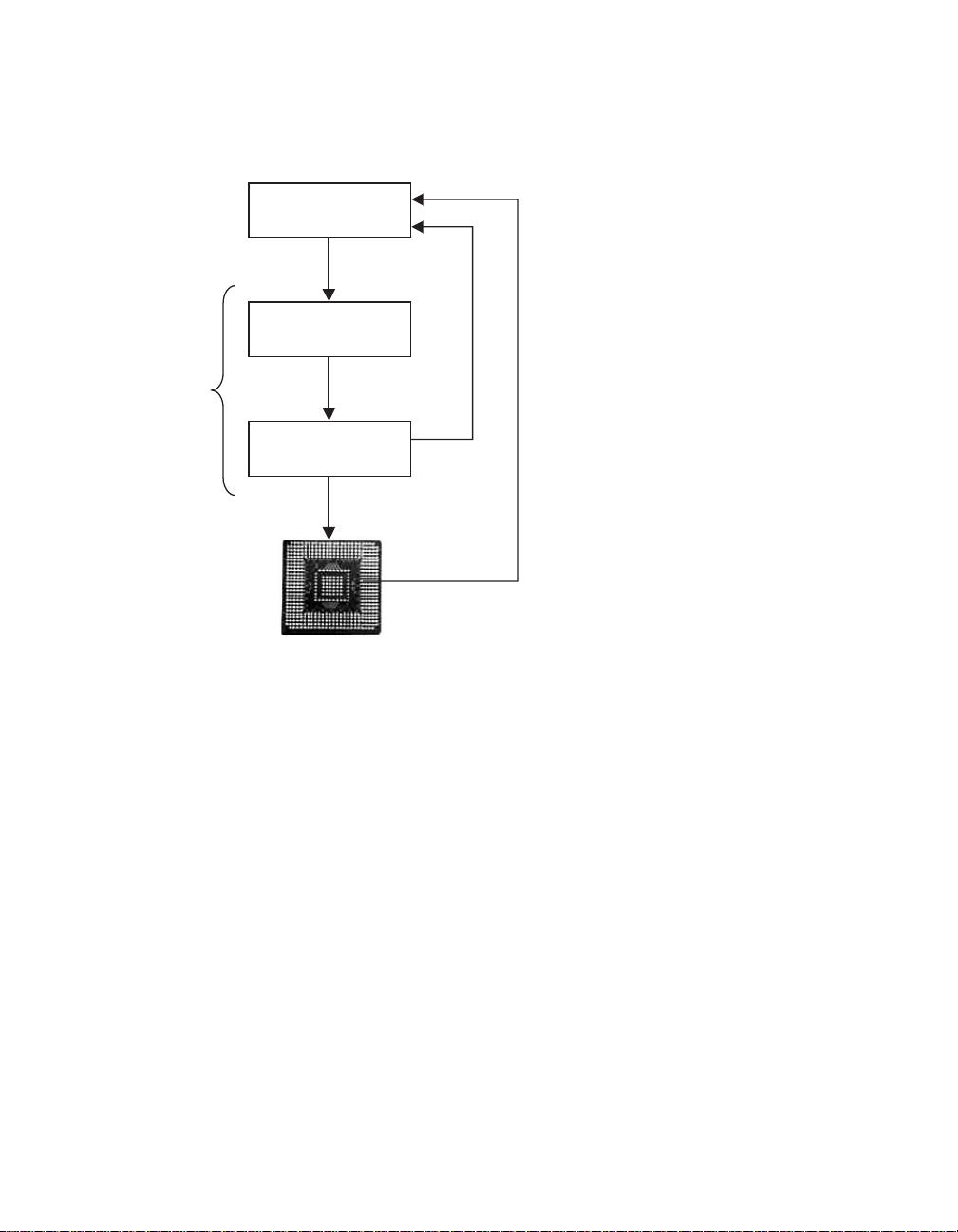

- VHDL 的两种主要使用模式:行为描述和结构描述,以及它们在电路设计中的应用。

- VHDL 的基本语法元素,如实体、架构、包、类型和运算符。

- 如何使用 VHDL 描述逻辑门、触发器、寄存器、计数器等基本逻辑组件。

随着章节的深入,读者可以期待学习到更多关于 VHDL 设计流程的知识,包括如何创建设计实体、定义接口、编写结构描述以及如何进行行为建模。此外,书中还可能涵盖了以下主题:

- 数据流分析和行为建模,包括进程(processes)、并行性和同步机制。

- 结构化设计方法,如模块化设计和层次化设计,以及如何利用库和子程序来提高代码复用性。

- 错误处理和调试技巧,以及如何使用测试平台(testbench)进行设计验证。

- 综合(synthesis)的概念,将 VHDL 代码转换为实际硬件的过程,以及如何优化设计以满足性能和资源限制。

- 实例化(instantiation)和库管理,了解如何在不同项目中重用设计模块。

书中还可能包含对 VHDL 标准更新(如 VHDL-2008)的讨论,以及与其他硬件描述语言(如 Verilog)的比较。此外,参考文献和索引将提供更深入学习和研究的资源。

总而言之,《CircuitDesignwithVHDL》是为那些希望掌握使用 VHDL 进行电路设计的工程师和学生准备的一本全面指南,它不仅解释了语言的基础知识,而且探讨了实际设计过程中的挑战和最佳实践。通过阅读本书,读者将能够运用 VHDL 开展复杂的电子系统设计任务。

2012-03-20 上传

2024-12-24 上传

2024-12-24 上传

2024-12-24 上传

2024-12-24 上传