20

TLV320AIC34

SLAS538B –OCTOBER 2007–REVISED NOVEMBER 2016

www.ti.com

Product Folder Links: TLV320AIC34

Submit Documentation Feedback Copyright © 2007–2016, Texas Instruments Incorporated

Feature Description (continued)

The word clock (WCLK_x or GPIO1_x) is used to define the beginning of a frame, and may be programmed as

either a pulse or a square-wave signal. The frequency of this clock corresponds to the maximum of the selected

ADC and DAC sampling frequencies.

The bit clock (BCLK_x or GPIO2_x) is used to clock in and out the digital audio data across the serial bus. When

in master mode, this signal can be programmed in two further modes, continuous transfer mode and 256-clock

mode. In continuous transfer mode, only the minimal number of bit clocks are required to transfer the audio data

are generated, so in general, the number of bit clocks per frame is two times the data width. For example, if data

width is chosen as 16 bits, then 32 bit clocks are generated per frame. If the bit clock signal in master mode is

used by a PLL in another device, TI recommends that the 16-bit or 32-bit data-width selections be used. These

cases result in a low-jitter bit clock signal being generated, having frequencies of 32 × f

S

or 64 × f

S

. In the cases

of 20-bit and 24-bt data width in master mode, the bit clocks generated in each frame are not all of equal period,

due to the device not having a clean 40 × f

S

or 48 × f

S

clock signal readily available. The average frequency of

the bit clock signal is still accurate in these cases (being 40 × f

S

or 48 × f

S

), but the resulting clock signal has

higher jitter than in the 16-bit and 32-bit cases.

In 256-clock mode, a constant 256 bit clocks per frame are generated, independent of the data width chosen.

The TLV320AIC34 further includes programmability to put the DOUT_x line in the high-impedance state during

all bit clocks when valid data is not being sent. By combining this capability with the ability to program at what bit

clock in a frame the audio data begins, time-division multiplexing (TDM) can be accomplished, resulting in

multiple codecs able to use a single audio serial data bus.

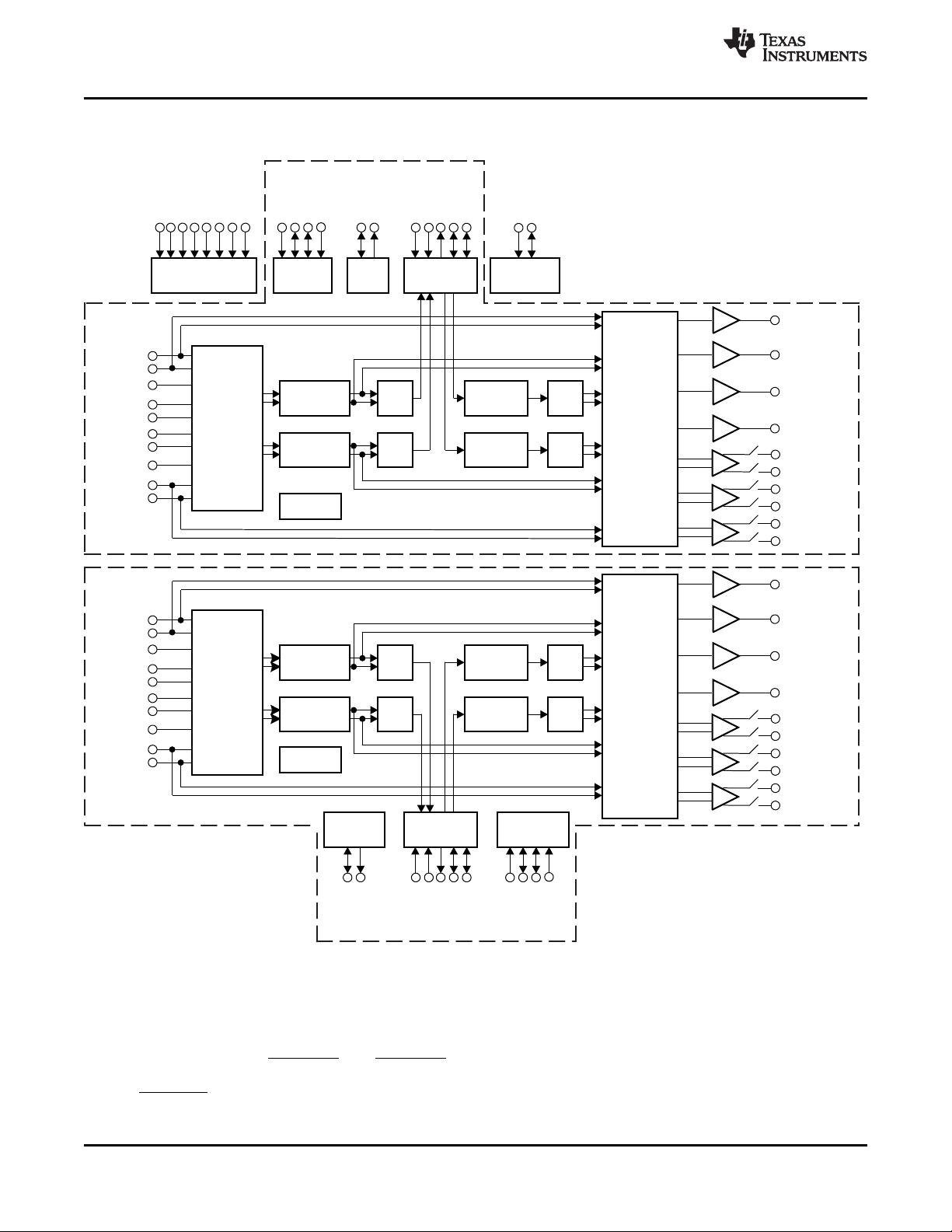

The TLV320AIC34 also provides additional capability for ADCs and DACs within each partition (A or B) to run at

different data rates, which is described in more detail later in this datasheet. In this mode, both ADC and DAC

data are clocked using the same bit clock (BCLK_x) signal, but two word clock (WCLK_x) signals are used, one

for the ADC data and one for the DAC data. When configured for this mode of operation, the WCLK_x terminal is

used for the DAC word clock, while GPIO1_x can be used for the ADC word clock.

When the audio serial data busses are powered down while configured in master mode, the terminals associated

with the interfaces are put into a high-impedance state.

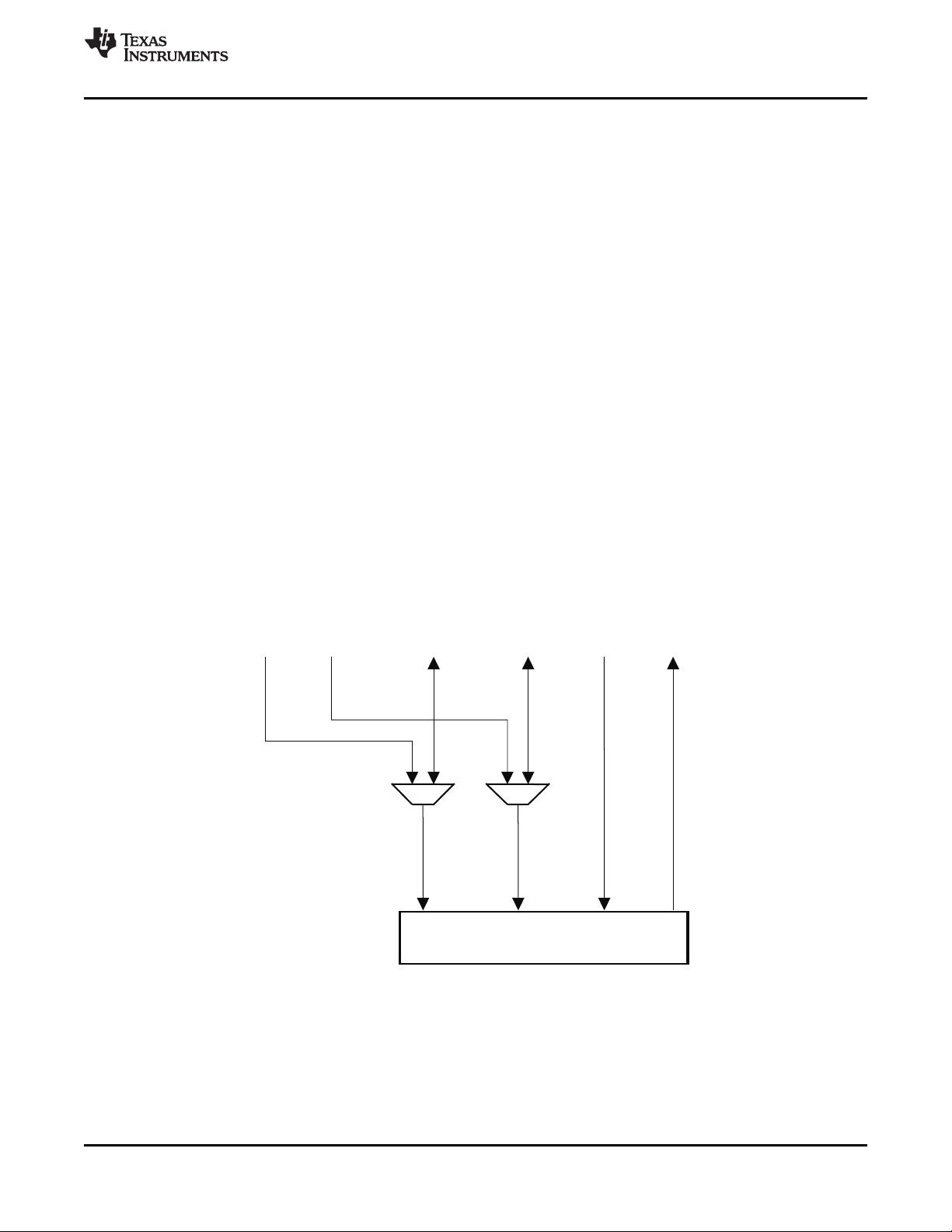

9.3.4 TDM Data Transfer

Time-division multiplexed data transfer can be realized in any of the previously mentioned transfer modes if the

256-clock bit clock mode is selected, although TI recommends using either left-justified mode or DSP mode. By

changing the programmable offset, the bit clock in each frame where the data begins can be changed, and the

serial data output driver (DOUT_x) can also be programmed into the high-impedance state during all bit clocks

except when valid data is being put onto the bus. This allows other codecs to be programmed with different

offsets and to drive their data onto the same DOUT_x line, just in a different slot. For incoming data, the codec

simply ignores data on the bus except where it is expected based on the programmed offset. See Using TDM

Function to Interface Four AIC33 CODECs with a Single Host Processor (SLAA301) and Using TLV320AIC3x

Digital Audio Data Serial Interface With Time-Division Multiplexing Support (SLAA311).

Note that the location of the data when an offset is programmed is different, depending on what transfer mode is

selected. In DSP mode, both left and right channels of data are transferred immediately adjacent to each other in

the frame. This differs from left-justified mode, where the left- and right-channel data are always a half-frame

apart in each frame. In this case, as the offset is programmed from zero to some higher value, both the left- and

right-channel data move across the frame, but still stay a full half-frame apart from each other. This is depicted in

Figure 14 for the two cases.