VHDL设计:实现可定时99分钟的定时器

版权申诉

149 浏览量

更新于2024-07-07

收藏 649KB DOC 举报

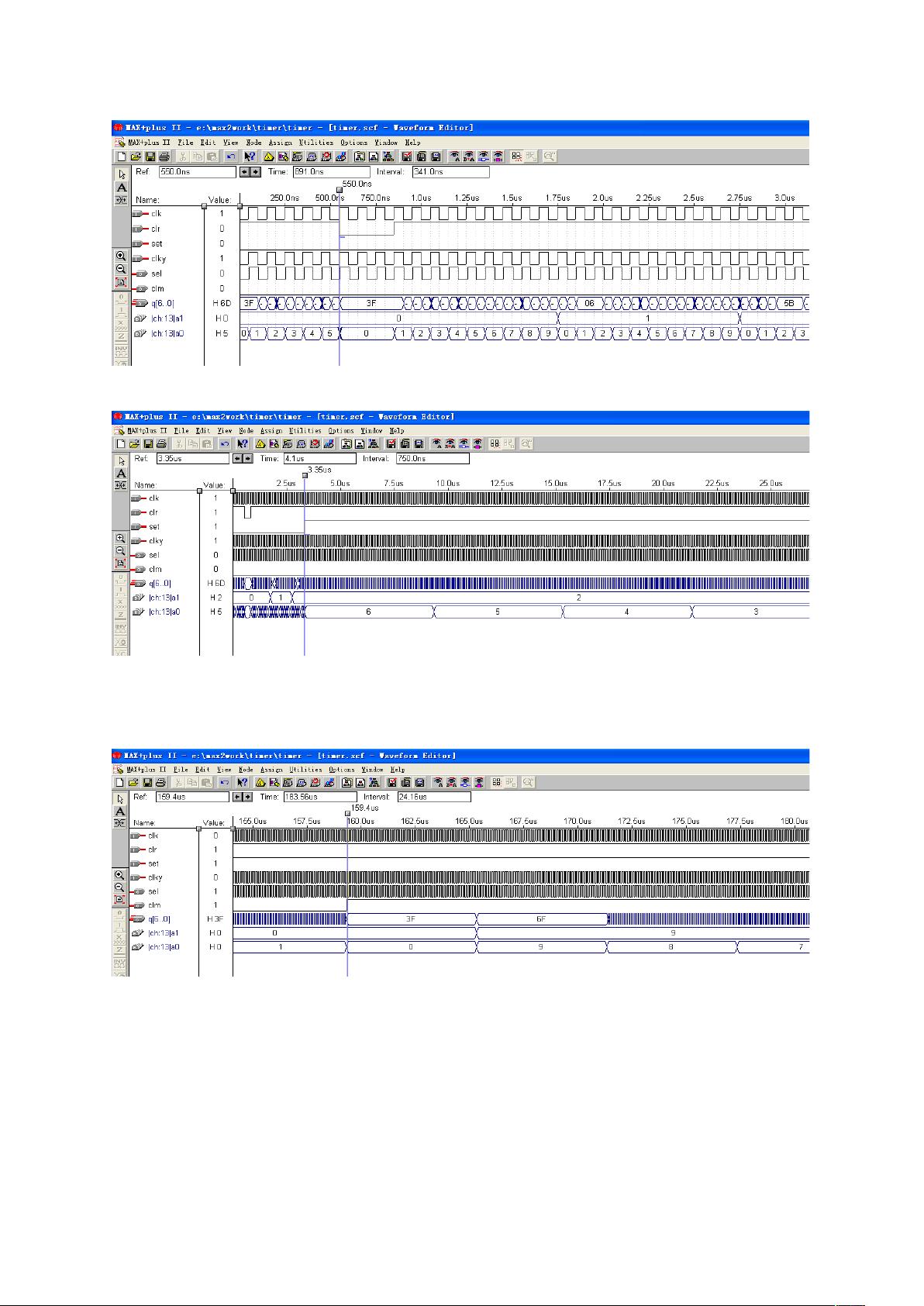

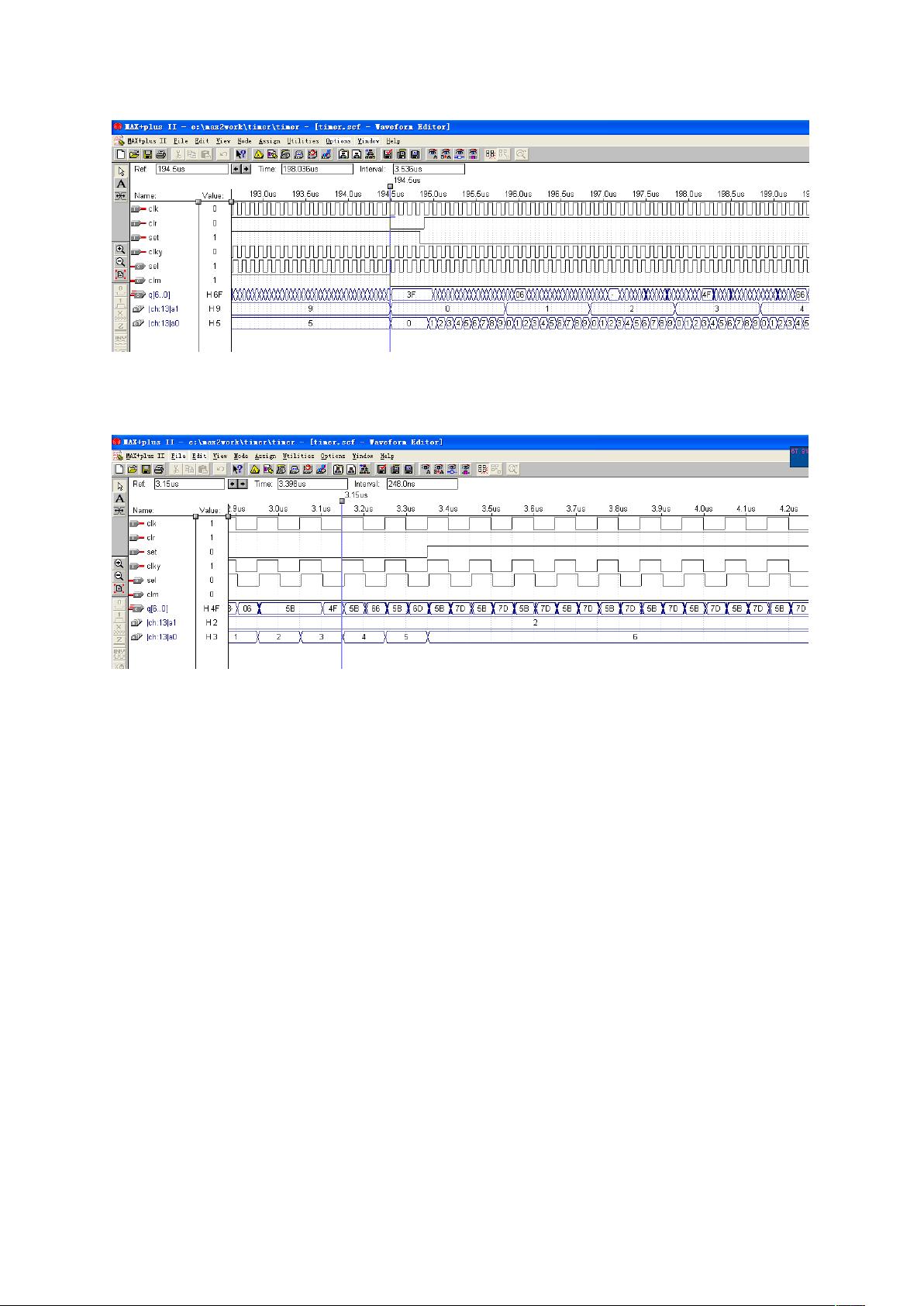

"定时器VHDL设计文档详细介绍了如何使用VHDL语言设计一个功能完备的定时器。设计包括整体清零、最高定时至99分钟、秒速递增和分速递减等功能,并通过数码管显示时间变化,以及 alm 输出高电平以触发其他电路或报警。"

在VHDL设计中,定时器是一个关键的数字系统组件,用于执行特定时间间隔的任务。本设计文档主要涵盖了一个基于VHDL的定时器实现,其核心模块名为AAA。该模块具备以下功能:

1. **整体清零**:通过clr输入信号,当clr为低电平时,定时器的所有计数值将被重置为零,alm输出也会被清零,表示定时器停止工作。

2. **计时范围**:定时器能够设定最高到99分钟的定时时间。这通过内部计数器的秒速递增和分速递减实现。

3. **计时操作**:clk信号提供1Hz的秒脉冲(在仿真中使用10MHz)。set输入信号用来设置定时,当set为低电平时,定时器开始从零以秒为单位递增。一旦达到预设时间,set变为高电平,定时器则开始以分钟为单位递减,直到计时完毕。

4. **分频器**:内部实现了60分频,即每过60秒,分钟计数器会增加或减少一。

5. **输出显示**:使用两个四位的std_logic_vector(t1和t0)分别表示分钟和秒,输出到数码管,以便于观察时间变化。

6. **报警信号**:alm输出信号在定时结束后变为高电平,可用于启动其他电路或触发报警。

7. **模块结构**:AAA模块的结构包含一个进程(PROCESS)对clk和clr信号进行敏感,变量t1和t0用于存储当前的分钟和秒值,变量t用于辅助计算。在clk上升沿,根据set的状态更新计数值。

8. **代码实现**:使用IEEE库中的std_logic_1164和std_logic_unsigned包,定义了实体和架构。实体定义了输入输出接口,架构中定义了处理过程,实现计数逻辑。

9. **计数逻辑**:在进程中,当set为低电平时,秒计数器递增,当达到9后自动回零并递增分钟计数器。当set为高电平时,分钟计数器递减,当分钟和秒均为零时,alm输出高电平。

通过这样的设计,定时器能够精确控制时间间隔,并通过外部信号进行控制和状态指示,满足了实验要求的定时功能。在实际应用中,这样的定时器可能需要进一步优化,例如添加额外的输入来控制预设时间,或者使用更复杂的数据结构来支持更广泛的定时范围。

105 浏览量

2021-09-29 上传

2021-09-25 上传

215 浏览量

216 浏览量

209 浏览量

2021-09-18 上传

2022-03-14 上传