TimeQuest静态时序分析模型入门笔记

"这篇笔记主要介绍了TimeQuest,它是Altera Quartus II软件中的一个时序分析工具,用于评估和优化FPGA设计的时序性能。笔记作者强调TimeQuest中的时序概念与Verilog HDL中的时序不同,后者关注的是模块间的通信和行为,而前者关注的是实际电路路径的延迟问题。笔记内容主要围绕静态时序分析模型展开,讨论了模型的基本单位——节点,通常以寄存器的形式存在,并通过理想时序图来阐述其工作原理。"

在深入讨论TimeQuest的静态时序分析模型之前,我们需要了解静态时序分析的基本概念。静态时序分析是一种不依赖于仿真运行的设计分析方法,它能够快速、准确地预测电路在最坏情况下的时序性能。这种方法在现代数字系统设计中至关重要,因为它允许设计师在设计早期发现潜在的时序问题,如建立时间和保持时间的违反。

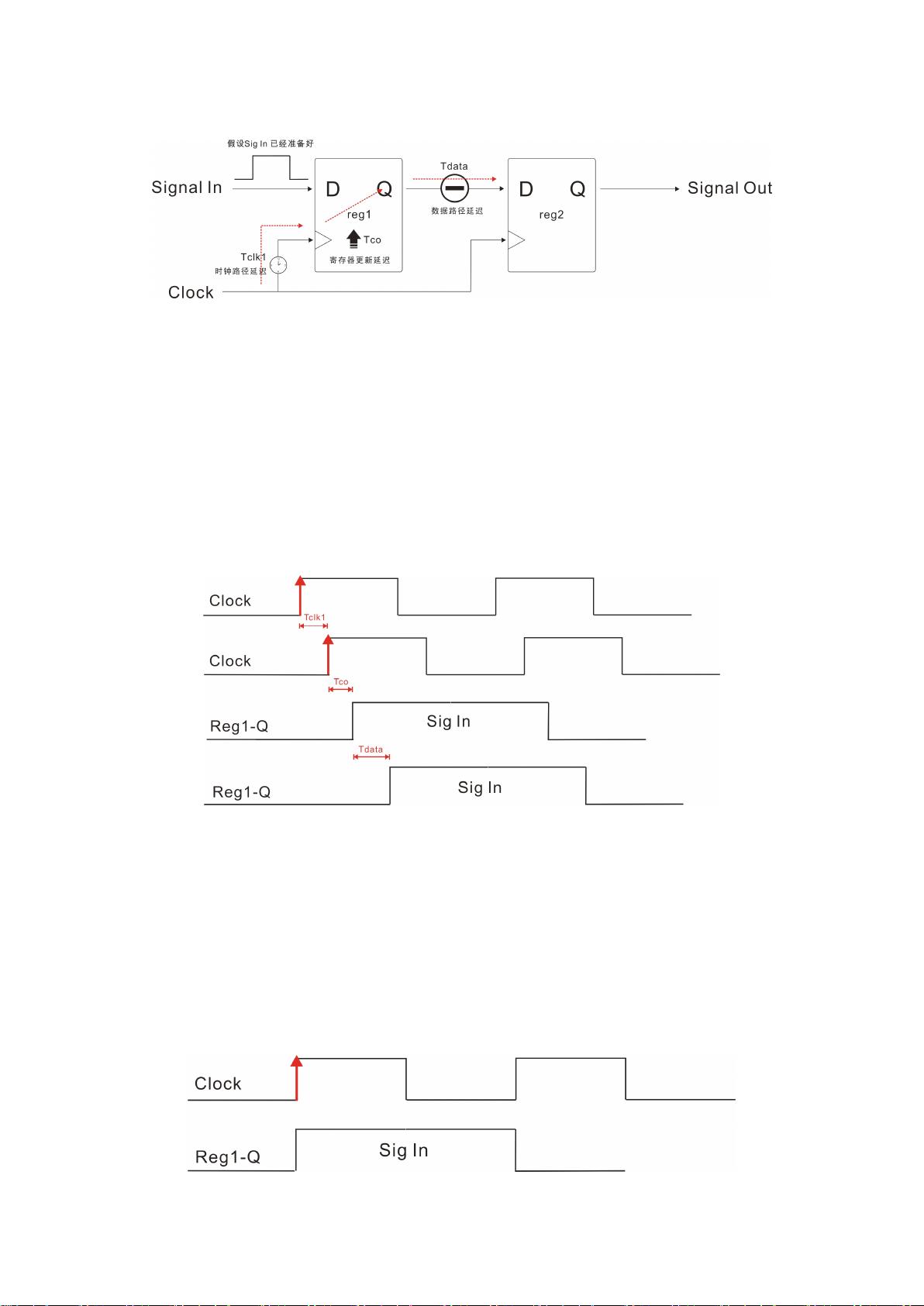

TimeQuest的分析模型以节点为基础,这些节点通常被看作是寄存器。在理想情况下,信号通过寄存器传递时,不存在任何物理延迟,就像图1.1c所示的理想时序图。然而,在实际情况中,由于电路延迟,信号从输入到输出会有延迟,这就引入了建立时间和保持时间的概念。建立时间是指数据必须在时钟边沿之前多长时间到达寄存器的输入,以确保在下一个时钟周期正确捕获;保持时间则是指数据必须在时钟边沿之后保持稳定的时间。

TimeQuest通过分析设计中的所有路径,找出最长的时序路径(也称为关键路径),并计算出满足时序要求所需的最小时钟周期。如果关键路径的延迟超过了这个最小时钟周期,那么设计就会有时序违例,需要进行优化。

在TimeQuest中,设计师可以使用各种技术来优化时序,如改变逻辑实现方式、调整时钟树结构或分配更优的物理资源。此外,TimeQuest还提供了报告和可视化工具,帮助设计师理解设计的时序特性,定位问题,并指导优化策略。

总结来说,TimeQuest是FPGA设计流程中不可或缺的一部分,它通过静态时序分析模型帮助设计师确保设计满足严格的时序约束,从而保证系统的可靠性。这篇笔记通过简单易懂的例子和理想时序图,为初学者提供了一个初步了解TimeQuest和静态时序分析的入口。

2021-10-02 上传

点击了解资源详情

2021-09-30 上传

2021-02-11 上传

2024-10-06 上传

2021-05-02 上传

2020-12-21 上传

2021-04-29 上传

肖北南

- 粉丝: 1

- 资源: 22

最新资源

- From Data Mining to Knowledge Discovery in Database

- developement projects for microsoft office sharepoint server 2007 and windows sharepoint services version 3.0

- C# 语言 规范1.2

- 银行家算法课程设计 源码(记事本)

- c++笔试面试宝典2009版

- 系统架构设计师考试大纲2009

- 数据库课程设计选题.

- spring-framework-reference.pdf

- 元器件封装大全,doc

- JSP技术手册JSP技术手册,详细全面介绍了JSP的基础和高端技术

- AT89C2051管脚图引脚图中文资料

- 全国医学博士入学考生统考英语试题2001

- 2008年下半年全国软件设计师上午试题,好资源

- 电力系统稳态分析试题

- WebWork In Action

- 有效无痛苦的代码评审