基于Vivado的DDR3 IP核FDMA扩展及应用指南

需积分: 44 127 浏览量

更新于2024-08-05

1

收藏 568KB PDF 举报

本篇文章详细介绍了如何在Xilinx Vivado平台上使用FDMA IP核扩展功能,特别是针对DDR3接口的应用。FDMA(Fast Data Memory Access)是一个由MSXBO定制的基于AXI4总线协议的DMA控制器,旨在简化FPGA对PL(Place and Logic)内的DDR或ZYNQ PS(Processor System)上的DDR内存的直接读写操作。

文章首先概述了FDMA IP的核心作用,强调它能够通过AXI4全主模式实现对DDR的高效访问,这对于需要频繁读写内存的系统设计来说非常实用。作者还推荐了一篇参考文档《02_ArtixFPGADDR控制器MIG使用(AXI4)(MA703FA-35T)20190401》,供读者进一步深入学习。

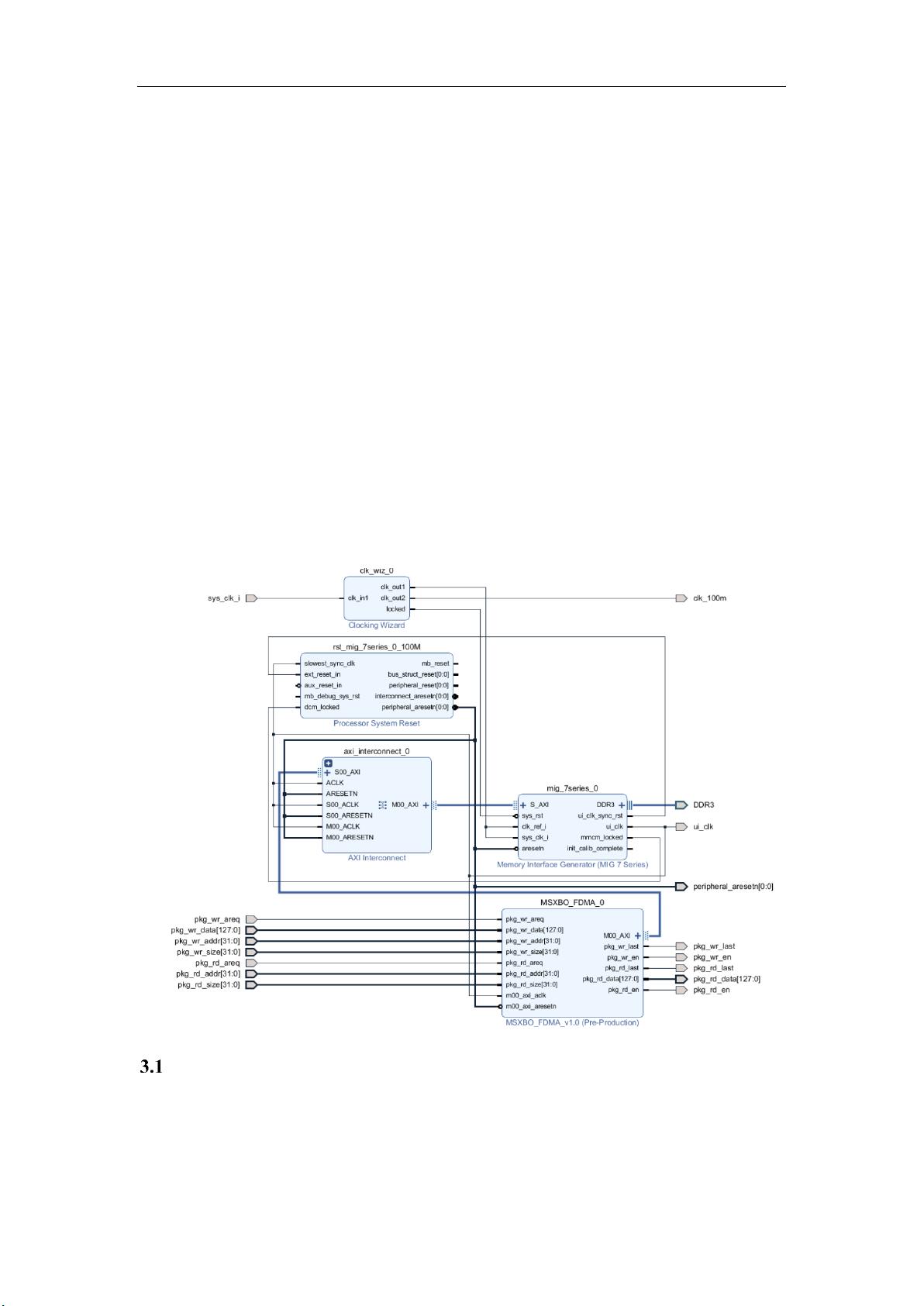

接下来,文章重点讲解了在Block Design (BD)环境中搭建FDMA与DDR3 IP的流程。BD方法被用于创建工程项目,当配置好DDR3 IP和FDMA IP后,通过运行"runconnectionautomation"工具,系统会自动生成相关连接的IP,如rst_mig_*, axi_interconnect_*, 并自动连接各个组件。

DDR3 IP的设置部分是关键环节,文章提到设置包括选择正确的DDR型号、配置内核时钟和位宽。根据提供的例子,如果DDR的内核时钟为400MHz,位宽为16bits,那么数据传输速率将达到1600MB/s。同时,用户侧使用的时钟频率ui_clk通过PHYtoControllerClockRatio设置,如设置为400MHz/4,得到100MHz。在DDR的AXI数据参数设置中,需要确保datawidth设置为最大值,以充分利用DDR的带宽。

最后,文章提及了DDR输入时钟的设置,其中inputclockperild作为参考时钟,相当于DDR设备的系统时钟。除了这些页面,还有其他常规设置,但文章没有详细列出。

这篇教程深入浅出地介绍了如何在Xilinx Vivado中通过FDMA IP扩展进行DDR3内存访问,涵盖了IP配置、接口设置以及工程搭建的详细步骤,对于FPGA开发人员理解和应用该技术具有很高的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-13 上传

2021-05-10 上传

2023-09-16 上传

2021-04-29 上传

120 浏览量

蒲公英的归宿

- 粉丝: 11

- 资源: 1

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用