时序逻辑电路解析:同步与异步电路的区别

需积分: 20 69 浏览量

更新于2024-08-02

收藏 4.38MB PDF 举报

"时序逻辑电路是数字逻辑电路的一种,其输出不仅取决于当前输入,还与过去的输入序列有关。这种电路由存储电路和组合逻辑电路组成,其状态由状态变量集合定义,包含了过去所有影响电路行为的信息。时序电路分为同步和异步两类。同步时序电路的状态改变受同一时钟脉冲控制,而异步时序电路则没有统一的时钟控制,输入可以直接引发状态变化。"

时序逻辑电路是数字电子技术中的核心概念,它们在计算机、通信设备、数据处理系统等众多领域有着广泛应用。与组合逻辑电路不同,组合逻辑电路的输出仅取决于当前的输入,而时序逻辑电路的输出则是历史输入序列的函数,这使得时序逻辑电路能够实现记忆和计数等功能。

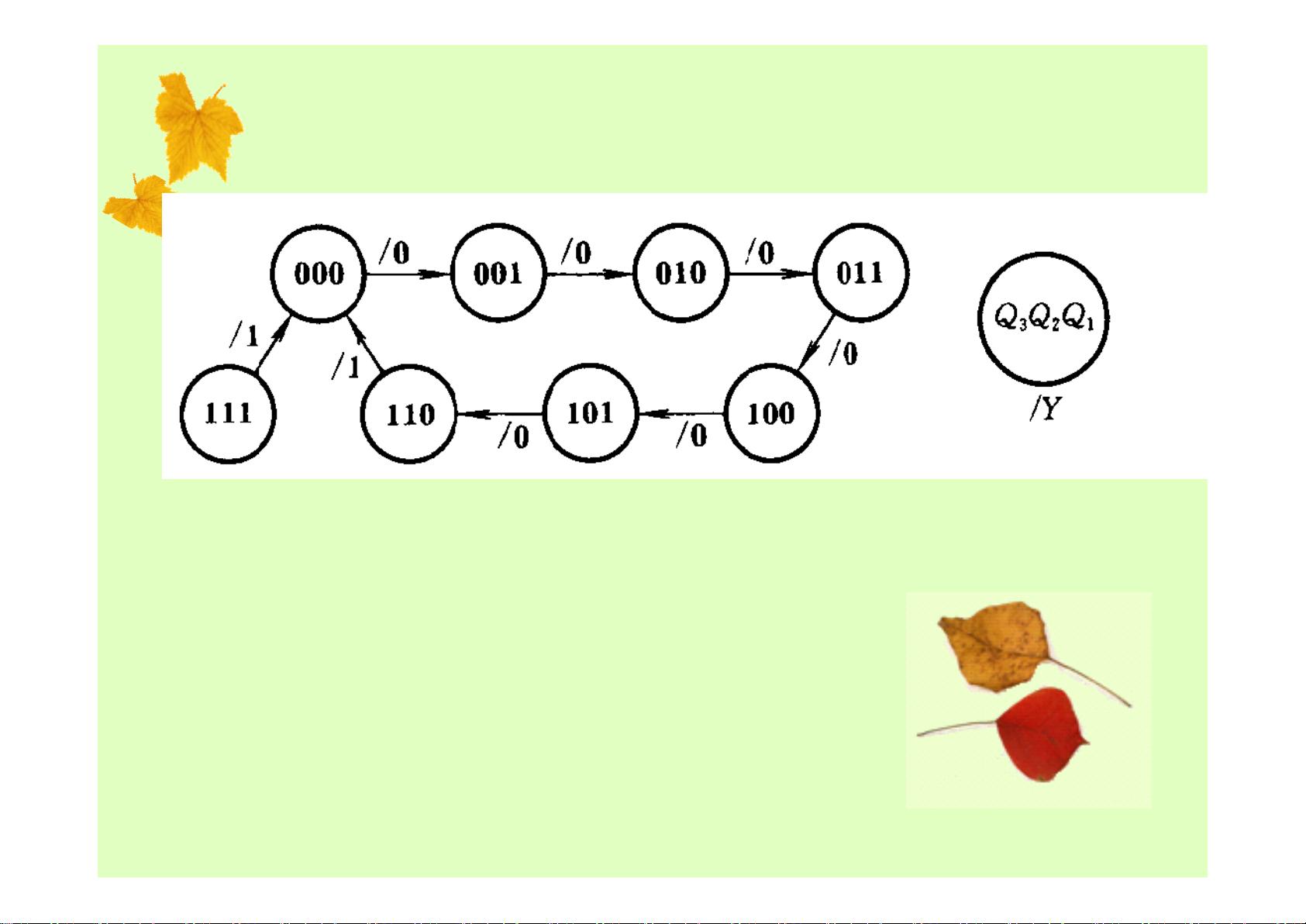

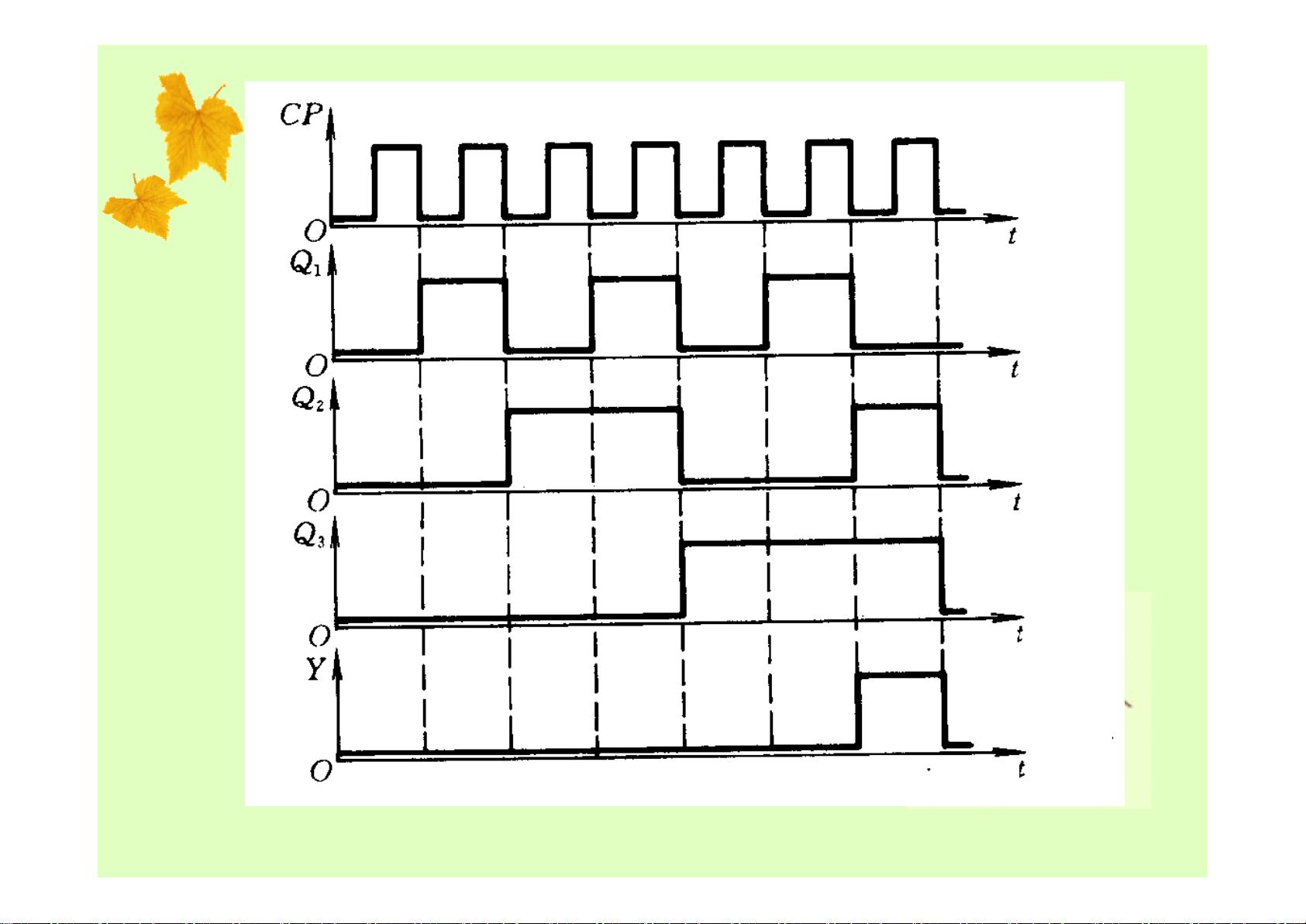

时序逻辑电路由两部分构成:存储电路和组合逻辑电路。存储电路,如触发器或寄存器,用于保存状态信息,这些信息是决定电路未来行为的关键。组合逻辑电路则负责根据当前输入和存储电路的状态来计算输出。时序电路的状态通常用有限状态机(FSM)的概念来描述,其中状态变量集合表示电路可能处于的多种状态,且每个状态都对应着一组特定的输入-输出关系。

同步时序逻辑电路是所有状态变化都在同一时钟脉冲的上升沿或下降沿发生的电路。这种类型的电路有明确的时钟同步,确保了所有部件在同一时刻更新状态,减少了竞争和不定性的问题。例如,常见的同步电路包括计数器和移位寄存器。

异步时序逻辑电路则不依赖全局时钟,其状态变化可以由输入信号直接触发,这可能导致电路的不同部分在不同的时间点更新状态。虽然异步设计提供了更大的灵活性,但同时也增加了设计的复杂性和潜在的错误源。

区分组合逻辑电路和时序逻辑电路的关键在于是否具有记忆功能。组合逻辑电路没有记忆,它们的输出只基于即时的输入;而时序逻辑电路具有记忆,能够记住过去的输入状态,并据此影响当前的输出。这一特性使得时序逻辑电路在实现复杂的控制逻辑、数据处理和序列分析任务时显得尤为关键。

时序逻辑电路在数字系统中扮演着至关重要的角色,它们是构建复杂数字系统的基础,如微处理器、存储器和各种接口控制器。理解并熟练掌握时序逻辑电路的设计和工作原理对于电子工程和计算机科学的学习者至关重要。

2021-11-09 上传

2021-10-08 上传

104 浏览量

207 浏览量

141 浏览量

166 浏览量

127 浏览量

2021-10-08 上传

professor12345

- 粉丝: 0

- 资源: 7

最新资源

- 先进算法讲义-中科大.pdf 需要的下吧

- TD-SCDMA Principle -李世鹤

- rhce5 启动引导troubleshooting实验笔记

- 软件体系结构(ppt版)

- C和C++嵌入式系统编程

- Java企业版中性能调节的最佳实践.pdf

- Log4j中文手册2006_04_07_205056_ZCxoePRlHJ_2.pdf

- AutoCADAutoCAD 2005中文版是美国AutoDesk公司推出的AutoCAD软件的最新版本,它在以前版本的强大功能之上又增加了新的功能。通过本章的学习,读者将对AutoCAD 2005中文版有一个整体上的了解,学会安装和启动的方法,初步了解AutoCAD 2005中文版的界面组成。

- 全国等级考试 二级vf机试题

- The Definitive Guide to Grails Second Edition

- LINUX电子书

- IGBT 应用系统资料!

- 单片机恒温箱温度控制系统的设计

- ARM的嵌入式系统硬件结构设计经典

- MATLAB偏微分方程工具箱简介

- TestLink1.7RC3使用说明书.doc