复旦数字电路设计:Chapter7 顺序逻辑电路解析

需积分: 5 68 浏览量

更新于2024-07-09

收藏 354KB PDF 举报

"该资源是复旦大学数字电路设计课程的一部分,主要关注Chapter7,即序列逻辑电路的设计。内容来自《Digital Integrated Circuits》第二版,由Jan M. Rabaey、Anantha Chandrakasan和Borivoje Nikolic合著。教程涵盖了序列电路的基础知识,包括存储机制、正反馈、基于电荷的电路以及组合逻辑。同时,讨论了寄存器(Latch)和触发器(Register)的区别,并介绍了命名规范,如在文本中,latch被定义为电平敏感的,而register则被认为是边沿触发的。"

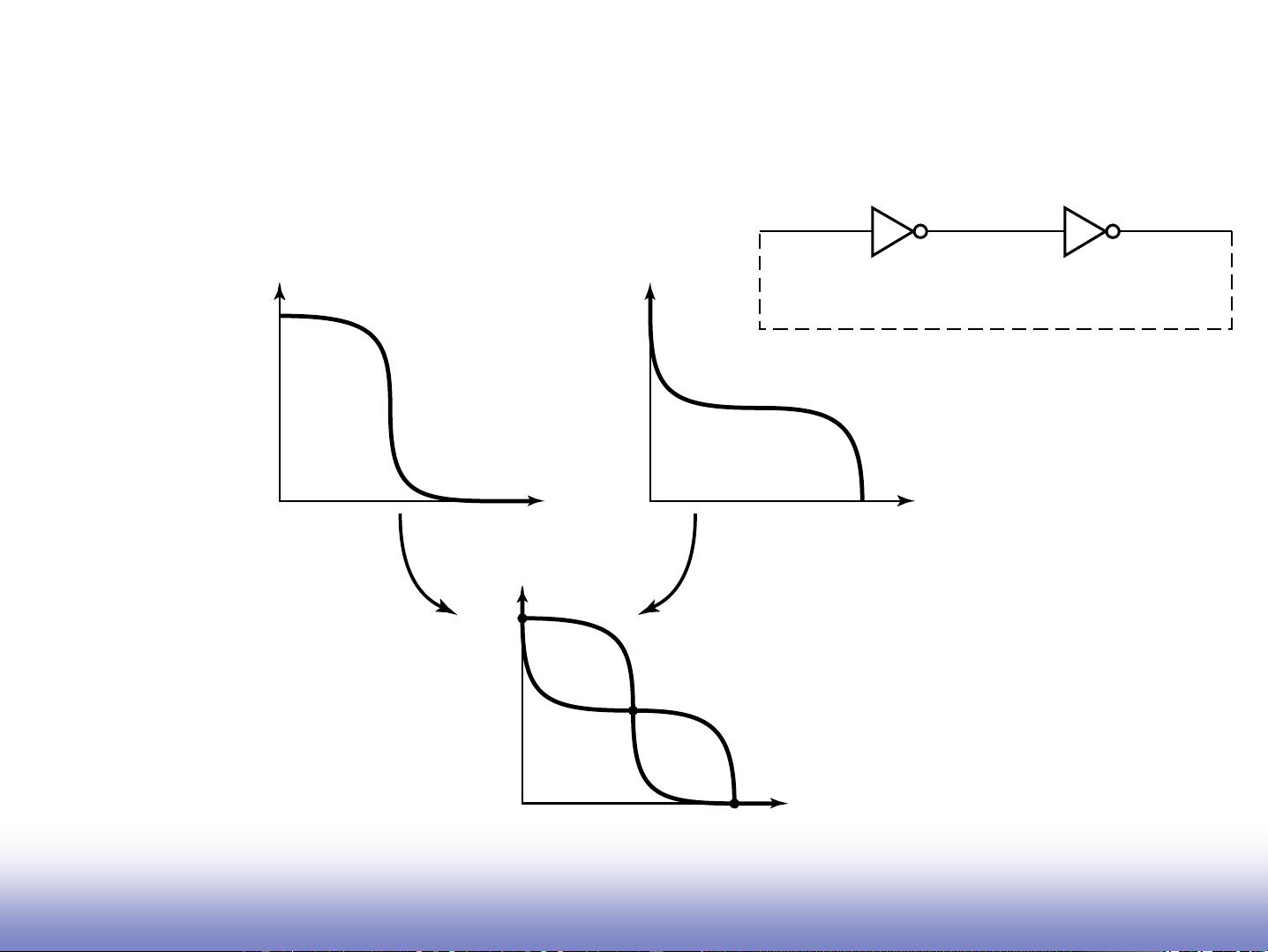

在数字电路设计中,序列逻辑电路是一种重要的概念,它们能够在时钟信号的控制下存储和处理数据。本章深入探讨了这一主题,首先介绍了两种基本的存储机制:正反馈和基于电荷的机制。正反馈用于实现电路的自保持状态,而基于电荷的机制通常涉及电容的充放电,用于数据的存储。

组合逻辑电路是序列电路的基础,它们根据输入信号即时产生输出,不具有记忆功能。然而,序列电路结合了这种即时响应与存储能力,使得数据可以在时钟周期内保持稳定。在本教程中,作者对比了latch(锁存器)和register(寄存器)这两种常见的序列逻辑元件。

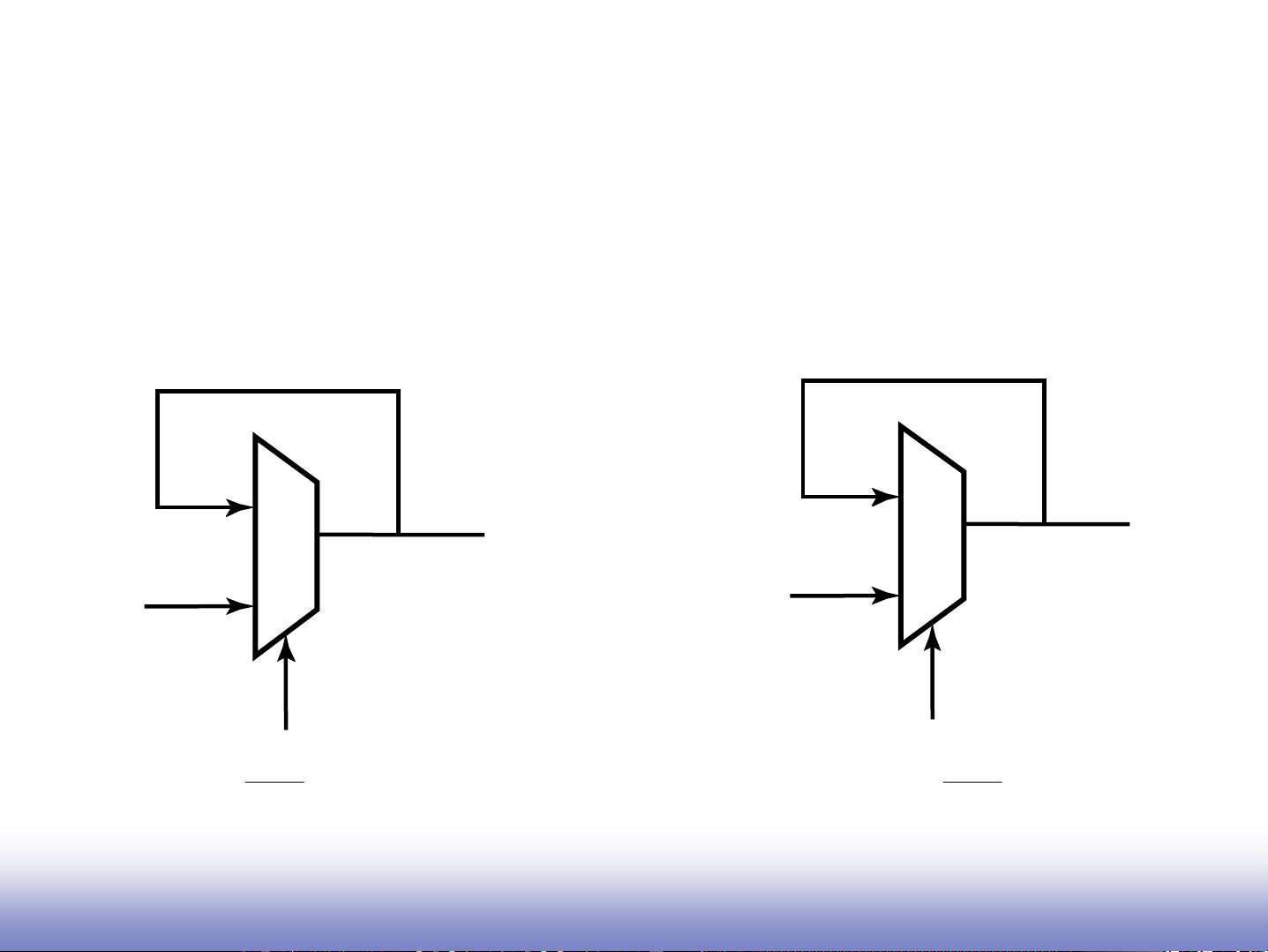

锁存器在时钟信号低电平时存储数据,当时钟信号改变时,数据仍然保持不变。其结构通常包含D输入和Q输出,以及一个时钟(Clk)信号。而寄存器则在时钟信号上升沿(或下降沿,取决于设计)时捕获数据,一旦时钟信号改变,存储的数据将保持直到下一个时钟边缘。同样,寄存器也有D输入和Q输出,但其行为取决于时钟的边沿。

在不同的文献和教材中,序列逻辑元件的命名可能有所不同,例如,边沿触发的器件有时被称为flip-flop。这样的命名差异可能会导致理解上的混淆,因此,了解和掌握标准的命名约定对于学习和设计数字电路至关重要。

本章还可能涵盖了其他重要概念,如触发器的不同类型(如SR锁存器、D触发器、JK触发器和T触发器),以及这些组件如何在实际应用中,如计数器和移位寄存器中发挥作用。此外,可能还涉及到同步和异步序列电路、时钟同步与偏移问题,以及电路的建立时间和保持时间等关键性能指标。

复旦大学的这个章节提供了全面的序列逻辑电路设计基础,对于理解和设计复杂的数字系统具有很大的帮助。无论是对电子工程的学生还是专业的电路设计师,都能从中受益。通过深入学习这些概念,读者可以进一步掌握数字集成电路的核心原理。

2021-05-20 上传

2021-05-20 上传

2021-05-20 上传

2021-05-20 上传

2021-05-20 上传

2021-05-20 上传

weixin_38692162

- 粉丝: 4

- 资源: 904

最新资源

- JDK 17 Linux版本压缩包解压与安装指南

- C++/Qt飞行模拟器教员控制台系统源码发布

- TensorFlow深度学习实践:CNN在MNIST数据集上的应用

- 鸿蒙驱动HCIA资料整理-培训教材与开发者指南

- 凯撒Java版SaaS OA协同办公软件v2.0特性解析

- AutoCAD二次开发中文指南下载 - C#编程深入解析

- C语言冒泡排序算法实现详解

- Pointofix截屏:轻松实现高效截图体验

- Matlab实现SVM数据分类与预测教程

- 基于JSP+SQL的网站流量统计管理系统设计与实现

- C语言实现删除字符中重复项的方法与技巧

- e-sqlcipher.dll动态链接库的作用与应用

- 浙江工业大学自考网站开发与继续教育官网模板设计

- STM32 103C8T6 OLED 显示程序实现指南

- 高效压缩技术:删除重复字符压缩包

- JSP+SQL智能交通管理系统:违章处理与交通效率提升