数字电子技术:主从触发器与D型锁存器解析

版权申诉

152 浏览量

更新于2024-07-03

收藏 1.24MB PPT 举报

"该资源是关于数字电子技术的讲解,主要聚焦在锁存器和触发器,特别是D型、S-R型和J-K型的主从触发器以及维持阻塞触发器。内容涵盖了触发器的电路结构、工作原理以及动态特性,并通过具体的例子如74HC74集成电路中的D触发器进行了深入解析。"

在数字电子技术中,触发器是基本的存储单元,用于保持数据并在特定条件(如时钟脉冲)下更新。本资料主要关注5.4章节中的触发器,特别是主从触发器和维持阻塞触发器。

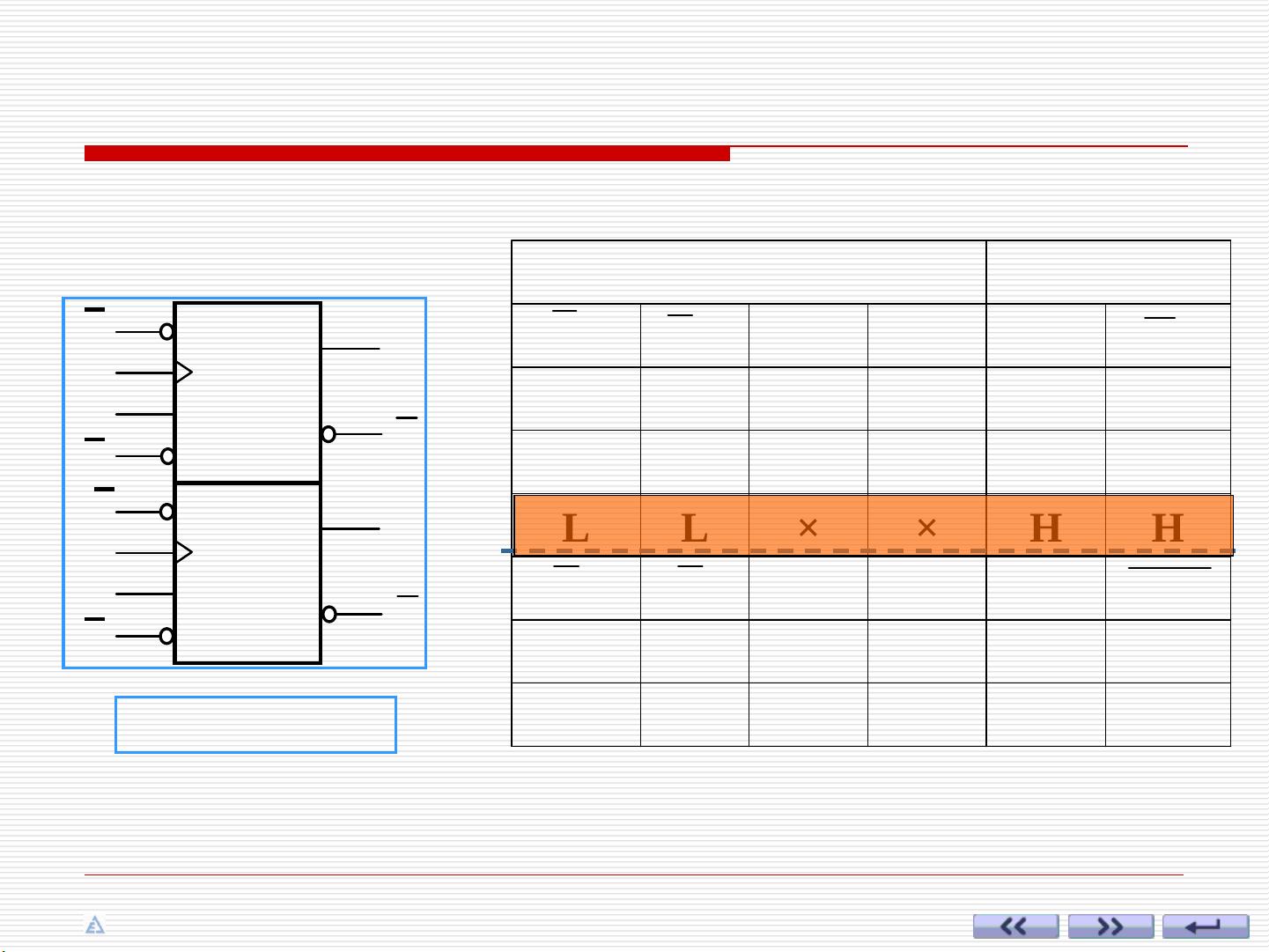

5.4.1 主从触发器包括D型、S-R型和J-K型。这些触发器的特点在于它们的输入信号在时钟脉冲(CP)的不同阶段被处理。D型触发器的输出Q在时钟脉冲的上升沿更新为输入D的值;S-R型触发器受S(设置)和R(复位)信号控制,当S=1且R=0时设置触发器状态为1,反之当S=0且R=1时复位为0;J-K型触发器则通过J和K输入进行翻转或保持操作。

5.4.2 维持阻塞触发器是一种D型触发器,它在时钟脉冲的上升沿期间阻止输入D的变化,确保数据稳定传输。这防止了由于输入信号的快速变化导致的错误状态。

5.4.3 利用传输延时的触发器,如J-K型和S-R型,利用电路的延迟特性来实现特定的逻辑功能,例如在时钟边沿后的某个延迟时间内改变触发器状态。

5.4.4 触发器的动态特性涉及到触发器在不同时钟周期间的稳定性和速度性能。这些特性对于高速数字系统的设计至关重要,因为它们影响数据的正确传输和系统的整体性能。

在Verilog HDL中,锁存器和触发器的描述方式不同,锁存器在使能信号E的高电平或低电平时对输入敏感,而触发器则在时钟脉冲的上升沿或下降沿对输入敏感。

电路结构方面,主从型触发器包含一个主锁存器和一个从锁存器。主锁存器在时钟脉冲低电平时接收输入,而从锁存器在时钟脉冲高电平时传递数据。例如,在D型主从触发器中,当CP=0时,输入D通过主锁存器,当CP由0跳变为1时,从锁存器的状态根据主锁存器之前捕获的D值更新。

74HC74集成电路中的D触发器是一个典型的CMOS边沿D触发器,其逻辑图和功能表展示了在不同输入和时钟条件下,如何根据D输入和CP时钟信号改变输出Q。

这份资料详细介绍了锁存器和触发器的工作原理,电路结构,以及它们在数字电子系统中的应用,对于理解和设计数字系统具有重要意义。

2024-05-30 上传

2023-06-28 上传

2023-05-27 上传

具体内容包括2.1基本放大电路 2.2运算放大器 2.3滤波电路 3.1组合逻辑电路的分析与设计 3.2编码器 3.3译码器 3.4数据选择器 3.5加法器 3.6触发器与锁存器 3.7计数器与寄存器

2023-07-20 上传

2024-08-24 上传

2023-05-20 上传

2023-04-22 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析