FPGA中的嵌入式双端口SRAM设计与应用

85 浏览量

更新于2024-09-01

收藏 263KB PDF 举报

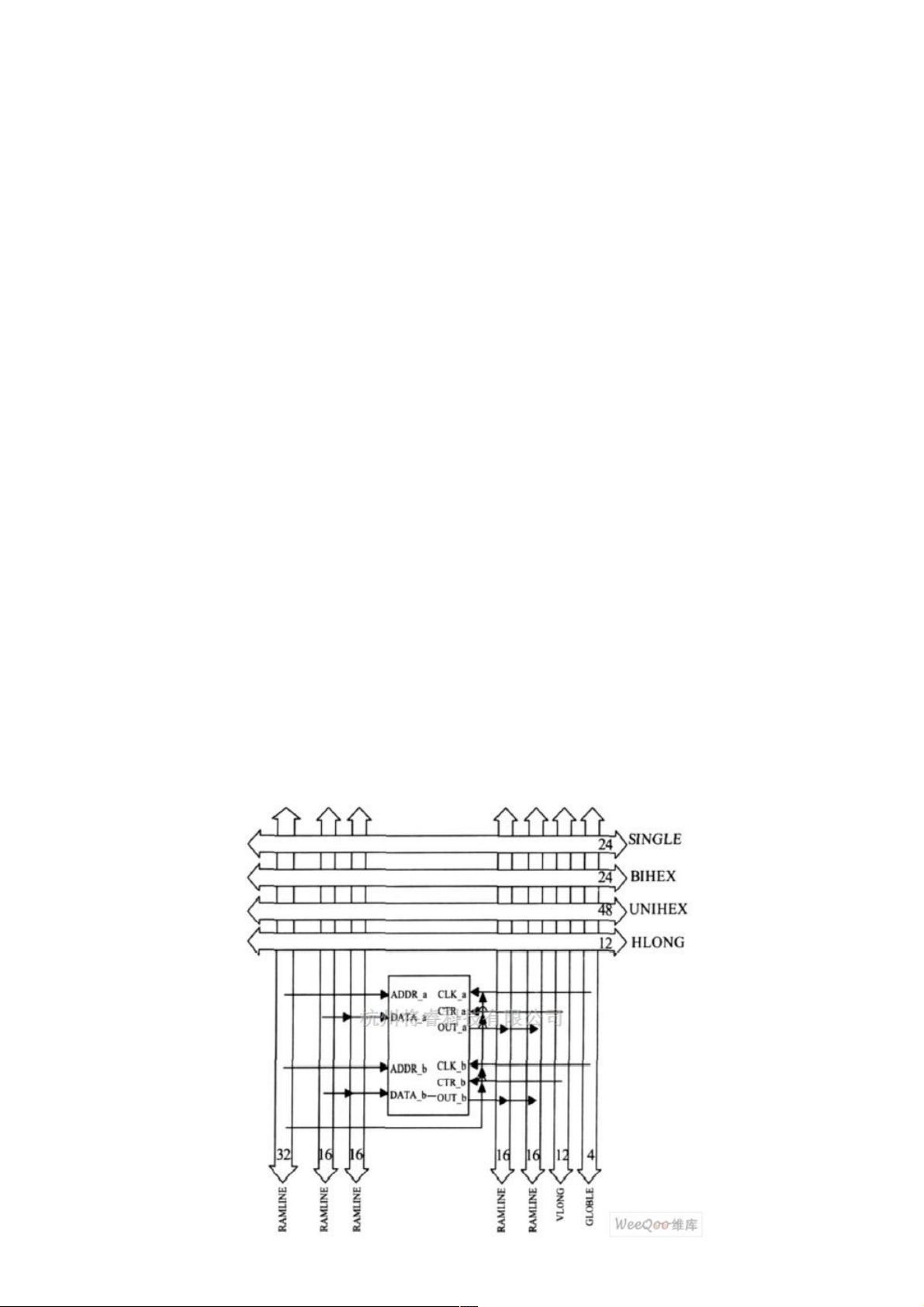

"EDA/PLD中的一种基于FPGA的嵌入式块SRAM的设计,着重于双端口可配置块存储器的实现,包括布线接口、可配置逻辑、译码和高速读写电路。设计适用于2.5V电源电压,采用0.22微米CMOS工艺,最高工作频率可达200MHz,可适应不同位数的存储需求。在FPGA中,这种SRAM可实现如FIFO等特定功能,常见应用包括片上缓冲、高速缓存和寄存器堆。设计采用了6管单元的SRAM结构,并通过BRAM块划分技术提高读取速度,通过减少负载电容来提升性能。"

在电子设计自动化(EDA)和可编程逻辑器件(PLD)领域,一种基于现场可编程门阵列(FPGA)的嵌入式块静态随机存取存储器(eSRAM)设计被提出。该设计关注的是一个可配置的双端口块存储器,它具备与其他电路的连接接口,允许灵活的逻辑配置,以及高效的读写操作电路。在编程过程中,设计允许对所有存储单元进行初始化清零,并在编程完成后转化为独立的双端口存储器结构。

嵌入式SRAM在逻辑芯片中广泛应用,特别是在需要高速数据存储和快速访问的场合,如片上缓冲器、高速缓存和寄存器堆。标准的6晶体管(6T)SRAM单元由于其工艺兼容性,通常被选为实现嵌入式存储器的基础。像Xilinx这样的公司,其FPGA产品会包含配置存储器、布线资源、I/O、可编程逻辑单元以及块存储器BRAM,其中BRAM不仅增加内存容量,还可以作为查找表(LUT)的扩展。

为了提高BRAM的性能,文章提出了块划分策略,即将存储阵列划分为多个较小的块,减少位线和字线上的负载电容,从而降低读取延迟。这种设计方法能够满足现代数字系统对高速存储的需求,特别是在需要高吞吐量和低延迟的场合。实际流片结果验证了设计的可行性,2.5V的工作电压下,使用0.22微米的CMOS单多晶五铝工艺制造,最高工作频率达到200MHz,能够实现不同位宽的存储功能,且具有良好的成本效益。

此外,这种块SRAM设计还能与FPGA中的其他逻辑块编程连接,实现如FIFO(先进先出队列)这样的功能。这展示了FPGA的灵活性,使得设计者能够根据应用需求定制存储解决方案,优化系统的整体性能。因此,这种基于FPGA的嵌入式块SRAM设计对于高性能、低延迟的嵌入式系统开发具有重要意义。

2020-11-08 上传

2020-11-27 上传

2020-11-29 上传

2020-12-13 上传

2020-11-28 上传

2020-12-06 上传

2020-11-09 上传

2020-12-13 上传

2020-11-24 上传

weixin_38683848

- 粉丝: 4

- 资源: 950

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新