DC逻辑综合操作指南

需积分: 47 95 浏览量

更新于2024-08-30

收藏 259KB PDF 举报

"DC逻辑综合使用流程.pdf"

在VLSI设计中,逻辑综合是一个至关重要的步骤,它将设计者用高级语言(如Verilog或VHDL)编写的硬件描述转化为门级网表,为后续的布局布线阶段提供基础。DC(Design Compiler)是一款由Synopsys公司开发的业界广泛使用的逻辑综合工具。本文档详细介绍了如何使用DC进行逻辑综合的流程。

1. 启动软件

启动DC的最常见方式是在终端中输入命令`design_vision`,这将打开其图形用户界面(GUI)。在这个界面中,用户可以通过菜单、对话框以及命令行执行各种操作。

2. 指定相关库文件及路径

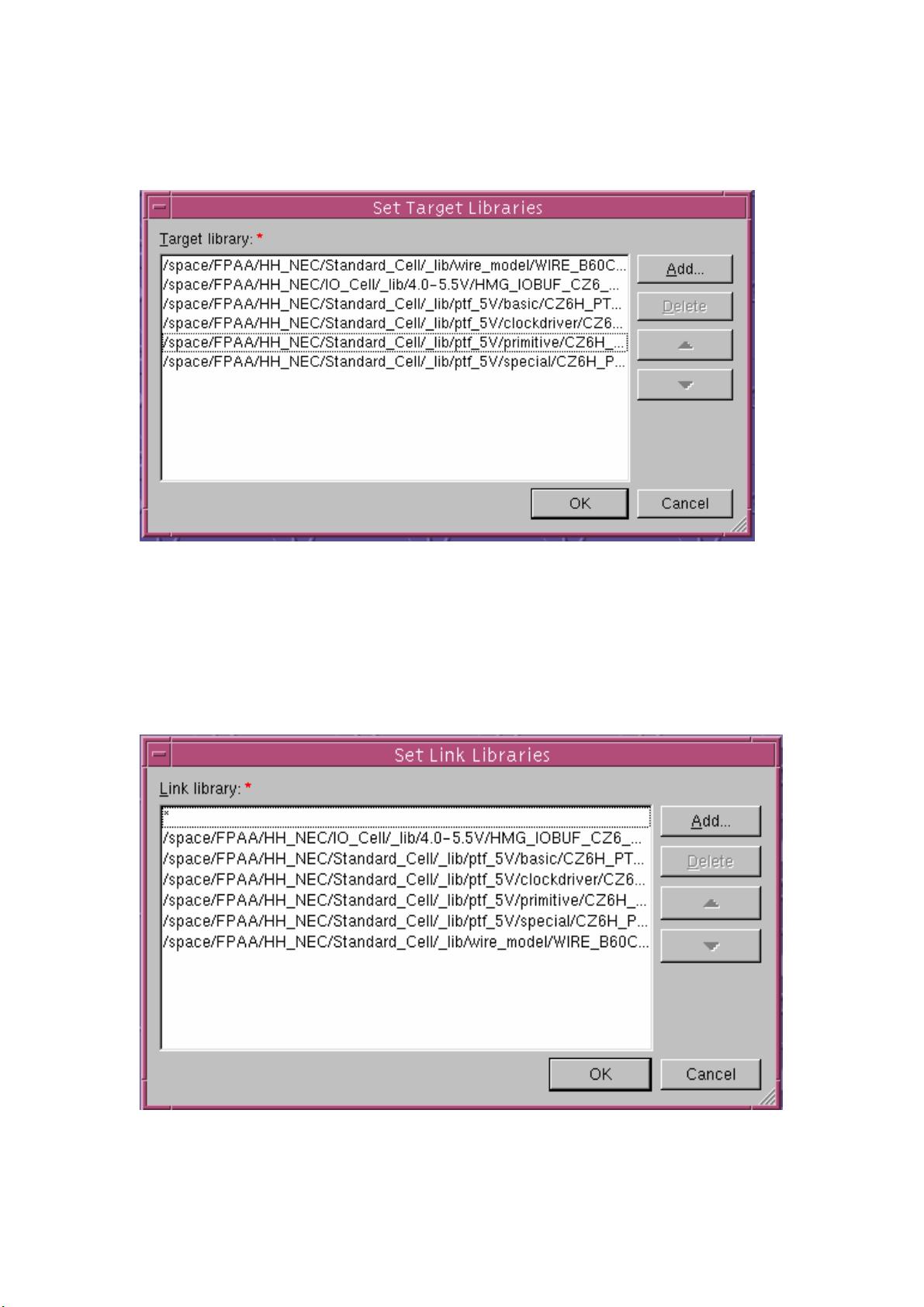

在开始综合之前,必须指定设计所需的库文件和搜索路径。在“File”菜单中选择“Setup”,然后在“Search_path”中添加库文件的路径。目标库(Target_library)通常包含由代工厂提供的库文件(*.db),这些文件包含了不同工艺下的晶体管模型。链接库(Link_library)通常与目标库相同,而符号库(Symbol_library)则是*.sdb文件,用于表示设计中的单元符号。

3. 设计读入

使用“File”菜单的“Read”功能读入设计文件。在读入后,需要明确指定设计的顶层模块名称,以便DC知道从何处开始综合。设计的层次结构可以在GUI的左侧窗口中查看。

4. 链接

设计读入之后,执行“File>LinkDesign”来链接设计。链接过程将合并所有引用的模块并创建一个完整的内部表示。在命令框中可以看到链接过程的详细信息。

5. 实例唯一化

如果设计中存在重复的子模块实例,需要进行实例唯一化。这个过程是必要的,因为DC可能会为每个实例采用不同的电路实现,即使它们的源代码和功能完全相同。使用“Hierarchy>Uniquify>Hierarchy”命令,点击“ok”以执行实例唯一化。勾选特定选项可以强制重命名所有实例,无论它们是否已经被唯一标识。

6. 参数化和约束设置

在综合之前,可能需要设置参数(parameters)和设计约束(constraints)。参数化允许对设计中的某些值进行动态调整,而约束则定义了设计的行为限制,例如时序要求、面积目标或功耗限制。

7. 逻辑综合

执行综合是整个流程的核心,通过“Synthesize - XST”或类似的命令开始综合。在设置好所有参数和约束后,DC将优化逻辑设计,以满足指定的目标。

8. 时序分析

综合完成后,进行时序分析(Timing Analysis)以评估设计是否满足时序要求。这通常通过“Analyze - Timing”命令完成。

9. 报告和检查

生成综合报告,包括门级网表大小、功耗和时序信息。检查报告以确保设计满足预期的性能指标。

10. 输出网表

最后,使用“File>Write”将综合结果写入网表文件(通常为.v or .sdf格式),供后续的布局布线工具使用。

DC逻辑综合的整个流程是一个迭代过程,可能需要反复进行参数调整和优化,以达到最佳的设计性能。理解并熟练掌握这些步骤对于高效的VLSI设计至关重要。

2021-10-11 上传

2020-11-30 上传

2020-12-28 上传

2022-11-15 上传

2022-07-10 上传

2022-06-20 上传

2020-12-28 上传

2021-12-25 上传

2022-09-19 上传

ppcust

- 粉丝: 38

- 资源: 725

最新资源

- 新代数控API接口实现CNC数据采集技术解析

- Java版Window任务管理器的设计与实现

- 响应式网页模板及前端源码合集:HTML、CSS、JS与H5

- 可爱贪吃蛇动画特效的Canvas实现教程

- 微信小程序婚礼邀请函教程

- SOCR UCLA WebGis修改:整合世界银行数据

- BUPT计网课程设计:实现具有中继转发功能的DNS服务器

- C# Winform记事本工具开发教程与功能介绍

- 移动端自适应H5网页模板与前端源码包

- Logadm日志管理工具:创建与删除日志条目的详细指南

- 双日记微信小程序开源项目-百度地图集成

- ThreeJS天空盒素材集锦 35+ 优质效果

- 百度地图Java源码深度解析:GoogleDapper中文翻译与应用

- Linux系统调查工具:BashScripts脚本集合

- Kubernetes v1.20 完整二进制安装指南与脚本

- 百度地图开发java源码-KSYMediaPlayerKit_Android库更新与使用说明