基于FIR滤波器的数字幅频均衡功率放大器设计

需积分: 9 199 浏览量

更新于2024-09-12

1

收藏 277KB PDF 举报

数字幅频功率放大器设计报告

一、数字幅频均衡方案

在数字幅频功率放大器的设计中,选择了FIR滤波器作为数字幅频均衡方案。FIR滤波器的设计方法有多种,频域采样的设计方法可对局部频谱进行整形,适合幅频均衡的应用。FIR滤波器的优点在于它具有线性相位,不存在相位失真。

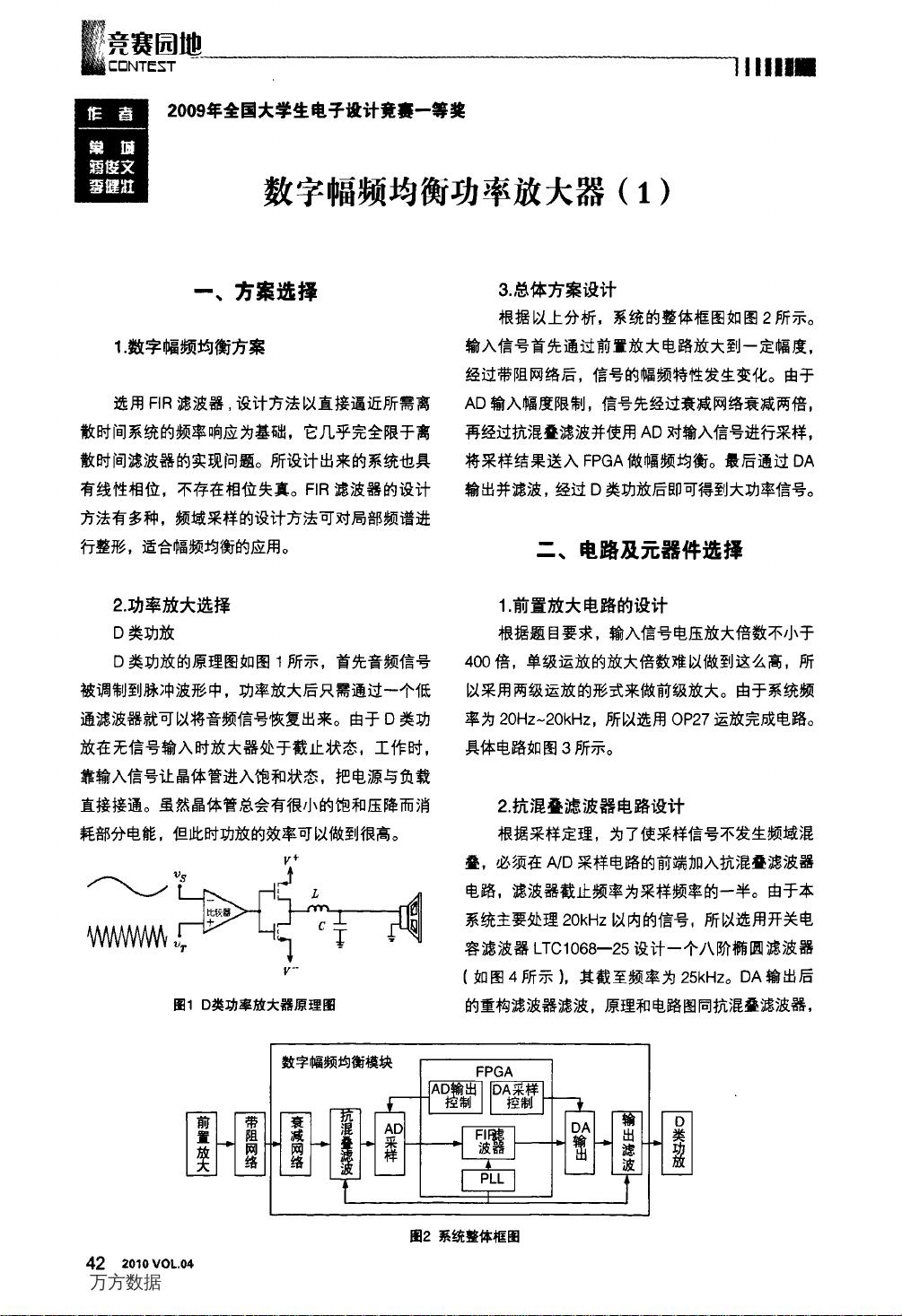

二、系统整体框图设计

根据以上分析,系统的整体框图如图2所示。输入信号首先通过前置放大电路放大到一定幅度。经过带阻网络后,信号的幅频特性发生变化。由于AD输入幅度限制,信号先经过衰减网络衰减两倍。再经过抗混叠滤波并使用AD对输入信号进行采样。将采样结果送入FPGA做幅频均衡。最后通过DA输出并滤波,经过D类功放后即可得到大功率信号。

三、电路及元器件选择

1.前置放大电路的设计

根据题目要求,输入信号电压放大倍数不小于400倍,单级运放的放大倍数难以做到这么高,所以采用两级运放的形式来做前级放大。由于系统频率为20Hz-20kHz,所以选用OP27运放完成电路。具体电路如图3所示。

2.抗混叠滤波器电路设计

根据采样定理,为了使采样信号不发生频域混叠,必须在A/D采样电路的前端加入抗混叠滤波器电路。滤波器截止频率为采样频率的一半。由于本系统主要处理20kHz以内的信号,所以选用开关电容滤波器LTC1068-25设计一个八阶椭圆滤波器(如图4所示),其截至频率为25kHz。DA输出后的重构滤波器滤波,原理和电路图同抗混叠滤波器。

四、关键技术点

1.数字幅频均衡技术

数字幅频均衡技术是指通过数字信号处理技术来实现幅频均衡的方法。这种方法可以实时地对信号进行处理,并且可以根据实际情况进行调整。

2.FIR滤波器设计

FIR滤波器设计是数字幅频均衡技术的核心部分。FIR滤波器可以实现线性相位,不存在相位失真,并且可以对局部频谱进行整形,适合幅频均衡的应用。

3.抗混叠滤波器设计

抗混叠滤波器设计是为了防止采样信号发生频域混叠。这种滤波器可以将采样频率限制在一定范围内,从而防止信号混叠。

四、小结

数字幅频功率放大器设计报告中,我们设计了一种数字幅频均衡方案,使用FIR滤波器来实现幅频均衡,并选用OP27运放和LTC1068-25滤波器来完成电路设计。这种设计可以实时地对信号进行处理,并且可以根据实际情况进行调整。

2021-05-11 上传

2010-06-14 上传

2024-11-02 上传

2024-10-26 上传

2023-11-07 上传

2024-11-02 上传

2024-11-07 上传

2023-06-13 上传

yha543

- 粉丝: 0

- 资源: 1

最新资源

- iirc:IRC服务器,如果我没记错的话

- Environment-Friend:一个旨在向大众传播废物管理意识的网站。 与与用户交互的聊天机器人集成

- bitbucket-companion-crx插件

- 笨蛋

- matlab二值化处理的代码-LAUCalTagWidget:BradAtcheson的CalTag摄像机校准方案的实时实施。这项工作得到了G

- 毕业设计&课设-基于MATLAB的FIR滤波器设计.zip

- 带C和Shell的操作系统:具有Shell和C编程的操作系统

- anti-csrf:功能齐全的反CSRF库

- pex:用于生成 .pex(Python EXecutable)文件的库和工具

- 盖斯玛斯

- Frogger_VG_Programming:一个Frogger克隆游戏机,用于练习为GAME 3150 05 SP2021进行编码@ Webster U

- ignite-challenge01

- 赫德梅塔卡普

- Check Adblocker-crx插件

- -COMP1521-计算机系统-基础知识:有关低级别系统内容的第一年课程

- 毕业设计&课设-该团队的直接模拟蒙特卡罗工作和模拟环境的脚本和数据。.zip