易灵思FPGA T85技术规格与接口详解

需积分: 10 201 浏览量

更新于2024-07-09

收藏 1.25MB PDF 举报

"易灵思FPGA T85技术手册提供了关于Efinix T85 FPGA器件的详细信息,包括其特性、封装选项、核心功能描述、接口功能描述以及电气规格等。"

Efinix T85是易灵思公司的一款FPGA(Field-Programmable Gate Array)芯片,其技术手册(T85DataSheet DST85-v1.2)涵盖了该器件的关键特性、可用封装选择、核心功能和接口功能等多个方面。以下是手册中的关键知识点:

1. **特性**:

- Efinix T85 FPGA具备一系列独特的功能,如高效能、低功耗和小尺寸封装。

- 该器件可能包含可配置的逻辑单元、嵌入式存储器、乘法器、全局时钟网络等。

2. **封装选项**:

- 手册中列出了T85的不同封装选项,这些选项影响了FPGA的物理尺寸和引脚布局,适应不同的应用需求。

3. **设备核心功能描述**:

- **XLR Cell**:这是Efinix FPGA特有的基本逻辑单元,能够实现灵活的逻辑功能。

- **Logic Cell**:这些是构成FPGA的基本逻辑构建块,用于实现用户定义的逻辑设计。

- **嵌入式内存**:T85支持内建的存储资源,可以用于缓存或其他需要高速访问数据的应用。

- **Multipliers**:内置乘法器提供硬件乘法功能,加速计算密集型任务。

4. **全局时钟网络**:

- 这部分描述了如何在FPGA内部高效地分布和同步时钟信号。

5. **设备接口功能描述**:

- **Interface Block Connectivity**:说明了FPGA如何与其他系统组件连接,如GPIO、复杂I/O缓冲器、双数据速率I/O等。

- **General-Purpose I/O Logic and Buffer**:通用I/O逻辑和缓冲器提供了灵活的输入/输出能力。

- **Complex I/O Buffer**:复杂的I/O缓冲器支持更高级别的信号处理和驱动能力。

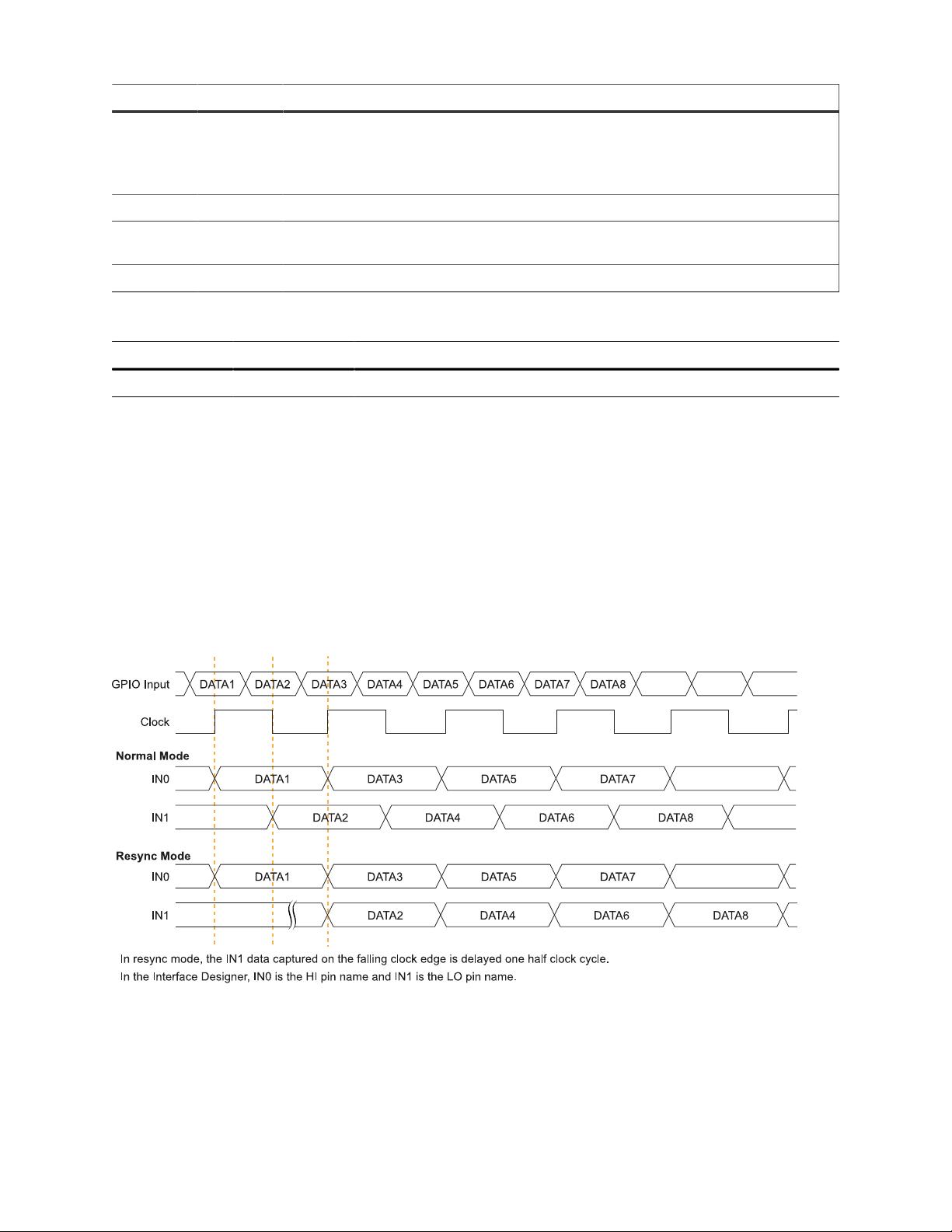

- **Double-Data Rate I/O**:双数据速率I/O允许在时钟周期的上升沿和下降沿同时传输数据,提高数据吞吐率。

- **Clock and Control Distribution Network**:时钟和控制分配网络确保在整个器件内的时钟信号和控制信号的精确分发。

6. **I/O Banks**:

- FPGA的I/O资源被组织成不同的银行,便于管理和优化资源使用。

7. **PLL (Phase-Locked Loop)**:

- PLL用于生成多个时钟信号,根据需要进行频率合成和相位调整。

8. **LVDS (Low-Voltage Differential Signaling)**:

- LVDS接口支持高速、低噪声的数据传输,包括LVDS TX和LVDS RX功能。

9. **MIPI (Mobile Industry Processor Interface)**:

- MIPI接口针对移动设备设计,包括MIPI TX和RX,以及D-PHY定时参数,用于高速串行通信。

10. **DDR SDRAM**:

- T85支持DDR SDRAM接口,允许与DDR内存进行高速数据交换,并提供了DDR接口设计师设置。

11. **电源管理**:

- 描述了电源启动顺序和电源供应电流瞬态特性,对正确电源管理至关重要。

12. **配置**:

- T85支持多种配置模式,包括静态和动态配置,以满足不同应用场景。

13. **电气规格**:

- 提供了LVDS I/O、ESD性能和MIPI电气规格及定时参数,这些对于确保器件正确运行和兼容性至关重要。

以上是对Efinix T85 FPGA技术手册主要内容的详尽概述,它为设计者提供了全面的指导,以充分利用T85 FPGA的潜力。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-12-12 上传

2019-10-15 上传

2013-01-27 上传

2013-01-29 上传

angel20041401

- 粉丝: 3

- 资源: 8

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南