XILINX_ISE 数字系统设计教程:从入门到实战

需积分: 46 71 浏览量

更新于2024-07-22

2

收藏 3.28MB PPT 举报

"XILINX_ISE_中文新教程提供了从传统到现代数字系统设计流程的详细讲解,结合XILINX ISE 13.1集成开发环境,介绍了如何使用VHDL语言进行FPGA设计。教程涵盖工程建立、设计输入、功能级仿真、逻辑综合、时序仿真、系统调试与验证等步骤,并通过实例演示了分频器和计数器的设计过程。"

XILINX ISE是Xilinx公司提供的一个集成开发环境,主要用于FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)的设计、综合、仿真以及实现。这个中文新教程旨在帮助学习者掌握现代数字系统的设计方法,特别是利用VHDL语言和ISE工具进行硬件描述。

在传统数字系统设计流程中,设计师通常从设计目标出发,手动构建真值表,简化卡诺图以获得最简逻辑表达式,然后用LSI(Large Scale Integration)电路实现这些表达式。设计完成后,需要通过调试和验证确保系统的正确性。然而,这种方法效率较低,依赖于人工操作。

现代数字系统设计流程则更倾向于自动化。设计输入后,通过功能级仿真检查逻辑功能是否正确。接下来,逻辑综合工具会将高级语言描述转化为门级网表,时序仿真进一步验证时序性能。经过映射、适配、布局和布线等步骤,最终完成设计的硬件实现。

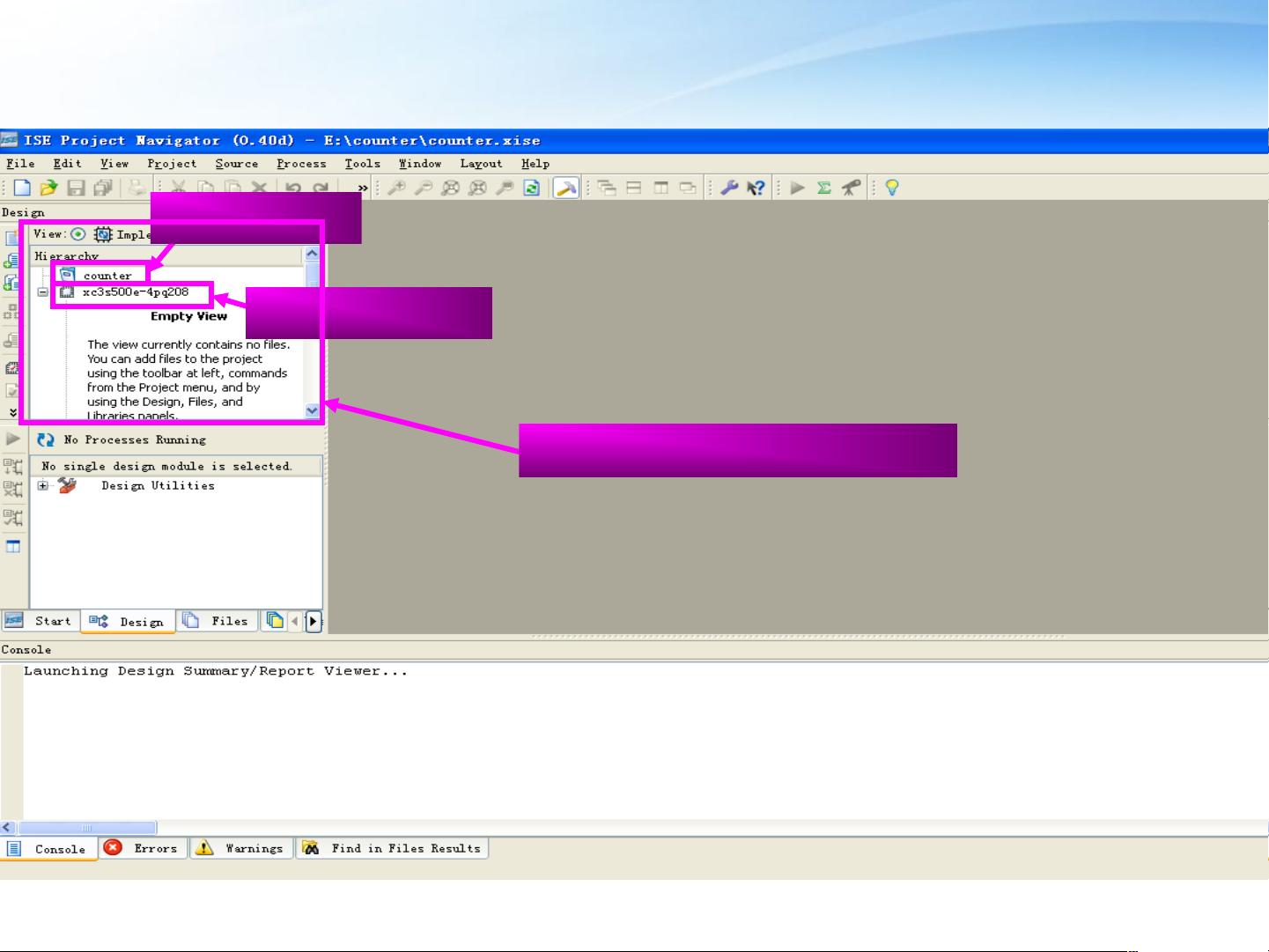

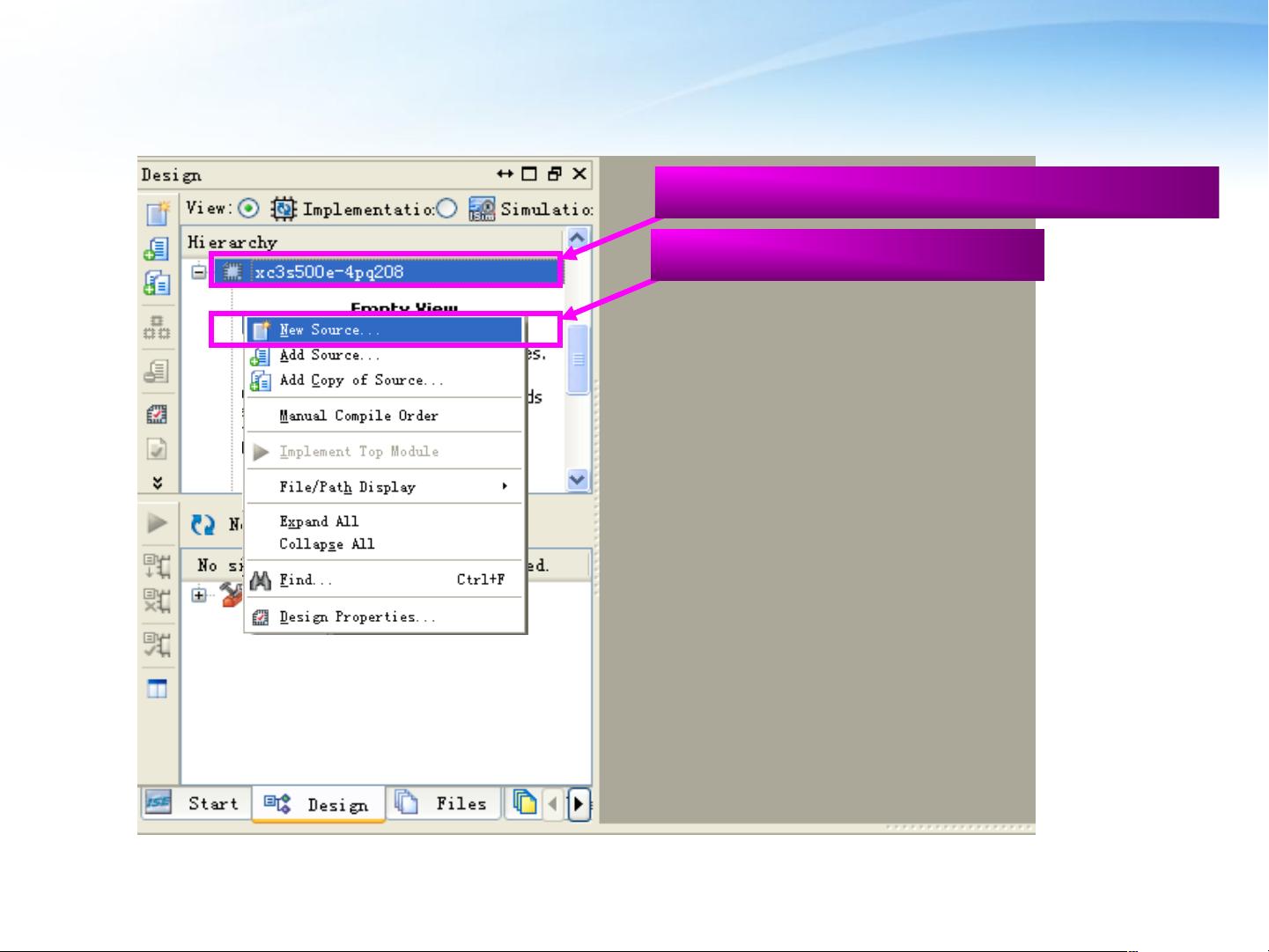

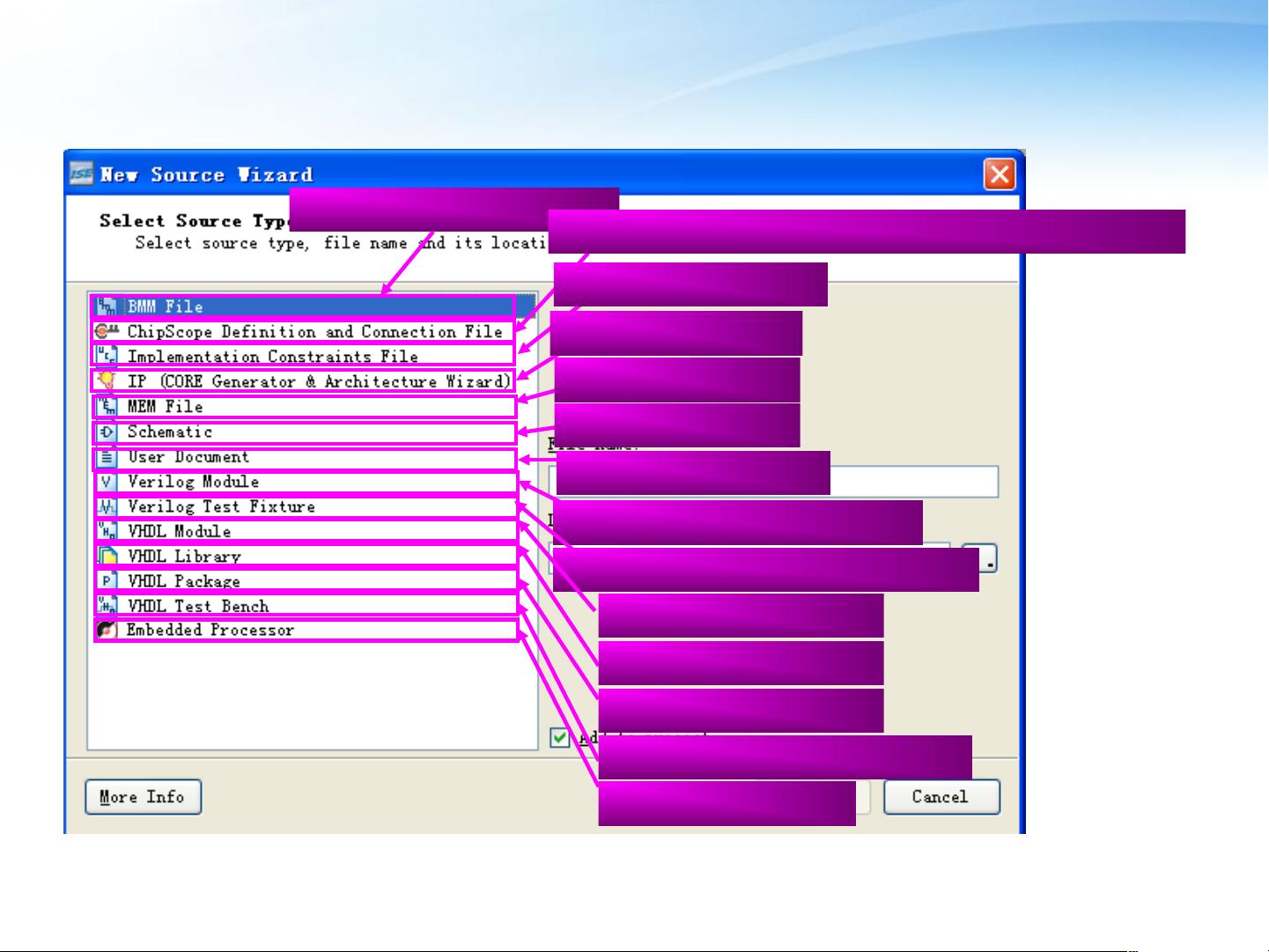

教程以ISE 13.1为例,展示了如何创建工程、选择器件、编写VHDL代码。例如,创建一个名为"counter"的工程,指定产品分类、芯片系列、型号、封装和速度等级,并选择VHDL作为设计语言。接着,教程详细解释了如何设计一个分频器和三位计数器,包括编写VHDL代码、综合、仿真、添加用户约束、实现布局布线,以及生成PROM文件并下载到PROM或FPGA中。

在基于VHDL的ISE设计流程中,一个常见的例子是设计一个接受外部50MHz时钟的分频器,生成1Hz的时钟信号,并用3位计数器驱动三个LED显示计数值。设计过程涉及VHDL代码编写,如定义一个名为`lab1`的实体,包含输入`a`, `b`, `c`和输出`y`,并在架构中实现逻辑表达式`y <= a or (c and b)`。经过综合后的仿真可以帮助我们检查设计是否符合预期。

"XILINX_ISE_中文新教程"是学习FPGA设计和VHDL语言的一个宝贵资源,通过实际操作指导学习者熟悉现代数字系统设计的全过程,提升设计和实现技能。

210 浏览量

171 浏览量

2011-10-20 上传

2024-12-27 上传

点击了解资源详情

点击了解资源详情